热门标签

热门文章

- 1二叉树——基础知识详解

- 2vue3 - 详细引入 wangeditor 富文本编辑器及使用教程,安装引入全过程及说明(示例源码开箱即用,快速植入wangeditor 富文本编辑器到vue3项目)_vue3富文本编辑器

- 3ROS 无人机仿真系统4 —— 通过键盘控制飞行器飞行_couldn't open joystick

- 4RocketMQ安装启动教程_rocketmq启动

- 5怎么看待软件外包公司_软件外包公司怎么样

- 6一篇DCMM评估解读和补贴最全文章,建议收藏!

- 7复旦nlp实验室 nlp-beginner 任务二:基于深度学习的文本分类_复旦大学nlp 作业

- 8读取信息boot.bin和xclbin命令

- 9在 Windows 平台下安装与配置 MySQL 5.7.36之启动与关闭MySQL服务_mysql5.7怎么启动

- 10Faster:一个高效就地更新的并发键值存储_c# faster

当前位置: article > 正文

testbench仿真赋值时,为符合真实情况,时序逻辑应延迟一拍

作者:笔触狂放9 | 2024-06-01 14:43:26

赞

踩

testbench仿真赋值时,为符合真实情况,时序逻辑应延迟一拍

Testbench仿真时,时序逻辑无延迟存在无延迟赋值的情况

test代码:

module test_top( input clk, input rst_n, input a, input b, output reg c_out ); always@(posedge clk) begin if(!rst_n) c_out<=0; else if(b==1) c_out<=a; else c_out<=c_out; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

testbench代码:

下面展示一些 内联代码片。

module top_test_tb( ); reg clk; reg rst_n; reg a; reg b; wire c_out; always #10 clk=~clk; initial begin clk=0; rst_n=1; a=0; b=0; #20; a=1; #30; b=1; #100; a=0; end test_top test_top( .clk(clk), . rst_n(rst_n), .a(a), .b(b), .c_out(c_out) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

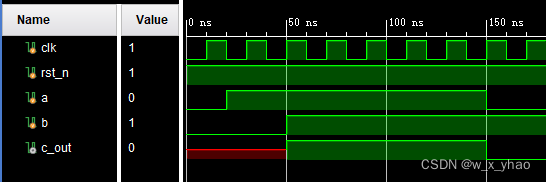

仿真波形如下:

可以看出赋值和判断语句在tb赋值后,无任何延迟,时序逻辑进行直接判断和赋值。与真实下载到板子中不同,时序逻辑应该在a,b值变化后的一拍,才能检测到a和b的值的变化。并进行判断和赋值。

应如何修改tb,保证正常的测试

tb文件中的与时序相关的赋值应同样采用时序逻辑。

三种方式:

//非阻塞赋值

@(posedge clk)

a<=1;

//或

#20;

a<=1;

//将信号与时钟上升沿错开一小段

#20.1;

a=1;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

testbench代码

module top_test( ); reg clk; reg rst_n; reg a; reg b; wire c_out; always #10 clk=~clk; initial begin clk=0; rst_n=1; a=0; b=0; #20; @(posedge clk) a<=1; #30; @(posedge clk) b<=1; #100; @(posedge clk) a<=0; end test_top test_top( .clk(clk), . rst_n(rst_n), .a(a), .b(b), .c_out(c_out) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

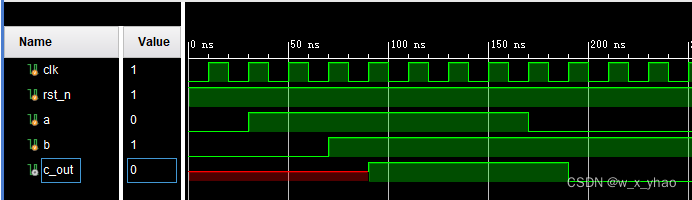

修改后的仿真结果正常了:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/658134

推荐阅读

相关标签