- 1View.onDraw(Canvas canvas)的使用_android 在 rootview canvas

- 2Azure基础:Azure ExpressRoute 知识介绍(20)_expressroute和本地网络

- 3智慧城市中的数据力量:大数据与AI的应用

- 4python/opencv 读取,写入和显示视频_cv2使用什么渲染视频

- 5fast-livo运行及报错解决办法_query livox lidar fw type failed

- 6tomcat整体架构解析

- 7机器学习(1): 线性回归——最小二乘法 小结_线性回归 最小二乘法

- 8Docker的资源配额_docker cpu分配

- 9leetcode刷题(javaScript)——数组相关场景题总结_给定一个由正整数数组,请按以下规则处理,使得数组有序(递增或者递减,不一定要严格

- 10【吐血整理】信息素养大赛分析(附报名攻略)_全国青少年信息素养大赛算法创意实践初赛

Modelsim 使用教程(1)——概述_modelsim 如何重新design

赞

踩

目录

三、基本仿真流程(Basic simulation flow)

3.1 创建工作库(create a working library)

3.2 编译设计(Compiling Your Design)

3.3 加载仿真器并运行(Loading the Simulator with Your Design and Running the Simulation)

3.4 调试结果(Debugging Your Results)

一、概述

Modelsim 是一款对于VHDL, Verilog, SystemVerilog, SystemC以及混合语言设计的仿真验证工具。

本系列提供了ModelSim仿真环境的简要概念性概述。它主要分为五个方面:

- Design Optimizations(设计优化)

- Basic simulation flow(基本仿真流程)

二、设计优化(Design Optimizations)

在讨论基本的仿真流程之前,了解设计优化是很重要的。默认情况下,ModelSim优化会自动在所有设计上执行。这些优化旨在最大化仿真器的性能,在一些Verilog设计中,比非优化的运行产生高达10倍的改进。

然而,全局优化可能对可以查看的设计模拟结果的可见性产生影响——某些信号和过程可能不可见。如果这些信号和过程对调试设计很重要,那么可能有必要通过从特定模块中删除优化来定制仿真。

因此,对于如何最好地应用优化到设计做出明智的决定是很重要的。在ModelSim中执行全局优化的工具称为vopt。请参考ModelSim用户手册中的使用vopt优化设计章节,了解关于优化权衡和定制的完整讨论。有关命令语法和用法的详细信息,请参考参考手册中的vopt。

三、基本仿真流程(Basic simulation flow)

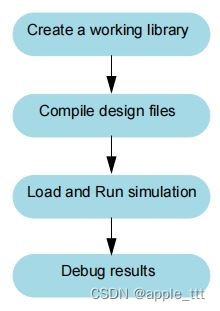

下图显示了在ModelSim中模拟设计的基本步骤。

3.1 创建工作库(create a working library)

在ModelSim中,所有的设计都被编译到一个库中。设计者通常通过创建一个称为“work”的工作库来在ModelSim中启动一个新的仿真,这是编译器使用的默认库名称,作为编译设计单元的默认目标。

3.2 编译设计(Compiling Your Design)

在创建工作库后,我们就可以在库中编译我们的设计。ModelSim库格式可以兼容所有受支持的平台。你可以在任何平台上仿真你的设计,而无需重新编译你的设计。

3.3 加载仿真器并运行(Loading the Simulator with Your Design and Running the Simulation)

在设计编译过后,通过在顶层模块(Verilog)或配置或实体/架构对(VHDL)上调用仿真器,可以用设计加载仿真器。

假设设计加载成功,则将仿真时间设置为零,并输入运行命令以开始仿真。

3.4 调试结果(Debugging Your Results)

如果没有得到预期的结果,我们可以使用ModelSim的调试环境来跟踪问题的原因。

四、项目流程(Project Flow)

HDL设计最终还是要应用于我们的项目中,尽管我们可能不需要在modelsim中使用到项目,但是它们可以简化与工具的交互,并且对于组织文件和指定仿真设置很有用。

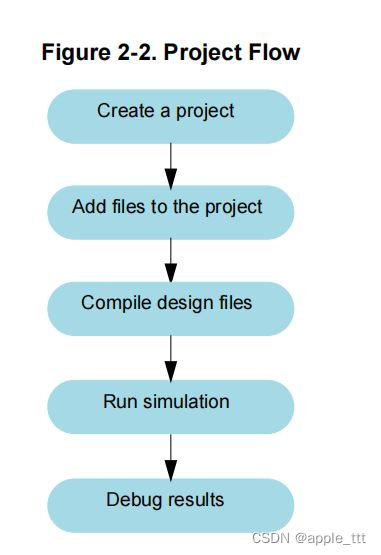

下图显示了在Modelsim项目中仿真设计的基本步骤:

如你所见,该流程与基本的仿真流程类似。然而,有两个重要的区别:

- 你不必在项目流程中创建一个工作库;它是自动为你完成的。

- 项目是持续性的。换句话说,每次调用ModelSim时,它们都会打开,除非你专门关闭它们。

五、多库流程(Multiple library flow)

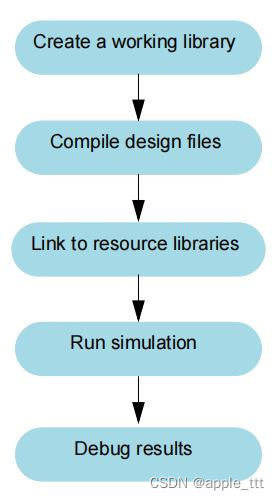

ModelSim以两种方式使用库: 1)作为一个本地工作库,其中包含你的设计的编译版本;2)作为一个资源库。工作库的内容将在您重新编译和更新设计时发生更改。资源库通常是静态的,它可以作为设计的部件源。您可以创建自己的资源库,也可以由另一个设计团队或第三方提供。

你可以指定在编译设计时将使用哪些资源库,并且有一些规则可以指定搜索它们的顺序。一个同时使用工作库和资源库的常见示例是:你的门级设计(RTL代码)和tb被编译到工作库中,设计参考的模块(例如IP)在单独的资源库中。

下图显示了使用多个库进行仿真的基本步骤:

你还可以从项目中链接到资源库。如果您正在使用一个项目,您将用以下两个步骤替换上面的第一步:创建项目,并将tb添加到项目中。

六、调试工具(Debugging Tools)

ModelSim提供了许多工具来调试和分析你的设计。随后的课程将介绍其中一些工具,包括:

- 使用项目

- 使用多个库

- 与SystemC模拟

- 设置断点并逐步浏览源代码

- 查看波形和测量时间

- 探索您的设计中的“物理”连通性

- 查看和初始化记忆

- 使用波形编辑器创建激励

- 分析仿真性能

- 测试代码覆盖范围

- 比较波形

- 使用PSL断言进行调试

- 使用系统验证日志断言和覆盖指令

- 使用SystemVerilog DPI

- 自动化仿真