- 1BERT详解(附带ELMo、GPT介绍)_bert详解(附带elm)

- 2MySQL错误-this is incompatible with sql_mode=only_full_group_by完美解决方案_this is incompatible with sql mode=only full group

- 3【DevOps】网络安全进阶之路:打造更安全、更可靠的网站

- 4数据库 | 看这一篇就够了!最全MySQL数据库知识框架!_数据库mysql

- 5信息系统项目管理师 论文、教材目录、考试大纲、考情_信息项目管理师目录

- 6【FPGA】Verilog:全减器与半减器 | Full Subtractor | Half Subtractor

- 7python学习1:安装注意事项,2024年最新字节跳动社招前端面试题_python安装注意事项

- 8【FPGA & Verilog&Modelsim】 8bitBCD码60计数器_modelsim设计8位计数器

- 9jenkins用例报告html,jenkins配置--上传代码,定时执行用例,发送测试报告

- 10(22-1)基于RAG的法律法规解析系统(Llama3+Langchain+ChromaDB):背景介绍+项目介绍_chromadb langchain

verilog学习笔记- 4)Modelsim 软件的安装、使用_modelsim安装

赞

踩

目录

Modelsim 的安装:

安装:

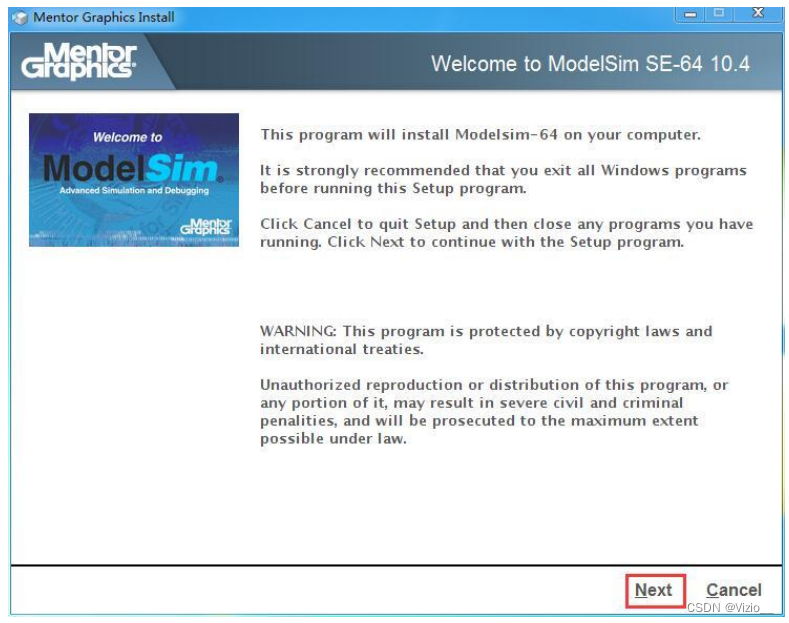

双击运行“modelsim-win64-10.4-se.exe”文件

接下来一路【Next>】

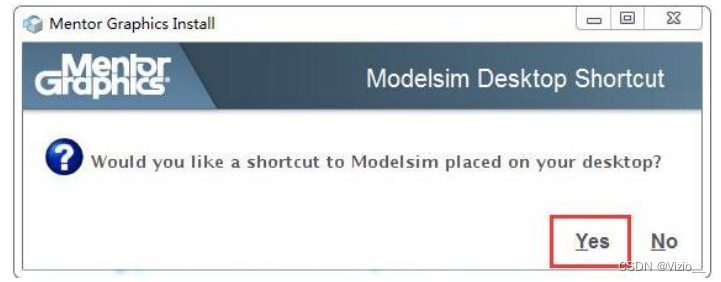

现在处于安装过程,在安装的过程中会出现两次信息提示框,第一次提示是否在桌面建立快捷方式, 点击“Yes”,如下图所示:

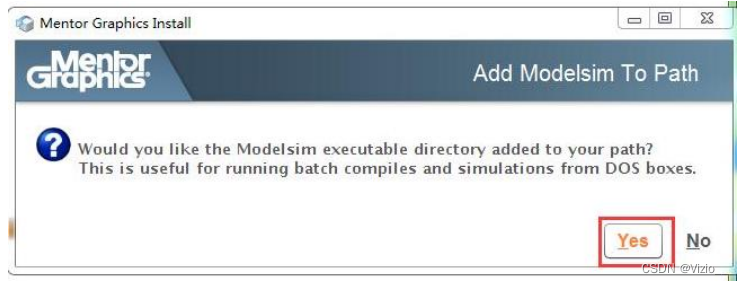

第二次提示是否将 Modelsim可执行文件放入Path 变量,选择―Yes‖时可以从DOS 提示符执行Modelsim, 这里我们选择―Yes‖,如下图所示:

Modelsim 的使用:

手动仿真:

建立 Modelsim 工程并添加仿真文件

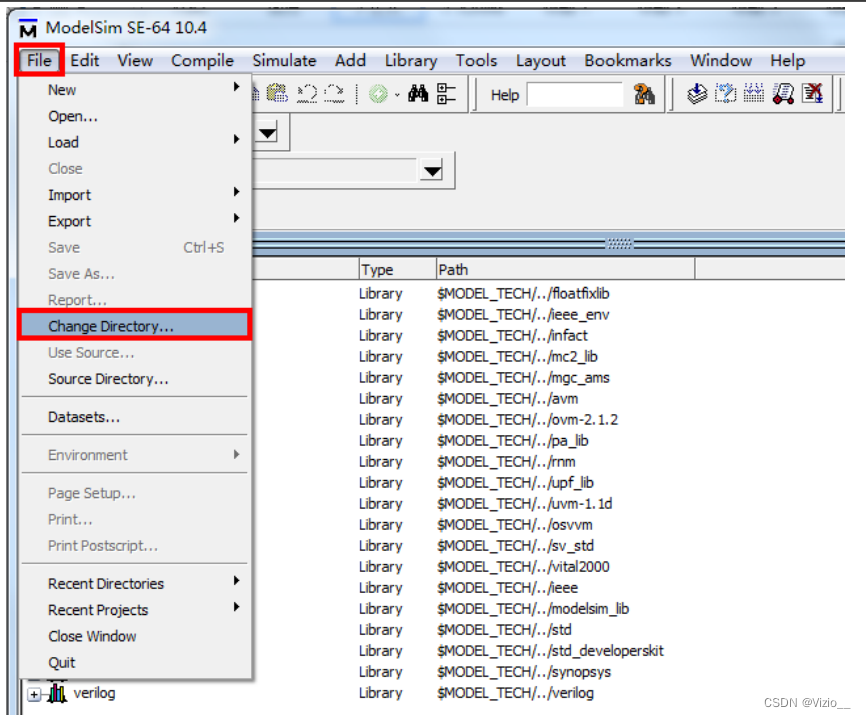

首先在 LED 流水灯的“sim”文件夹下新建文件夹“tb”,然后启动 Modelsim 软件,我们直接双击桌 面上的 Modelsim 软件图标,打开 Modelsim 软件,在 Modelsim 中选择 File->Change Directory,如下图所示:

在弹出的对话框中选择目录路径为刚才新建的 tb 文件夹。

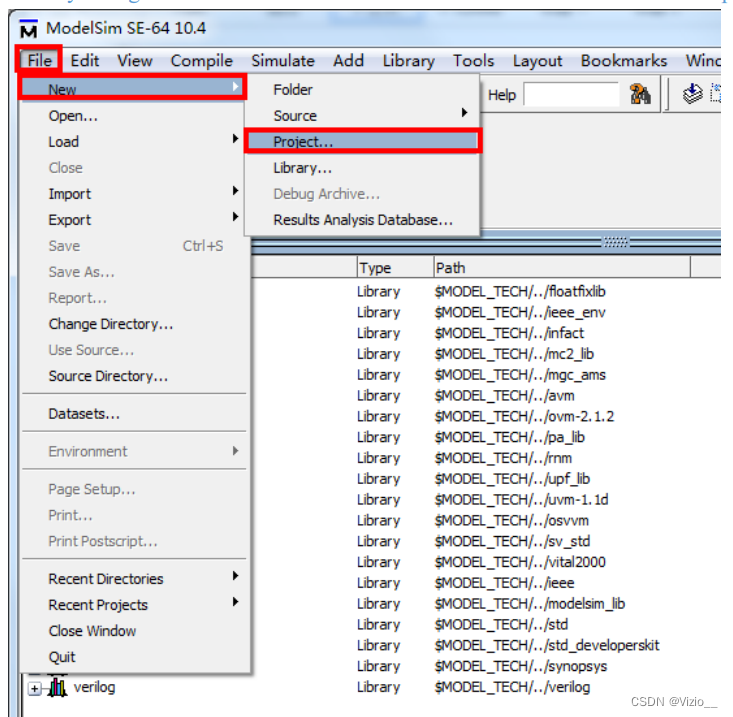

在 modelsim 中建立 project,选择 File->New->Project,如下图所示:

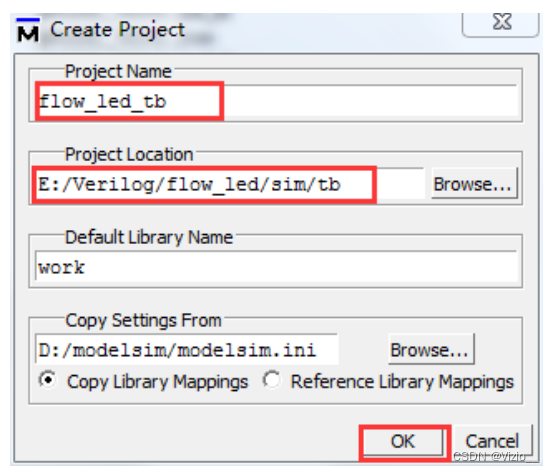

在“Project Name”栏中填写工程名,这里的命名方式,我们建议大家最好根据仿真的文件来进行命名, 时间久了,当我们记不得这个仿真工程是用来仿真什么的时候,我们看到这个工程名,就能够知道它是用 来做什么的了。这里我们把工程命名为“flow_led_tb”

“Project Location”是工程路径,可以根据需要把工程保存到不同的位置。因为前一步骤更改目录的时候已 经做了选择,所以这里保持默认即可。下面这两部分是用来设置仿真库名称和路径的,这里我们使用默认 即可。设置好工程名、工程位置,我们点击【OK】按钮,弹出如下图所示界面:

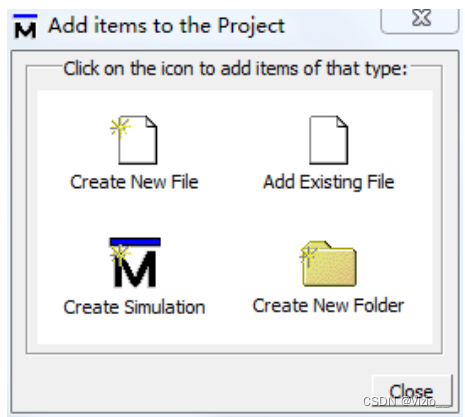

我们可以从该图的选择窗口中看出,它共有四种操作:Create New File(创建新文件)、Add Existing File (添加已有文件)、Create Simulation(创建仿真)和 Create New Folder(创建新文件夹)。这里我们先选 择“Add Existing File”(添加已有文件),如下图所示:

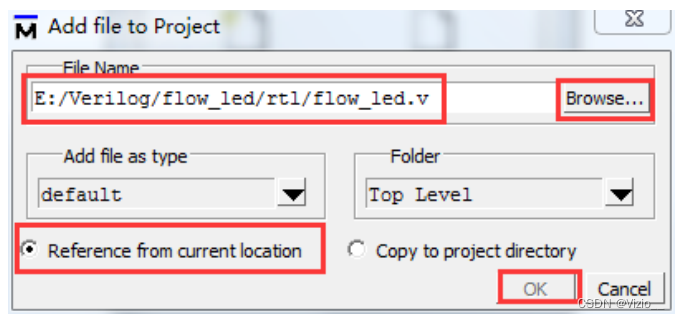

在该页面我们点击“Browse”按钮选择“flow_led.v”文件,其他的保持默认设置,最后点击【OK】按 钮。

建立 TestBench 仿真文件:

我们选择“Create New File”(创建新文件),如下图所示:

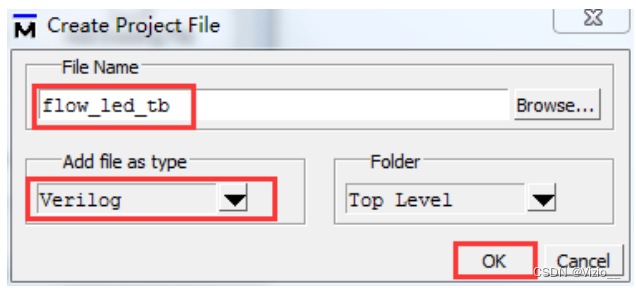

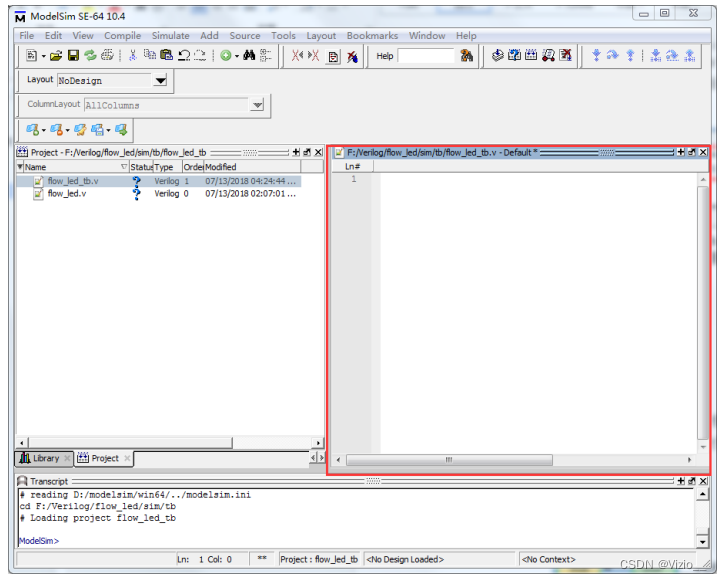

在“File Name”栏中输入文件名“flow_led_tb”,与工程名一致。―Add file as type‖栏中选择文件类型 为―Verilog‖类型,点击【OK】按钮,然后我们再关闭【Add items to the Project】对话框。此时可以看到,两个文件“flow_led.v”和―flow_led_tb.v‖添加至我们的 ModelSim 仿真工程中,如下图所示。

双击“flow_led_tb.v”文件,弹出下图所示界面:

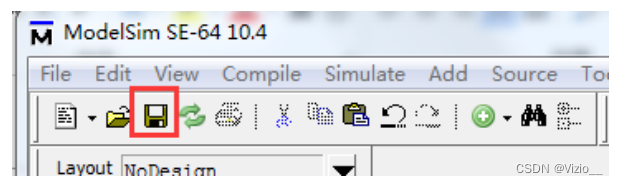

在其中编写 TestBench 仿真代码,编写完成后,单击下图所框的保存按钮

编译仿真文件:

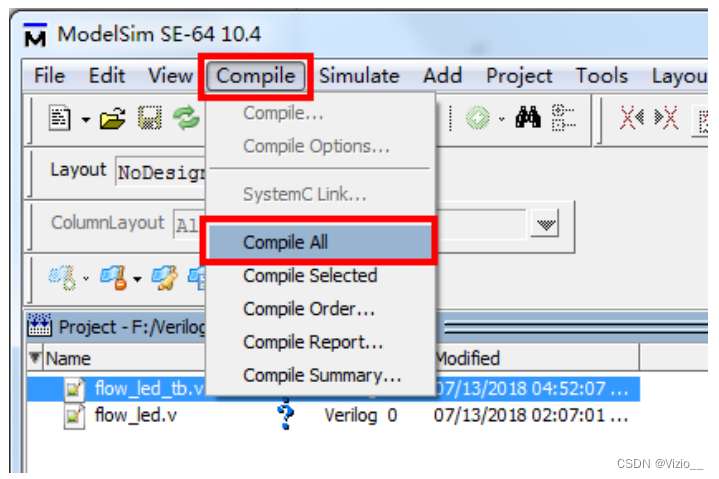

编译的方式有两种:Compile Selected(编译所选)和 Compile All(编译全部)。编译所选功能需要先 选中一个或几个文件,执行该命令可以完成对选中文件的编译;编译全部功能不需要选中文件,该命令是 按编译顺序对工程中的所有文件进行编译。我们可以在菜单栏【Compile】中找到这两个命令,也可以在快 捷工具栏或者在工作区中的右键弹出的菜单中找到这两个命令。下面我们单击 Compile All(编译全部), 如下图所示。

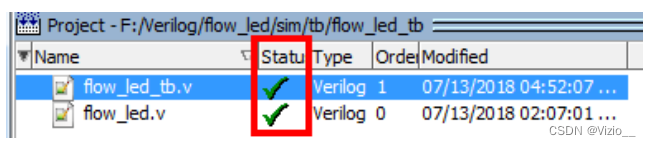

编译完成后,结果如下图所示:

文件编译后“Status”列可能会有三个不同状态。除了上图的用“√”表示的通过状态外,还有两个在 设计中不希望出现的状态:编译错误(显示红色的“×”)和包含警告的编译通过(对号的后面会出现一 个黄色的三角符号)。编译错误即 Modelsim 无法完成文件的编译工作。通常这种情况是因为被编译文件中 包含明显的语法错误,Modelsim 会识别出这些语法错误并提示使用者,使用者可根据 Modelsim 的提示信息 进行修改。编译结果中包含警告信息是一种比较特殊的状态,表示被编译的文件没有明显的语法错误,但 是可能包含一些影响最终输出结果的因素。这种状态在实际使用中较少出现,这类信息一般在功能仿真的 时候不会带来明显的影响,不过可能会在后续的综合和时序仿真中造成无法估计的错误,所以出现这种状 态时推荐读者也要根据警告信息修改代码,确保后续使用的安全性。

配置仿真环境:

编译完成后,接下来我们就开始配置仿真环境,我们在 ModelSim 菜单栏中找到【Simulate】→【Start Simulation...】菜单并点击,弹出如下右图所示页面。

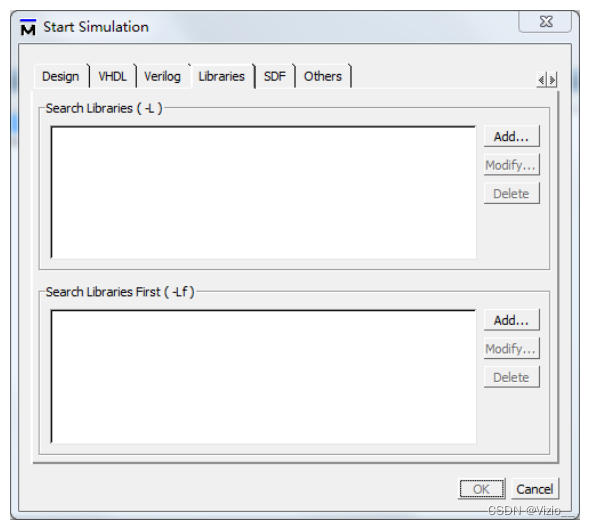

从配置仿真功能页面中我们可以看出,该页面中包含 6 个标签,分别是:Design、VHDL、Verilog、Libraries、 SDF 和 Others。对于这 6 个标签,我们用的最多的是 Design、Libraries 和 SDF 这三个标签了,下面我们就 来简单的介绍一下这 3 个标签,其余的标签我们一般用不到,这里我们就不再进行介绍了。 首先看一下 Design 标签,该标签内居中的部分是 Modelsim 中当前包含的全部库,可展开看到库中包含 的设计单元,这些库和单元是为仿真服务的,使用者可以选择需要进行仿真的设计单元开始仿真,此时被 选中的仿真单元的名字就会出现在下方的 Design Unit(s)位置。Modelsim 支持同时对多个文件进行仿真, 可以使用 Ctrl 和 Shift 键来选择多个文件,被选中的全部文件名都会出现在 Design Unit(s)区域。在 Design Unit(s)区域的右侧是 Resolution 选项,这里可以选择仿真的时间精度。在 Modelsim 进行仿真的时候,有 一个最小的时间单位,这个单位是使用者可以指定的,如最小单位是 1ns,仿真器在工作的时候按 1ns 为单 位进行仿真,对小于 1ns 发生的信号变化不予考虑或不予显示。因而这个最小时间单位也就是仿真的时间精 度。这个选项一般都是设置在默认状态,这时 Modelsim 依照仿真设计文件中指定的最小时间刻度来进行仿 真,如果设计文件中没有指定,则按 1ns 来进行仿真。最下方的区域是 Optimization 区域,可以在仿真开始 的时候使能优化。接下来我们来看一下 Libraries 标签,如下图所示。

在该标签中,我们可以设置搜索库。Search Libraries 和 Search Libraries First 的功能基本一致,唯一不 同的是 Search Libraries First 中指定的库会在指定的用户库之前被搜索。现在我们来看一下 SDF 标签,如下图所示。

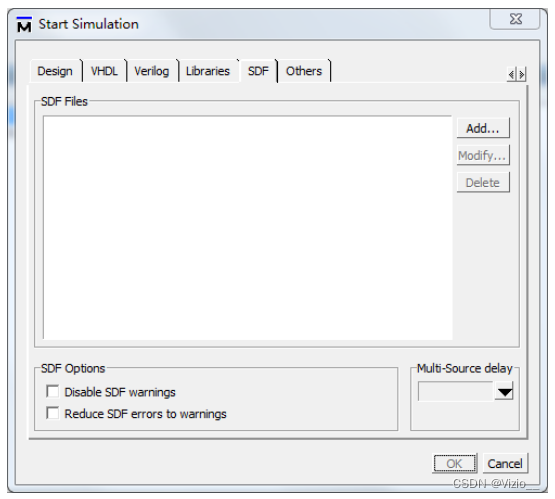

SDF 是 Standard Delay Format(标准延迟格式)的缩写,内部包含了各种延迟信息,也是用于时序仿真 的重要文件。SDF Files 区域用来添加 SDF 文件,可以选择 Add 按钮进行添加,选择 Modify 按钮进行修改, 选择 Delete 按钮删除添加的文件。

SDF Options 区域设置 SDF 文件的 warning 和 error 信息。第一个“Disable SDF warning”是禁用 SDF 警告,第二个“Reduce SDF errors to warnings”是把所有的 SDF 错误信息变成警告信息。区域 Multi-Source delay 中可以控制多个目标对同一端口的驱动,如果有多个控制信号同时控制同一个端口或互连,且每个信 号的延迟值不同,可以使用此选项统一延迟。下拉列表中可供选择的有三个选项:latest、min 和 max。latest 选项选择最后的延迟作为统一值,max 选项选择所有信号中延迟最大的值作为统一值,min 选项选择所有信号中延迟最小的值作为统一值。 至此,这三个标签我们就介绍完了,接下来我们在 Design 标签页面中选择 work 库中的 flow_led_tb 模 块,在 Optimization 一栏中取消勾选(注意一定要取消优化的勾选,否则无法观察信号波形),然后点击【OK】 就可以开始进行功能仿真了,其余标签页面中的配置我们使用默认就可以了,如下图所示。

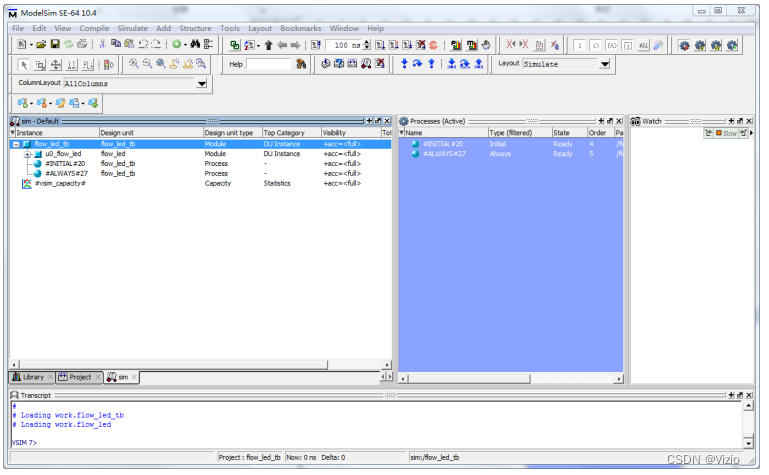

点击【OK】后弹出下图所示界面:

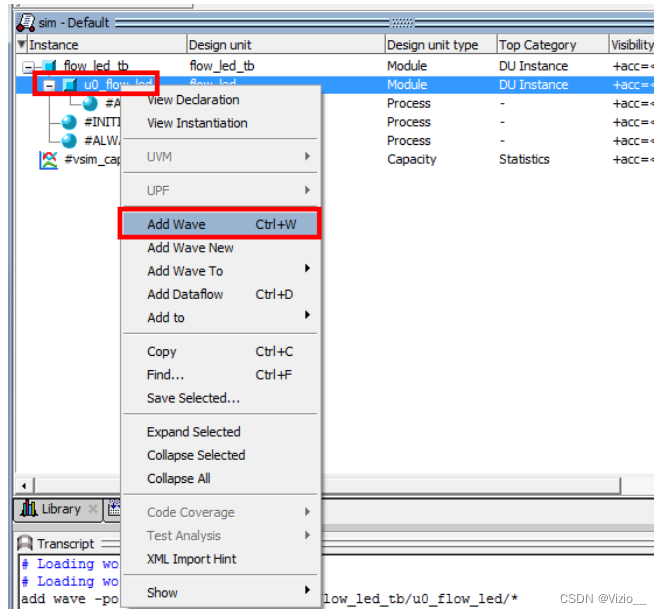

鼠标右键单击―u0_flow_led‖,选择―Add Wave‖选项,如下图所示:

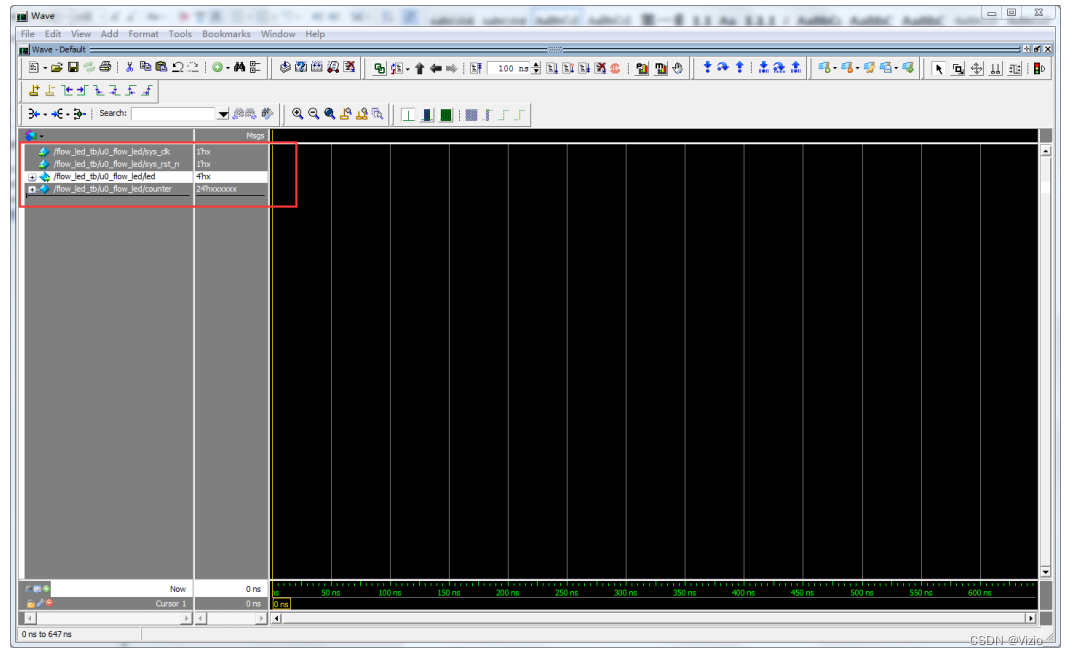

弹出下图所示界面,可以看到信号已经添加到窗口中。

我们选择仿真时间为 1ms,如下图所示,单击右边的运行按钮。

运行后的结果如下图所示:

为了方便大家更容易观察波形,我们这里将会对 ModelSim 软件中几个常用小工具进行简单的讲解。

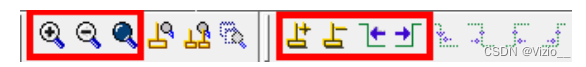

前面的几个放大镜模样的工具是放大、缩小和全局显示功能,鼠标放到图标上会显示出它们的快捷键, 后边的黄色图标是用来在波形图上添加用来标志的黄色竖线,紧跟着的是将添加的黄色竖线对齐到信号的 下降沿和上升沿。利用上述工具出来,可以看到在仿真结果中,当计时器 cnt 计到 4 时,led[0]由高电平变 低电平,计时器 cnt 计到 10 时 led[1]由低电平变成高电平,且 cnt 清零,形成了最初流水态,与预设的功能相同。

自动仿真:

所谓自动仿真,其实是在 Quartus II 中调用 ModelSim 软件来进行仿真,所以也称联合仿真。在调用过 程中,Quartus II 会帮我们完成 ModelSim 中的所有操作,我们只需要分析最后的仿真结果。

选择 EDA 仿真工具:

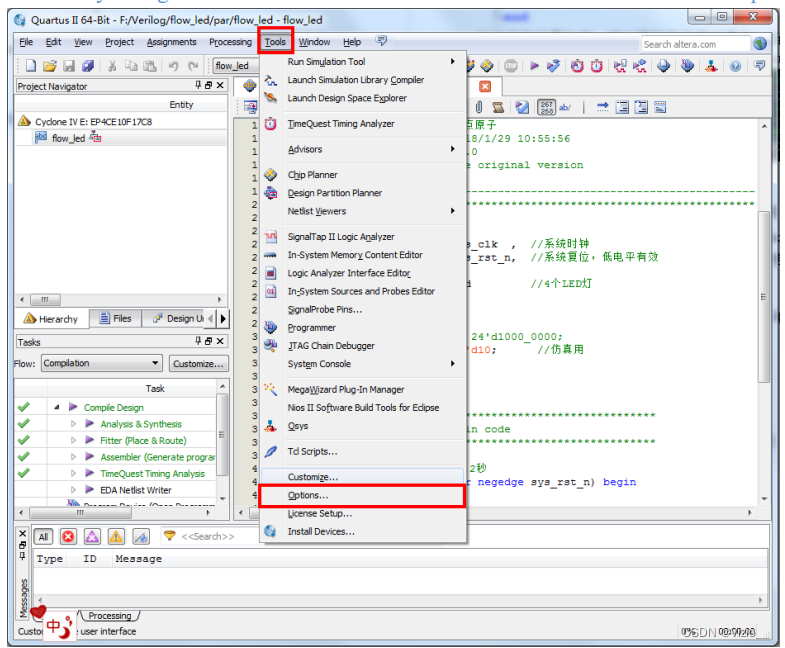

首先我们打开之前的 Quartus II 工程,在菜单栏中找到【Tool】→【Options】按钮,如下图所示:

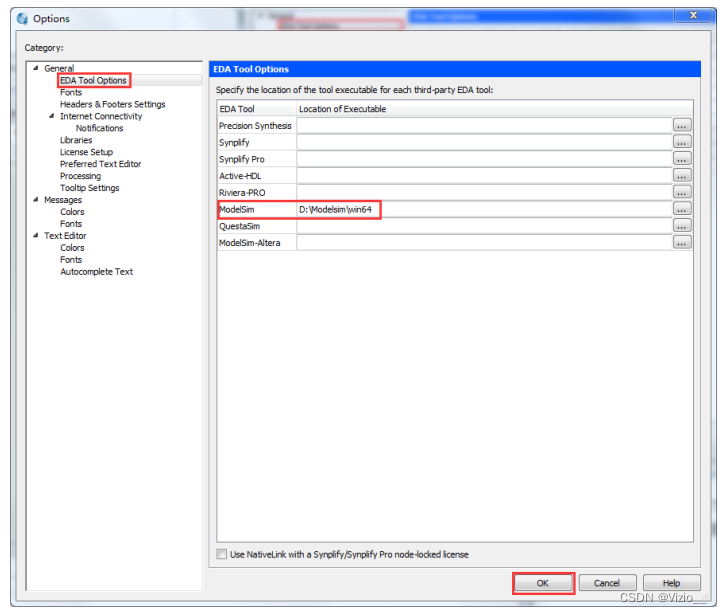

单击此按钮,在打开的页面左侧我们找到“EDA Tool Options”点击,如下图所示页面。.

在该页面中,ModelSim 这一栏,我们需要设置 ModelSim 的安装路径下的可执行文件的路径,路径设 置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。

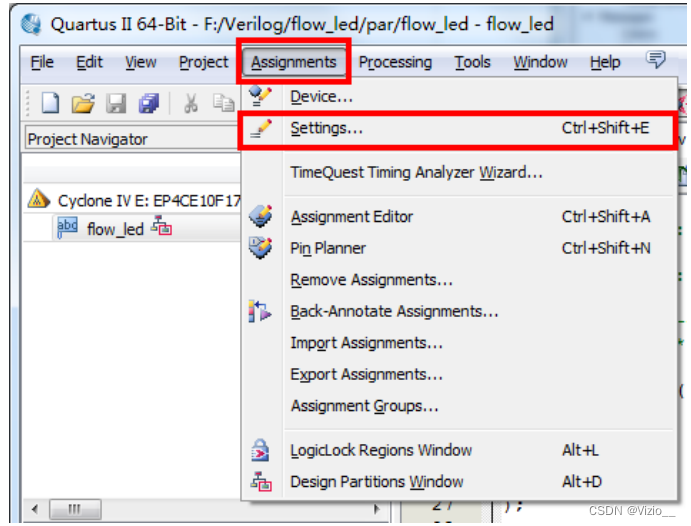

我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮,如下图所示页面。

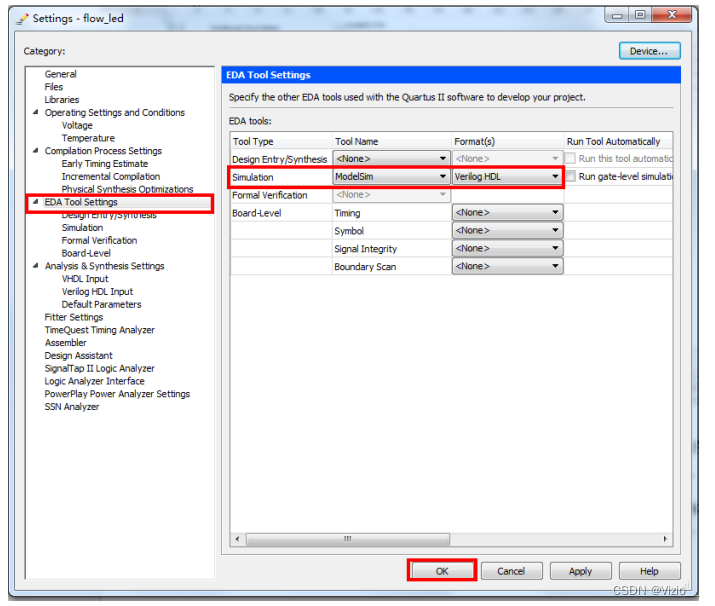

单击此按钮,在打开的页面左侧我们找到“EDA Tool Settings”点击,如下图所示页面。

我们之前创建工程的时候,由于在 Quartus II 软件中没有用到仿真,所以我们将这里设置成了“None”, 现在我们需要用到仿真工具了,我们需要在这里将“Simulation”设置成“ModelSim、Verilog HDL”。设置 完成之后,我们点击【OK】返回 Quartus II 软件页面中。

编写 TestBench:

介绍一下如何使用 Quartus II 软件生成 TestBench 模板

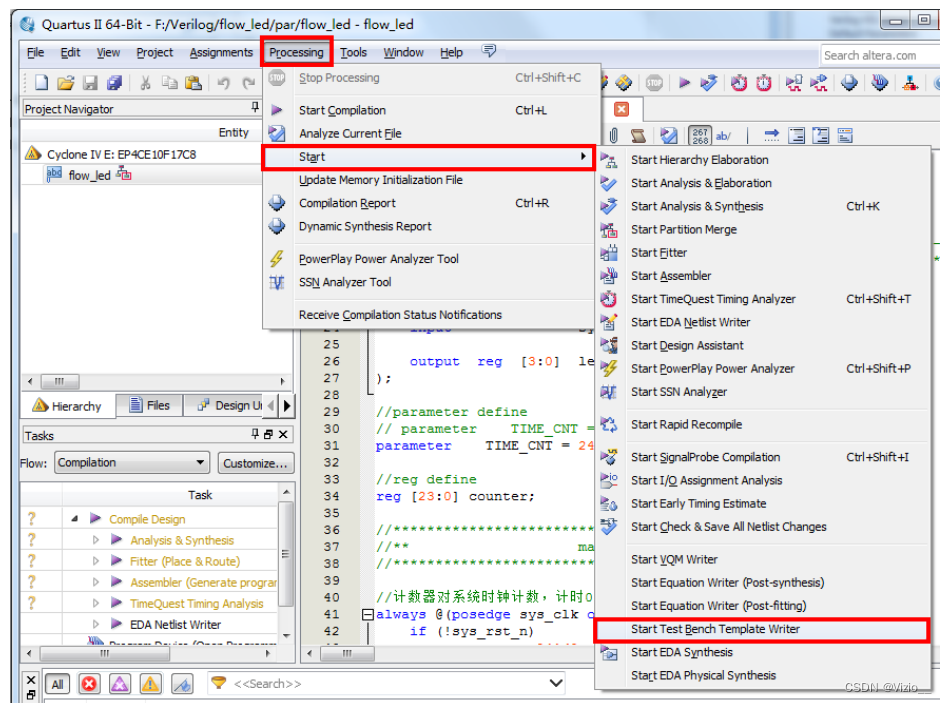

在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】 按钮,如下图所示:

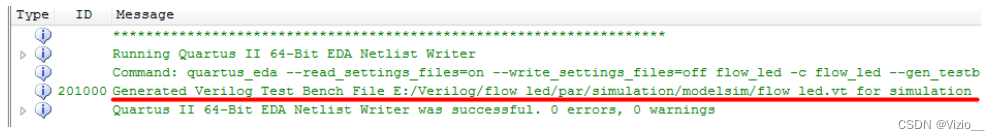

并点击该按钮,这时 Message 窗口中会显示,如下图所示:

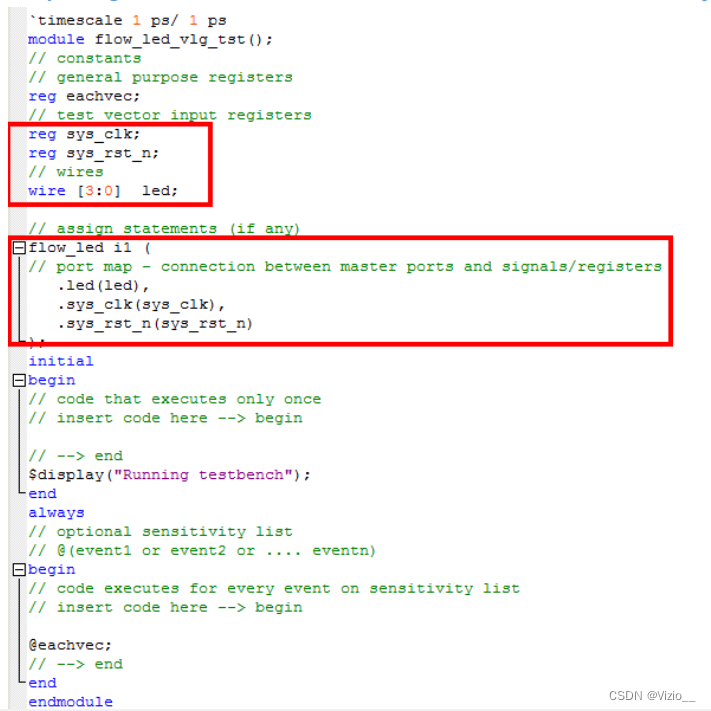

从画横线处我们可以看到 Quartus II 软件已自动给我们生成了一个 TestBench 模板并显示该模块的存放 路径,我们只需要找到这个模板并稍作修改就能直接使用了。我们在工程目录下找到“flow_led.vt”文件, 用记事本或 Quartus II 软件打开它进行修改,这里我们在 Quartus II 软件中进行,打开后如下图:

在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码、变量 的声明以及例化测试的工程等,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说 的激励)。eachvec 和@eachvec 是多余的信号,没有特殊的作用,我们可以将它删除也可以不删。修改后将其另存为 flow_led_tb.vt,以保持文件名与模块名一致。

配置仿真环境:

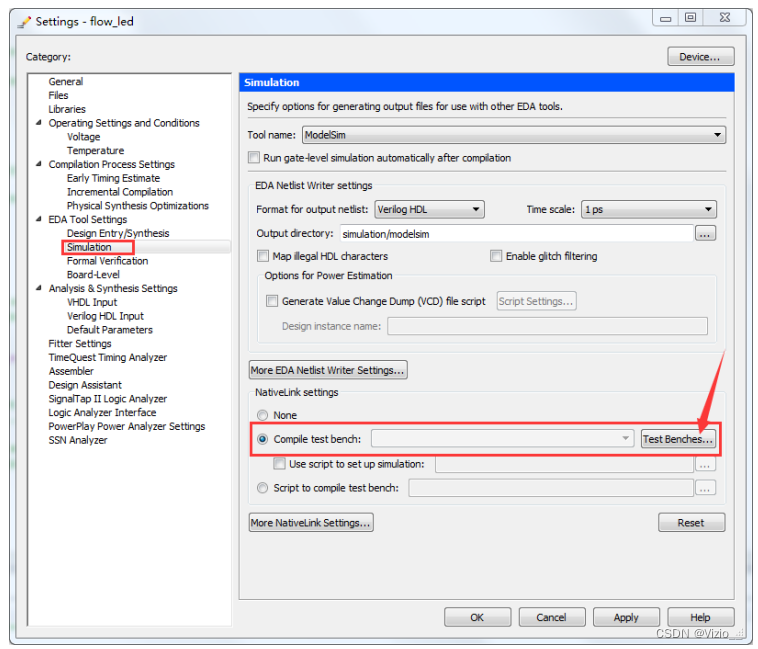

接下来我们需要在Quartus II软件中配置仿真环境,我们在Quartus II软件界面的菜单栏找到【Assigement】 →【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如下图所示的页面。

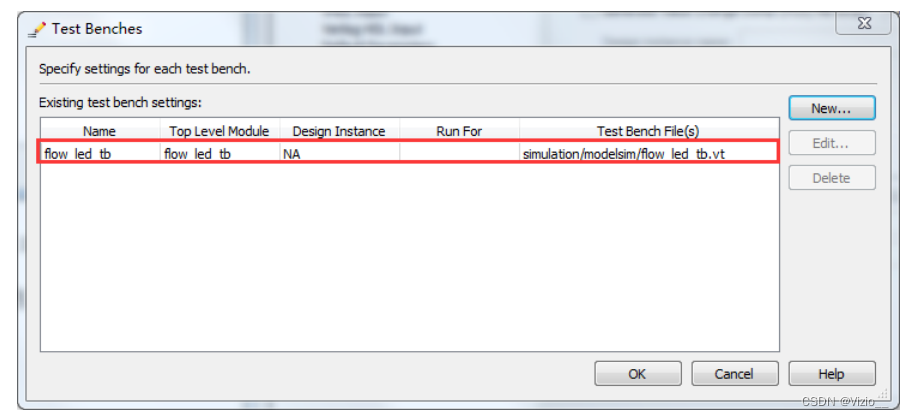

我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如下图所示的“Test Benches” 窗口:

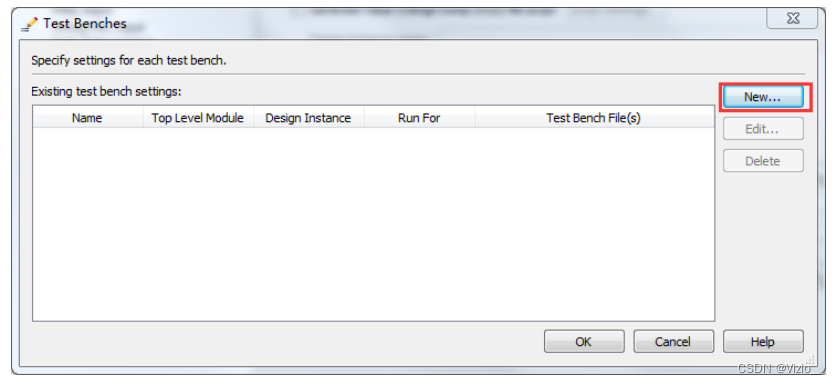

接着我们单击【New】按钮,则会出现如下图所示的“New Test Bench Settings”窗口:

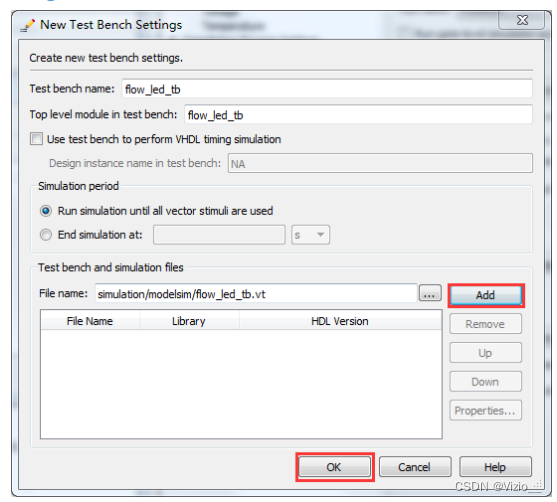

在该页面,我们将 TestBench 文件名输入到“Test bench name”,将 TestBench 顶层模块名输入到“Top level module in test bench”的编辑栏中,因为一般而言 TestBench 文件名和顶层模块名相同,所以这里只用 在“Test bench name”这一栏输入即可,软件自动同步添加“Top level module in test bench”。接着我们在 “Test bench and simulation files”列表框中添加 TestBench 仿真文件,这里我们选择 Quartus II 生成的 TestBench 模板文件―flow_led_tb.vt”。当然了,也可以选择在手动仿真节里编写的“flow_led_tb.v”文件。 添加仿真文件如下图:

然后单击【Add】按钮添加到最下面的列表中。完成后我们单击【OK】按钮,便可看到下图所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息。

然后单击【OK】按钮,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回到 Quartus II 软件界面。

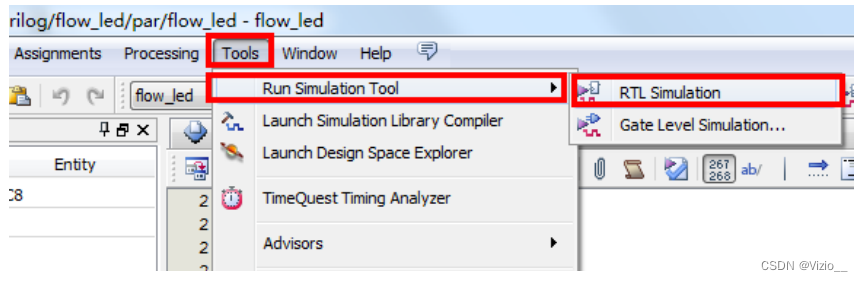

运行 RTL 仿真(功能仿真)

我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】 按钮,如下图所示界面。

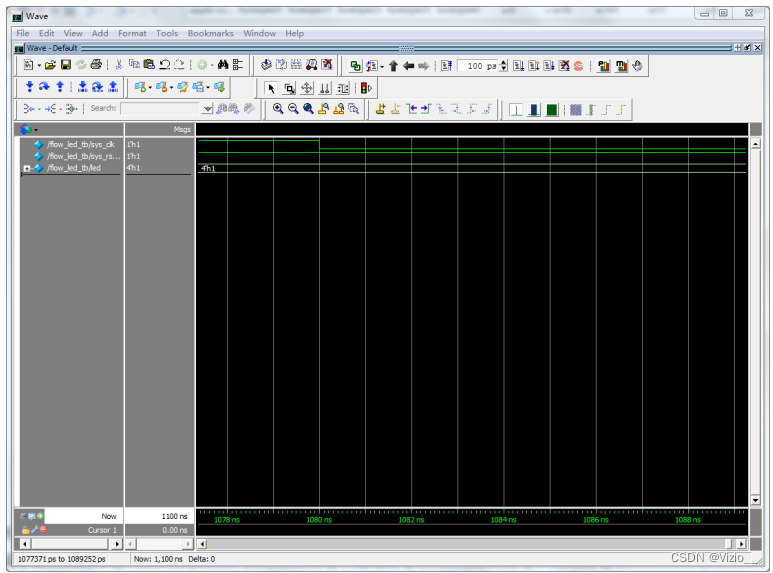

单击此按钮,则会出现如下图所示的波形图界面。

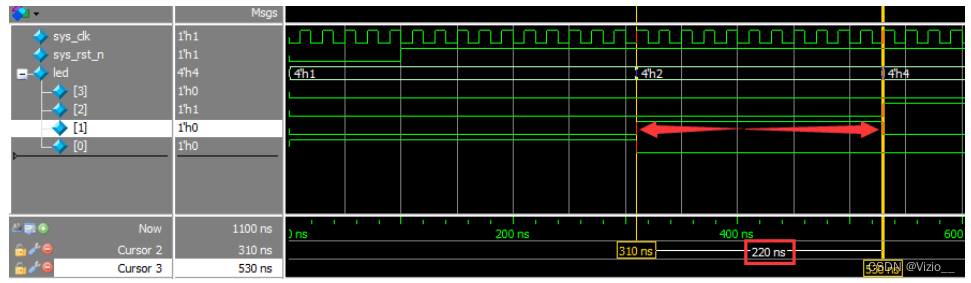

在该软件启动过程中,我们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形。从下图 可以看到在 310ns 时 led[0]由高电平变成低电平,led[1]由低电平变成高电平,形成了最初的流水态,然后 经过 220ns led[1]由高电平变成低电平,led[2]由低电平变成高电平。