- 1linux内核网络-使用协议族创建socket“每日读书“

- 2指令周期、机器周期、状态周期和振荡时钟周期(时钟周期)_一个机器周期等于几个振荡周期

- 3AdGuard Home 安装使用教程

- 4【数字IC/FPGA】UART的Verilog实现_uart verilog实现

- 5计算机语言结构和篇章,自然语言处理笔记——学习自然语言处理前所要了解的知识...

- 6校验ChatGPT 4真实性的三个经典问题:提供免费测试网站快速区分 GPT3.5 与 GPT4_chatgpt免费网站

- 7程序员35岁后的9个出路,没有送外卖的,身边人的例子。

- 8CTF刷题-汇总

- 9Vue3配置tailwindcss并在vscode中智能提示_vscode vue css提示

- 10Maven Java EE Configuration Problem:Cannot change version of project facet Dynamic Web Module to 3.1

对比GPU,使用FPGA创建神经网络_传统fpga怎么用作神经网络加速

赞

踩

介绍如何将一个具体的神经网络用于睡眠追踪,并将其映射到FPGA上。

微信搜索关注《Java学研大本营》

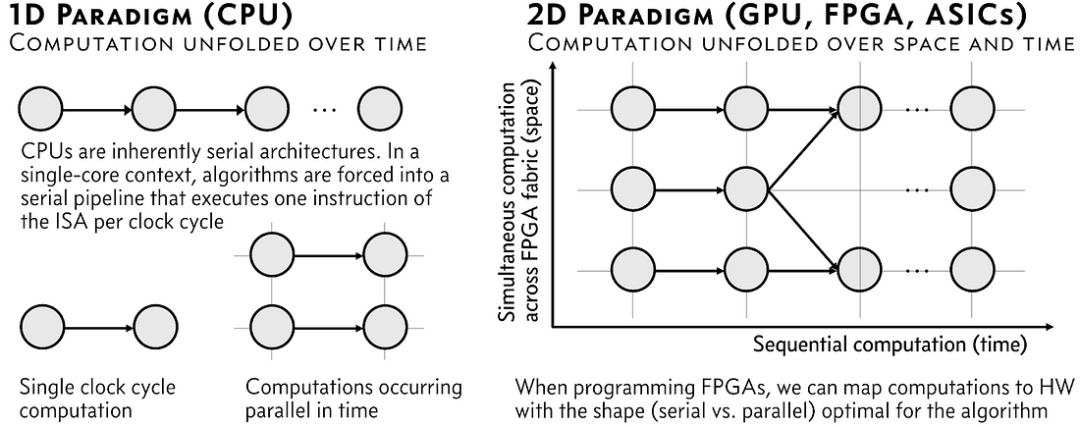

当代的CPU按照一维方式进行计算,顺序执行指令,并将算法分解为逐条加载和执行的指令。然而,未来的计算发展趋势表明,我们将越来越多地依赖硬件加速器来支持并行执行,这将成为计算的常态。这种发展趋势将统一算法和硬件结构的利用,从而实现更快、更高效的解决方案。

在这个发展趋势中,支持二维计算的GPU的崛起已经部分实现了这一趋势。GPU具备大规模并行计算的能力,使得许多原本难以并行化的应用程序性能得到大幅提升。

【左图】GPU最适合尴尬地并行处理图像处理算法。视频画面流畅。【右图】CPU的串行限制导致明显的延迟和性能不佳。

然而,GPU只能在特定情况下加速特定的算法。未来,通过互连的CPU和各种硬件加速器实现超优化将成为可能。FPGA将成为这个未来的重要组成部分,FPGA允许通过对硬件结构进行编程来实现极度定制化的二维计算。

【左图】展示了CPU如何通过串行执行逐个指令来解决问题的过程。【右图】展示了GPU、FPGA和ASIC等硬件加速器如何在空间和时间上进行二维计算。

本文为大家展示如何将一个具体的神经网络用于睡眠追踪,并将其映射到FPGA上。更重要的是演示将硬件映射到算法所需的关键工具,介绍如何实现异构计算。

1 睡眠追踪:铅笔尖上的神经网络

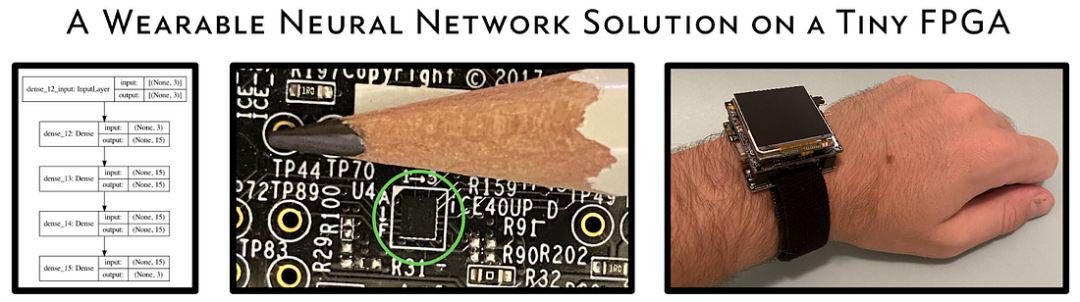

这里制作了一个基于可穿戴FPGA的睡眠追踪器。在这个过程中,建立了一个流水线,能够将最初用Python(Keras)描述的神经网络映射到硅芯片(FPGA)上。从数据采集到神经网络预测,整个睡眠追踪过程完全在一个微小的FPGA上运行,没有处理器参与。

在比铅笔尖还小的FPGA上部署了三层前馈神经网络(左图),这些FPGA可以在iCE40 Ultra Wearable Development Platform(右图中绿色圈出)中找到。

如视频所示,用户的睡眠状态直接在设备上进行分类。

,时长00:08

利用密歇根大学(Walch等人,2019年的《睡眠》期刊)开发的经过同行评审的算法实现。这是首个开源的睡眠数据集和相应的算法存储库。

使用来自该项目的有标签数据对这里的FPGA神经网络(NN)核心进行了验证。使用的神经网络是一个多层感知器,以加速度计数据、心率和昼夜节律数据作为输入,并以91.3%的整体准确率预测清醒、快速动眼(REM)睡眠和非快速动眼(non-REM)睡眠。

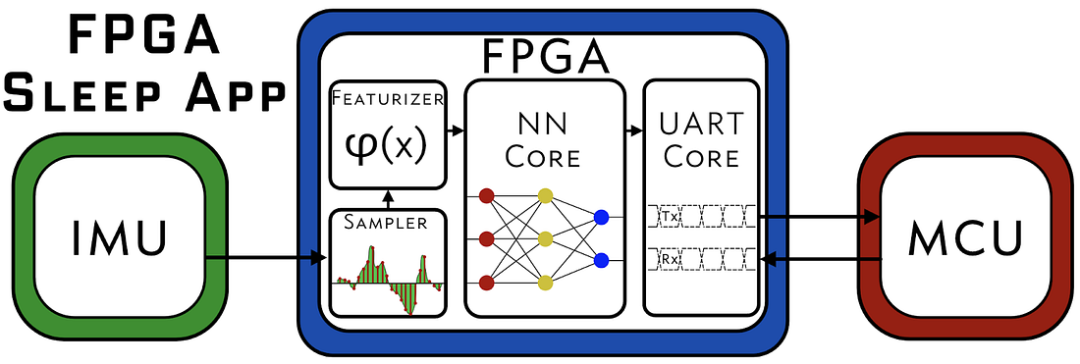

FPGA睡眠追踪器的高级架构图。在前端,STM IMU芯片是连接到FPGA的数据源。在后端,可以连接一个主机计算机来读取数据并向睡眠追踪器发送命令。从头开始使用SystemVerilog自己开发了采样器、特征提取器、NN核心和UART核心。这能够实现一个在微小FPGA上可部署的高效解决方案。

构建的参数化定义的FPGA NN核心是独立于供应商的,并且适用于超出此应用范围的其他应用,因为流水线允许在一定约束条件下轻松更新模型形状和参数。

2 可适应加速器上二维算法的未来

如今,部署可适应加速器(如FPGA)是一项高摩擦且耗时的任务。将从今天的实践和未来的改进角度描述FPGA开发的三个方面。

2.1 二维算法将以高级方式(例如Python)进行描述并自动部署

编写FPGA代码是一项神秘的任务,需要不同于数据科学家和大多数软件工程师的专业知识。对于本来可以极大受益于基于FPGA的二维加速的团队来说,这可能成为一道阻碍。能够使用熟悉的高级语言(如Python)描述针对FPGA的算法对于普及FPGA的使用至关重要。FPGA专家也将从这种基础设施带来的主要效率提升中受益。

要在应用中部署一个新的睡眠追踪器网络,用户只需运行一个脚本并轻微修改几个文件。无需具备硬件知识,也无需编写新的SystemVerilog代码。

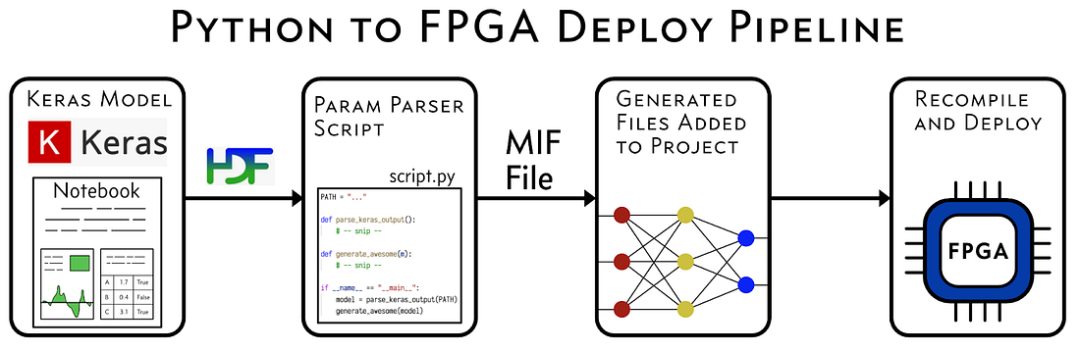

神经网络部署流程使非FPGA专家能够训练新模型并部署到FPGA上。流程的步骤包括训练和导出Keras模型,使用脚本将输出模型解析为FPGA编译器工具链所需的数据,更新顶层FPGA项目文件中的模型常量,然后重新编译FPGA比特流。

这有效的原因在于只允许使用高度约束的模型。未来,更通用的高级综合(HLS)工具,如赛灵思(Xilinx)的Vitis HLS和谷歌的XLS,将允许用户提供要部署到可适应加速器的通用高级算法描述。

2.2 将以Python等语言高效地测试和调试二维算法

仿真、验证和调试是FPGA应用设计过程中关键的部分。这些过程也将从高级接口和工具中得到重大改进。

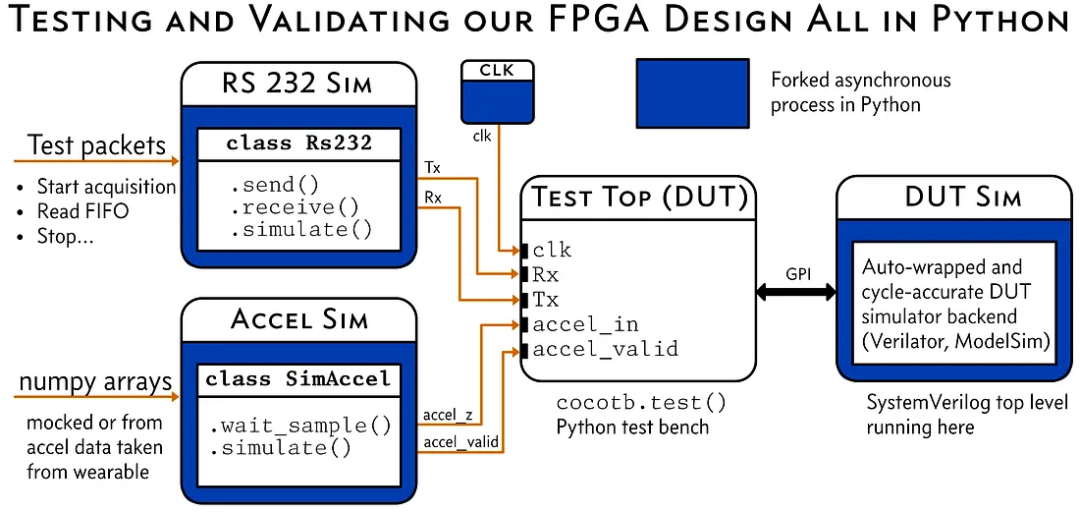

睡眠追踪器应用的顶层测试平台图。能够使用Cocotb和Python进行测试、验证和调试FPGA设计,这是一大福音。Python的异步/等待语法的便利性以及在Python中轻松模拟子组件/导入测试数据的简易性极大地加快了我们的工作。

已经取得了巨大的进展。例如,虽然直接在SystemVerilog中编写了所有组件,但在所有的离设备验证和测试平台(对每个模块和整个睡眠应用)上都使用了Cocotb,而从未离开过Python。借助Cocotb,可以在Python生态系统中使用周期精确的仿真,这对于FPGA验证非常重要,而且对开发人员非常高效。

2.3 Rust将成为连接异构系统的粘合剂

嵌入式工程师常见的情况是在硬件加速器(如FPGA)和主机CPU之间建立通信。这项工作因其繁琐和容易出错而臭名昭著。

在Rust中构建了FPGA睡眠应用程序的设备驱动程序和更高级的Session API。前者实现了自定义数据包协议,而使用后者创建了各种与FPGA睡眠应用程序交互的程序。Rust是一个很好的解决方案,因为其类型系统和静态检查使得编写安全的低级代码和符合人体工程学的高级API变得更加容易。本演讲的后半部分将详细介绍其中一些特性。

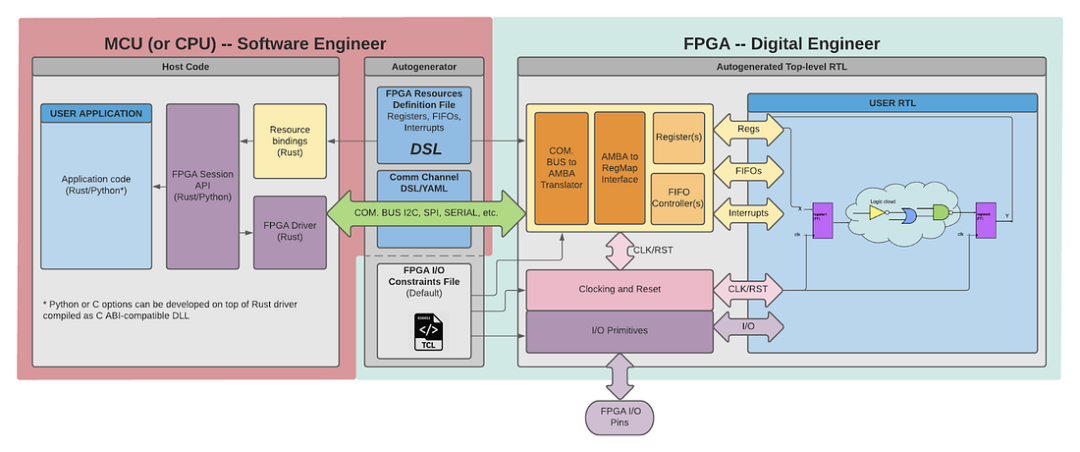

相信Rust是将异构计算系统连接在一起的最佳选择。在这个角色中,Rust将提供低级通信的安全性,减少驱动程序的脆弱性,并为算法之间跨硬件边界进行通信提供人体工程学的API。

将Rust作为CPU <-> FPGA的粘合剂的展望,包括针对常见I/O类的代码生成设施。

推荐书单

《 Vue.js 3企业级项目开发实战(微课视频版)》

本书是一本实用性很强的Vue.js 3实战项目书。书中结合实际项目场景,构建了一个完整的企业级应用。全书共分13章,内容包含项目概述、Vue3项目管理、登录管理、后台主框架、图库管理、管理员管理、用户管理、商品管理、订单管理、优惠券管理、商品评论管理、分销管理和公告管理,并且讲解了这些模块的实际应用方法。同时,本书还介绍了如何使用Vite、Axios、Vue Router、Vuex等流行工具和库,以提高开发效率、提升用户体验。

《 Vue.js 3企业级项目开发实战(微课视频版)》![]() https://item.jd.com/14140678.html

https://item.jd.com/14140678.html

精彩回顾

微信搜索关注《Java学研大本营》

访问【IT今日热榜】,发现每日技术热点