- 1MapReduce集群的安装与部署_mapreduce安装部署

- 2R语言上机例题_单位招聘2500人,按考试成绩从高到低依次录用,共有10000人报名,假设报名者的成绩

- 3Linux-解压缩文件命令(gzip、zip、unzip、tar、jar)_jar文件解压与压缩

- 4基于springboot生鲜交易商城微信小程序源码和论文

- 5【Hive---06】数据导入 与 数据导出_hive导出数据到本地

- 62024年网络安全最新网络安全学习笔记

- 7Django+uwsgi+nginx服务器部署后无法访问除首页外的其它页面_nginx django 打不开

- 8CSDN上该如何查看自己有多少积分?_csdn查看积分

- 9快速体验 Llama3 的 4 种方式,本地部署,800 tokens/s 的推理速度真的太快了!_llama 3 token就可以下各种软件输入你的token来操作了

- 10python linux运行环境,Linux平台Python运行环境配置

Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇_fpga高速收发器文档

赞

踩

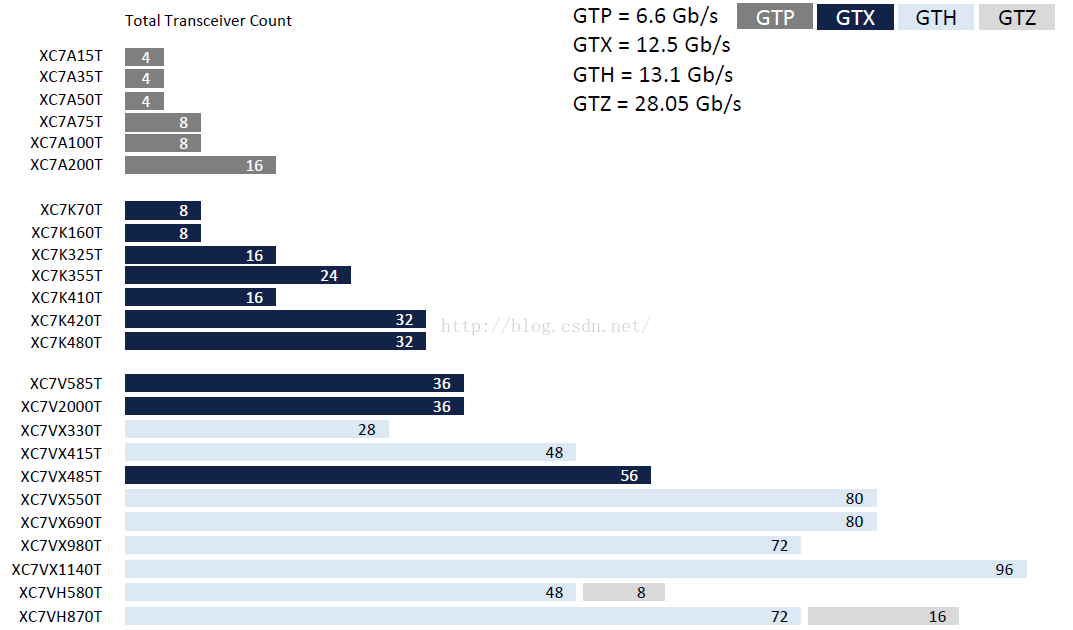

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最大的收发器数量。

图一

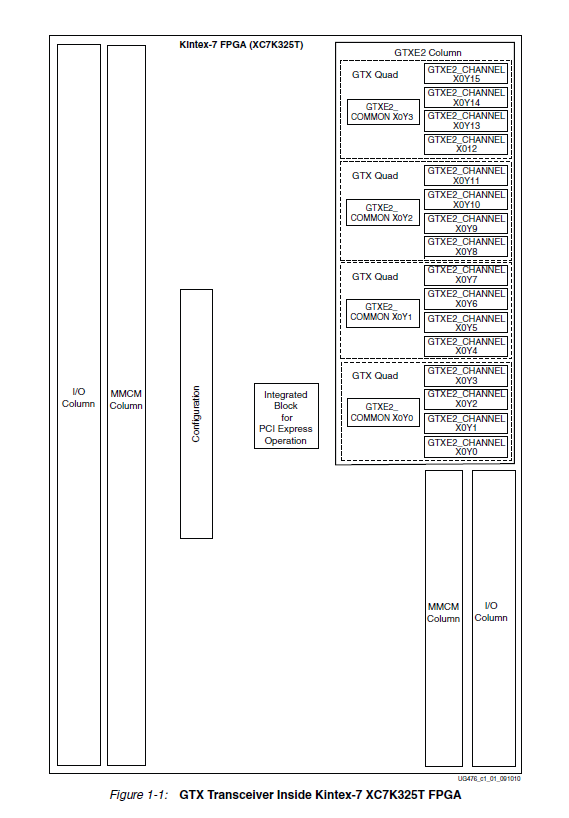

Xilinx的7系列FPGA随着集成度的提高,其高速串行收发器不再独占一个单独的参考时钟,而是以Quad来对串行高速收发器进行分组,四个串行高速收发器和一个COMMOM(QPLL)组成一个Quad,每一个串行高速收发器称为一个Channel,以XC7K325T为例,GTX在FPGA内部如图二所示:

图二

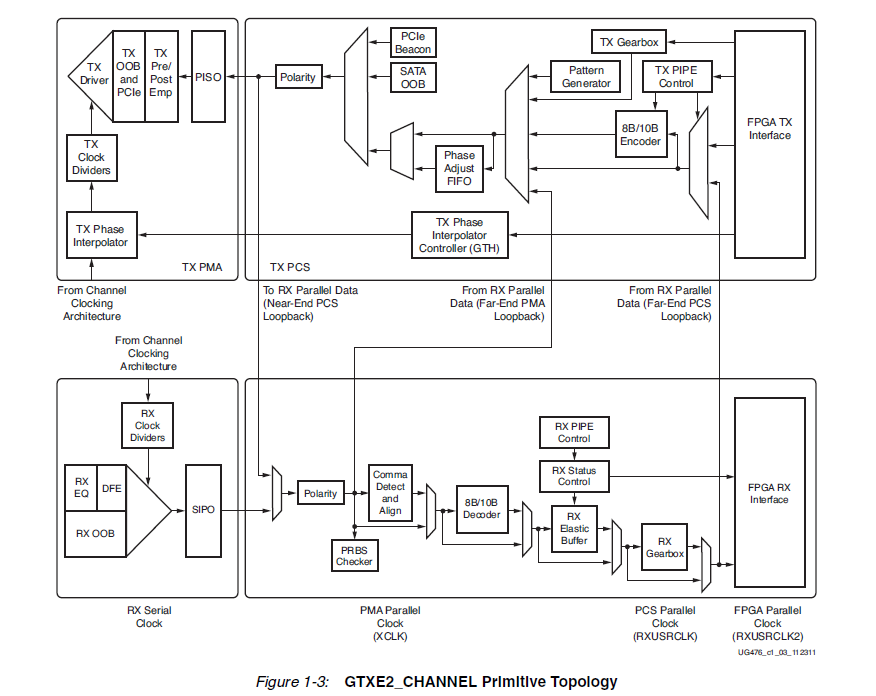

对于每一个串行高速收发器,其包含了发送部分和接收部分,内部结构图三:

图三

发送端和接收端功能独立,均由PMA(Physical Media Attachment,物理媒介适配层)和PCS(PhysicalCoding Sublayer,物理编码子层)两个子层组成。其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

GTX发送端处理流程:首先用户逻辑数据经过8B/10B编码后,进入一个发送缓存区,该缓冲区主要是PMA子层和PCS子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速Serdes进行并串转换,有必要的话,可以进行预加重、后加重。值得一提的是,如果在PCB设计时不慎将TXP和TXN差分引脚交叉连接,则可以通过极性控制来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是RX接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。

上面是GTX的性能和结构功能概述,下面详细分析GTX的时钟结构。

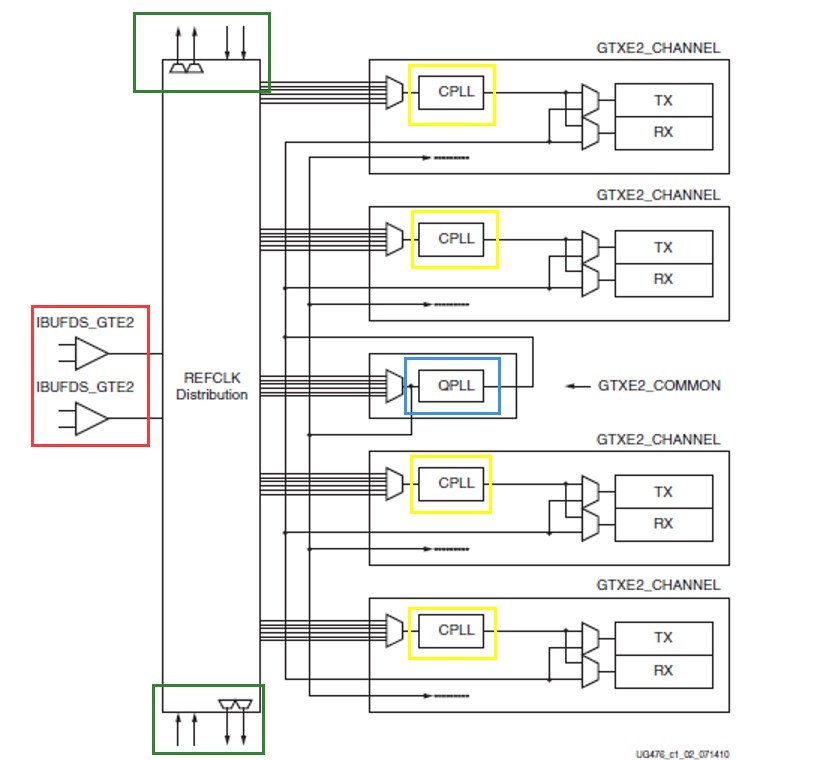

以7系列的GTX来说,每个Quad有两个外部差分参考时钟源,其中一个Quad的时钟结构如图四所示:

图四

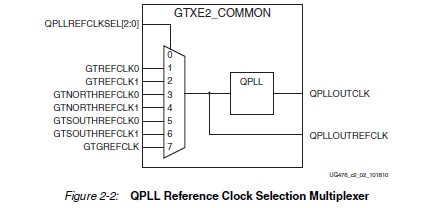

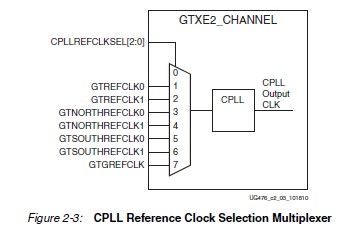

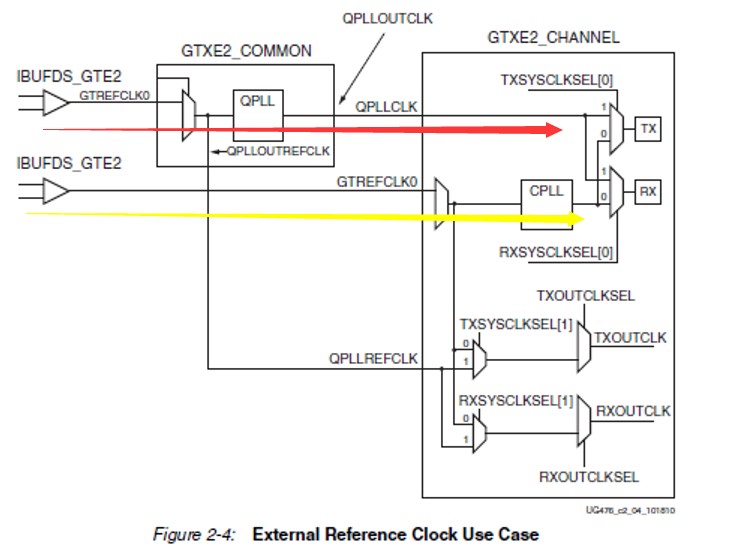

红色方框部分是两个差分参考时钟输入,每个外部参考时钟的输入必须经过IBUFDS_GTE2源语之后才能使用。绿色方框是来自其他Quad的参考时钟输入,7系列FPGA支持使用相邻(南北方向)Quad的参考时钟作为当前Quad的参考时钟,多路参考时钟源经过一个选择器之后,分两路进入QPLL和CPLL,如图五和图六,其中蓝色方框是QPLL,黄色方框是CPLL,对于一个GTX Channel来说,可以独立选择参考时钟,可以选择QPLL,也可以选择CPLL,QPLL和CPLL的区别在于两者支持的线速率不同,QPLL支持的线速率高于CPLL,图七是外部参考时钟模型的详细结构,红色箭头表示QPLL通路,黄色箭头表示CPLL通路。

图五

图六

图七

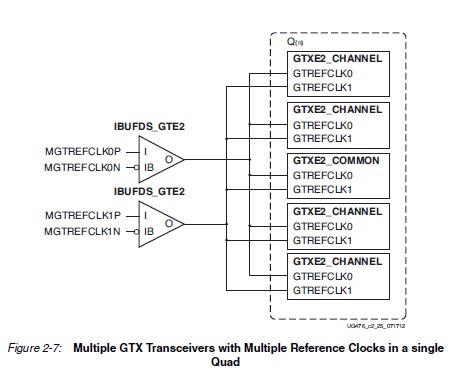

因为每一个Quad有两个外部参考时钟,因此对于每一个Quad来说,可以选择两个不同的参考时钟,每一个CHANNEL的接收端和发送端都可以独立选择参考时钟,如图八所示:

图八

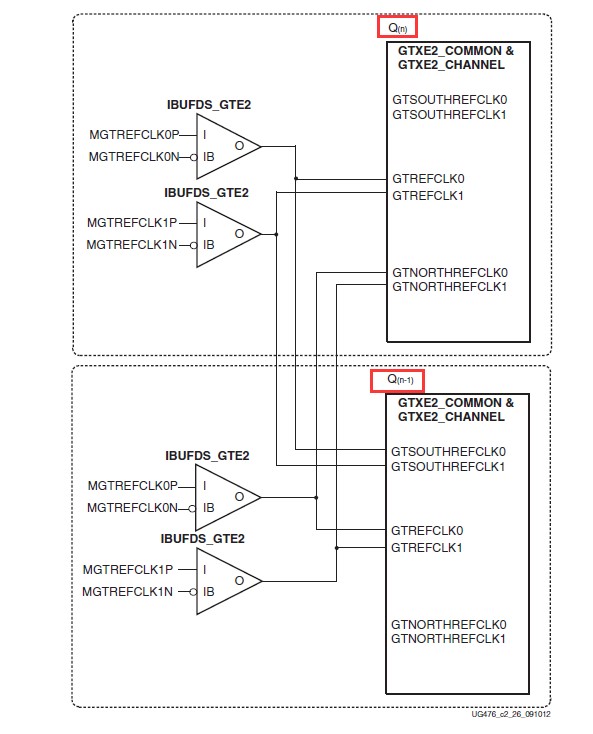

如果用户需要使用其他Quad的参考时钟源来作为当前Quad的参考时钟,在满足下面三个条件的情况下可以使用:

1. 只能使用当前Quad上方的Quad的参考时钟;

2. 只能使用当前Quad下方的Quad的参考时钟;

3. 一个Quad的参考时钟源不能驱动超过3个Quad的收发器(只能驱动当前Quad和上下方相邻两个Quad);

满足上面的条件,就可以把其他Quad的参考时钟配置成当前Quad的参考时钟,如图九所示,注意图中红色方框表示相邻的Quad:

图九

QPLL和CPLL的区别,在于两者支持的线速率不同,对于CPLL来说,支持的线速率位1.6GHz到3.3GHZ之间,而对于QPLL来说,GTX支持的线速率分两档,Lower Baud支持5.93GHz~8.0GHz,Upper Baud支持9.8GHz~12.5GHz,对于GTH则不分档位,支持的线速率为8.0GHz~13.1GHz。