- 12.3语料库NLTK数据包下载及安装

- 26款ai伪原创,手机上创作文章别错过_手机创作文章

- 3蓝桥杯Python A组国一经验分享(希望这篇文章可以给你一点点帮助)_蓝桥杯国赛一二三等奖比例

- 4bert 三种模型保存的方式以及调用方法总结(ckpt,单文件pb,tf_serving使用的pb)_bert.ckpt

- 5开源密码管理软件项目说明(附源代码)_统一密码服务平台的源代码

- 6- 概述 - 《设计模式(极简c++版)》

- 7基于matlab的指纹图像处理、脊线增强、脊线分割、脊线细化、细节点检测和细节点验证(毕设完整代码+报告)_脊线提取matlab

- 8SOC内部集成网络MAC外设+ PHY网络芯片方案:MII/RMII 接口与 MDIO 接口

- 9Java概念性问题7_哪一项的实现不可以添加为textfiled对象的监听器

- 10Transformer详解_transformer的输入

Xilinx FPGA PCIE接口调试

赞

踩

关于在linxu环境下Xilinx FPGA PCIE的接口调试从中遇到了几个问题,第一个就是时钟接口的选择,还有一个就是上位机如何识别XDMA;

操作系统环境:Linux

板卡:两款开发板VC707、KCU105

上位机环境准备:从Xilinx官网下载linux环境的XDMA驱动,并编译安装好;

一、PCIE时钟接口

1. 从VC707的pcie例程中可以看到,开发板自带的金手指的时钟通过

在约束文件中set_property LOC IBUFDS_GTE2_X1Y5 [get_cells refclk_ibuf_0]规定好了通道,在TOP文件中用

IBUFDS_GTE2 refclk_ibuf_0 (.O(sys_clk_0), .ODIV2(), .I(sys_clk_p_0), .CEB(1'b0), .IB(sys_clk_n_0));

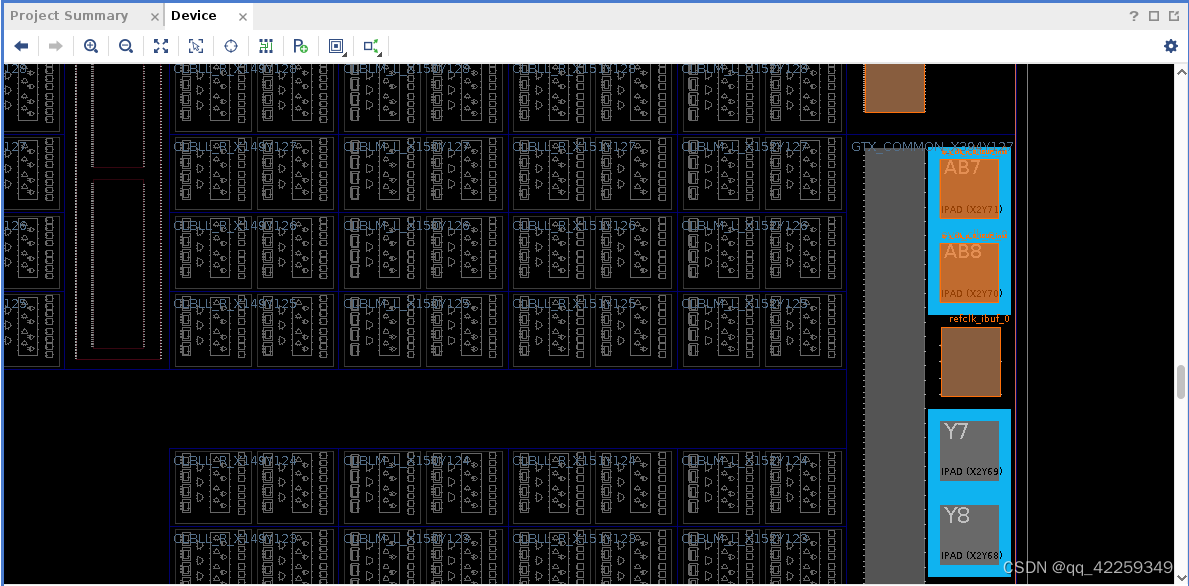

源语一次即可,这里的X1Y5是固定到了AB7、AB8管脚,如下图所示,AB7、AB8下方就是refclk,用鼠标放置在该buf上,就会显示其编号为X1Y5;

2.现在VC707的FMC接口引出PCIE管脚,对应的时钟约束管脚找了官方的各种手册都没有找到,后来在open systhesized design的版图中,能找到管脚对应的refclk_ibuf的编号;当管脚选择为E9,E10时,对应的refclk为X1Y10;

3.KCU105的时钟管脚与VC707的约束办法以及源语方式又不一样,在约束文件中可以用

set_property LOC H6 [get_ports sys_clk_p]

create_clock -name sys_clk -period 10 [get_ports sys_clk_p]

在top文件中,用下述源语描述即可;

IBUFDS_GTE3 # (.REFCLK_HROW_CK_SEL(2'b00)) refclk_ibuf (.O(sys_clk_gt), .ODIV2( sys_clk ), .I(sys_clk_p), .CEB(1'b0), .IB(sys_clk_n));

若是要换成FMC的pcie管脚,在约束文件中将对应的时钟管脚更换即可;

二、如何识别XDMA

除了要使用XDMA这个IP,上位机要识别XDMA,还需要reg_map;