热门标签

热门文章

- 1无人机巡检光伏电站的原理是什么

- 2Flutter 可冻结的侧滑表格 sticky-headers-table 结合 NestedScrollView 吸顶悬浮的使用实践_table_sticky_headers

- 3CSDN 让你的文章成为全球开发者的参考资料

- 4游戏开发者有必要写博客的6大原因_开发游戏的理由

- 5ACM SIGKDD 2020 Conference会议资料整理_static.cpss20.xyz

- 6python在tkinter中使用ttk模块在窗口中添加按钮模块(Button)_ttk怎么创建可拖放按钮

- 7黑马瑞吉外卖项目(毕业设计论文版)三份不同目录的文档可以选择都在两万字左右。_瑞吉外卖论文

- 8【GitHub学生包】2022年12月GitHub学生包最新申请教程 18次认证失败的经验之谈_github education pack学生包

- 9拼团模式--社交电商的常见营销手法_拼团社交式电商营销介绍

- 104.18作业

当前位置: article > 正文

一句话或一张图讲清楚系列之——ISERDESE2的原理

作者:花生_TL007 | 2024-04-23 15:52:38

赞

踩

一句话或一张图讲清楚系列之——ISERDESE2的原理

主要参考:

https://blog.csdn.net/weixin_50810761/article/details/137383681

xilinx原语详解及仿真——ISERDESE2

作者:电路_fpga

https://blog.csdn.net/weixin_45372778/article/details/122036112

Xilinx ISERDESE2应用笔记及仿真实操

作者:郭郭的柳柳在学FPGA

原理

- 校准模式

输入端循环输入8’h5c和8’h82交替的校准序列,接收端比较接收到的并行数据,如果与发送端不一致,则产生1个CLKDIV的BITSLIP信号,使并行数据的顺序滑动一次,等待3个CLKDIV后,比较滑动后的结果是否一致,如果一致则不再产生BITSLIP信号,直到检测到8个连续一致信号,认为字节边界已经对齐,随后进入工作模式。 - 工作模式

可以传输字节边界对齐的数据,也可以产生伪随机字节序列检测整个发送和接收通路的正确性。

重要参数

重要参数有两个:DDR、NETWORKING

ISERDESE2 #(

.DATA_RATE("DDR"),//位时钟的上升沿和下降沿都有效

.DATA_WIDTH(DESER_FACTOR),

.INTERFACE_TYPE("NETWORKING"),//可以使用BITSLIP

.DYN_CLKDIV_INV_EN("FALSE"),

.DYN_CLK_INV_EN("FALSE"),

.NUM_CE(2),

.OFB_USED("FALSE"),

.IOBDELAY("NONE"),

.SERDES_MODE("MASTER"))

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

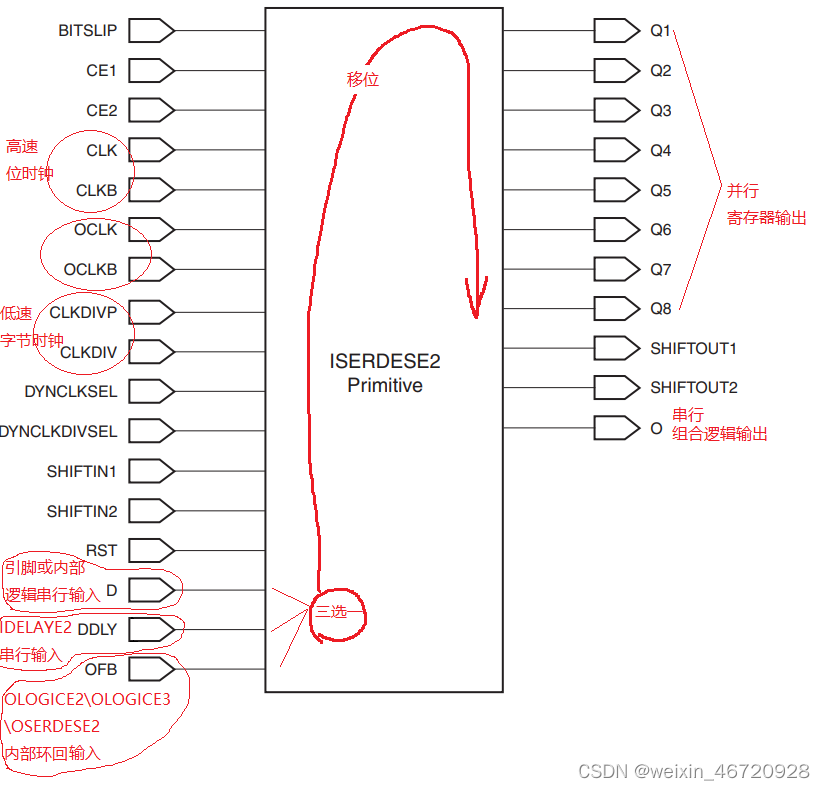

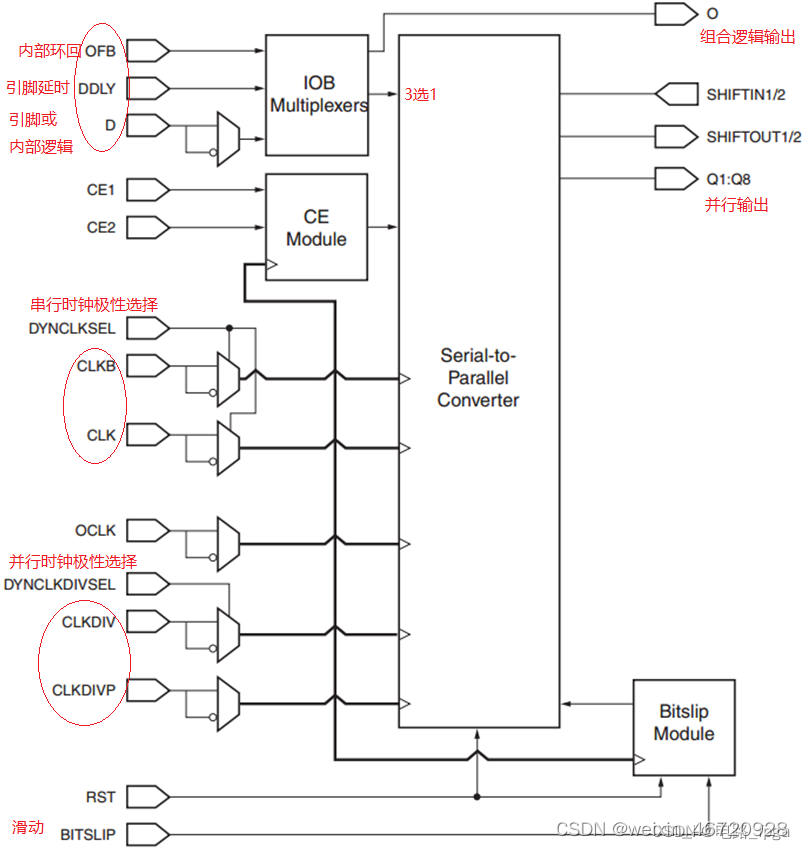

重要端口

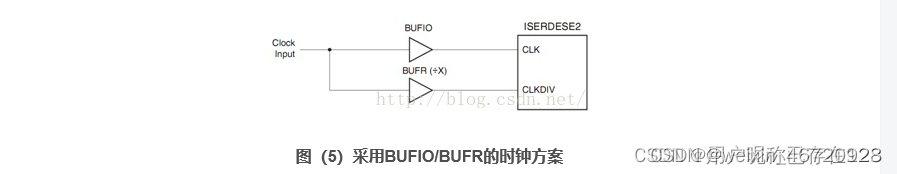

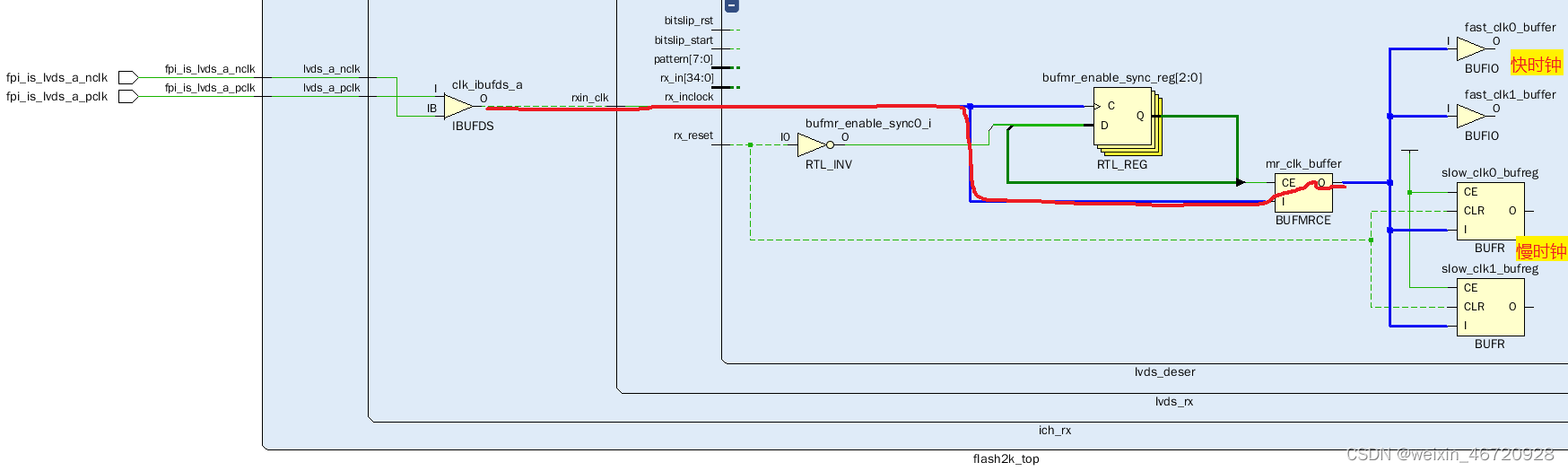

时钟方案

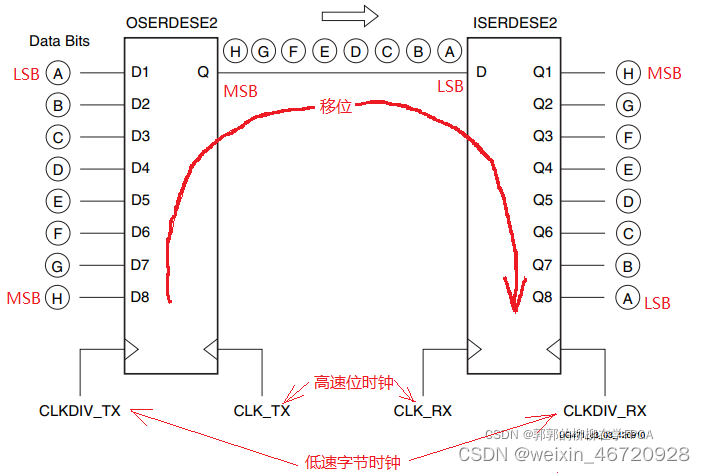

bit顺序

发送方:

.D1 ( din[0] ),

.D2 ( din[1] ),

.D3 ( din[2] ),

.D4 ( din[3] ),

.D5 ( din[4] ),

.D6 ( din[5] ),

.D7 ( din[6] ),

.D8 ( din[7] ),

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

接收方(高低位颠倒):

.Q1 ( q[7] ),

.Q2 ( q[6] ),

.Q3 ( q[5] ),

.Q4 ( q[4] ),

.Q5 ( q[3] ),

.Q6 ( q[2] ),

.Q7 ( q[1] ),

.Q8 ( q[0] ),

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

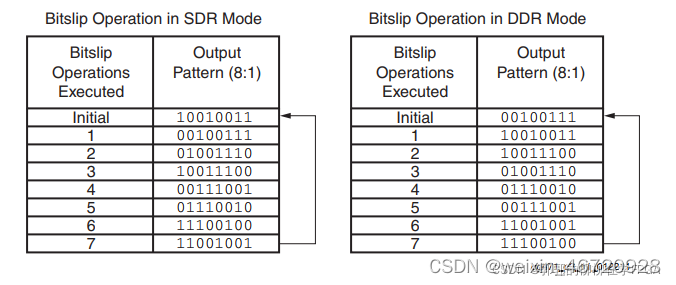

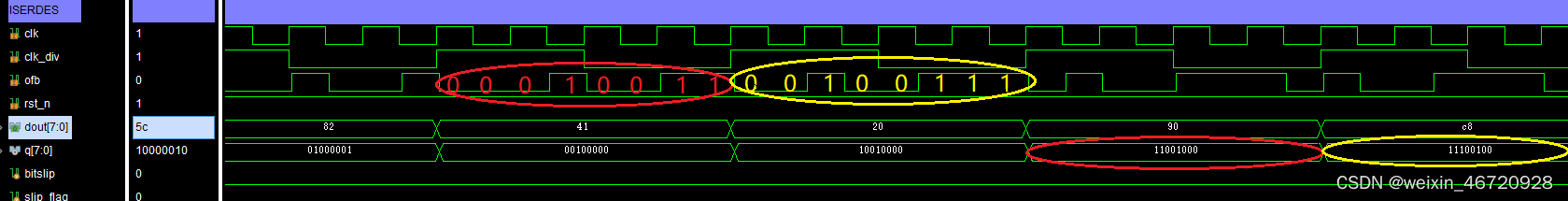

滑动

SDR模式下:每次的BITSLIP操作,会使输出左移1位;当8次操作后,恢复到最初状态;

DDR模式下:每次的BITSLIP操作,会使输出交替进行右移1位和左移3位操作,当8次操作后,恢复到最初状态;

移位延时

BitSlip与CLKDIV同步,移位脉冲BITSLIP在CLKDIV上升沿有效后,3个CLKDIV完成移位。

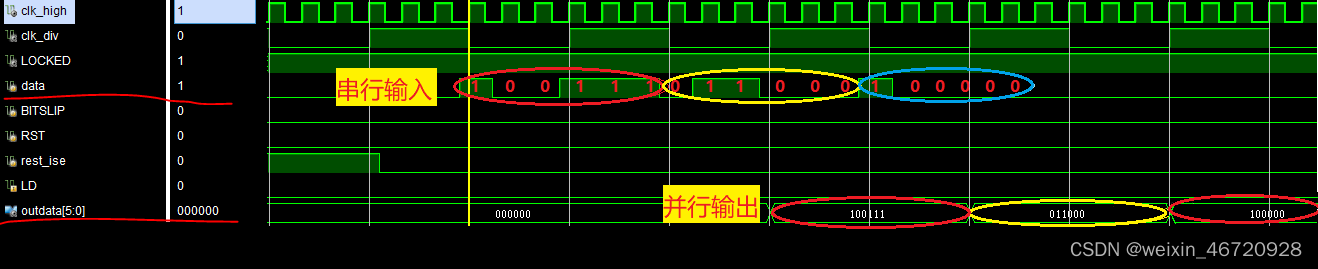

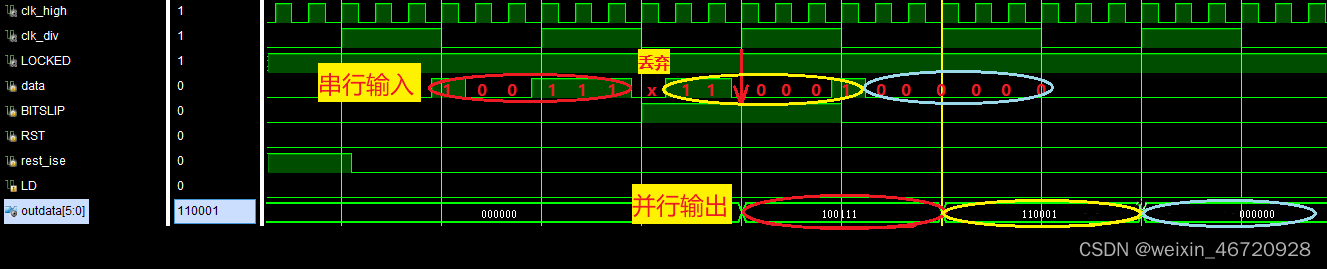

BITSLIP的作用

修改串转并的起始位置

BITSLIP前:

BITSLIP后:

丢弃1bit

串并转换延时

2个CLKDIV

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/花生_TL007/article/detail/474751

推荐阅读

相关标签