热门标签

热门文章

- 1Python与大数据:Hadoop、Spark和Pyspark的应用和数据处理技巧_python hadoop

- 2邊緣智能2024—AI開發者峰會(5月9日)數碼港即將啟幕_2024年5月9日ai

- 3Windows下双网卡配置静态路由,实现多网络同时使用_双网卡路由设置命令

- 4金融支付系统的API安全 & 认证机制

- 5LlamaIndex 组件 - Prompts_llama prompt配置

- 6华为杯研究生数学建模优秀参考论文(优秀论文参考2004-2022年)_华为杯数学建模优秀论文

- 7计算机百科丨存储介质发展史

- 8移动端开发必会出现的问题和解决方案_touchmove速度

- 9AtCoder Beginner Contest 354 (ABCDEFG题)视频讲解_abc354 题目b讲解

- 10api-ms-win-core-synch-l1-2-0.dll文件丢失解决方法_api-ms-win-core-synch-l2-0.dll

当前位置: article > 正文

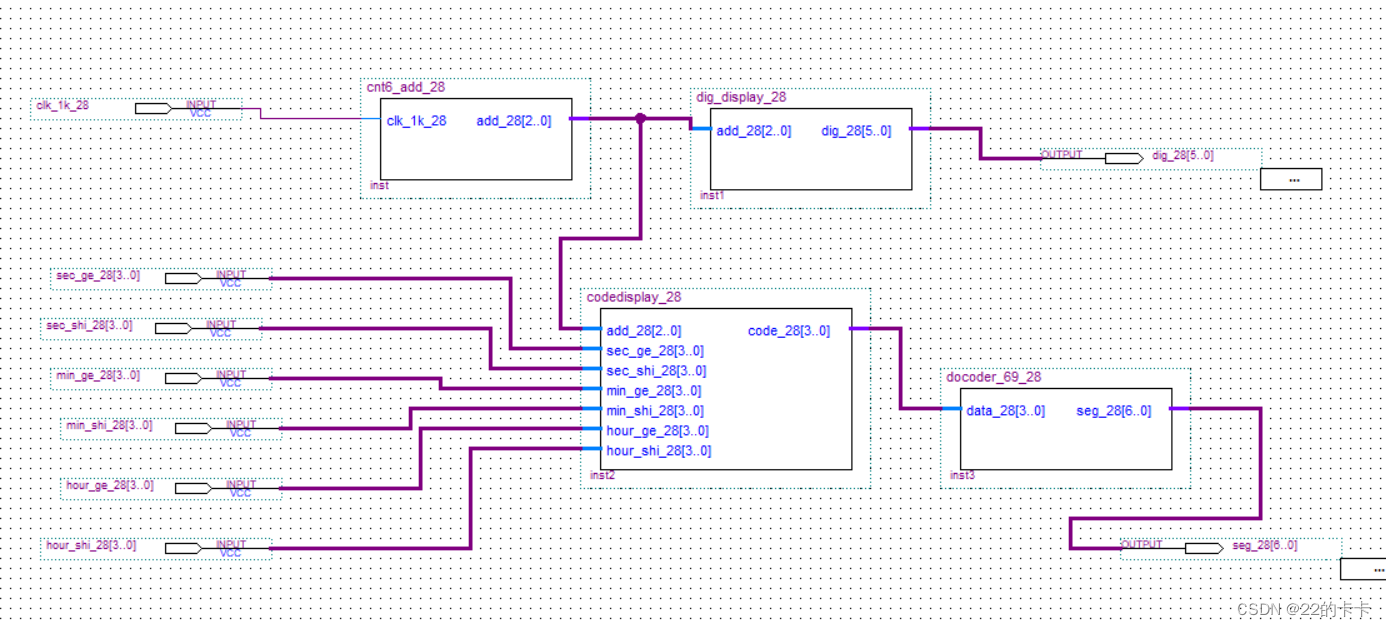

实验九 基于FPGA的计数译码显示电路设计_基于fpga的计数译码显示电路设计69的补段

作者:花生_TL007 | 2024-05-29 20:09:57

赞

踩

基于fpga的计数译码显示电路设计69的补段

基本任务一:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选

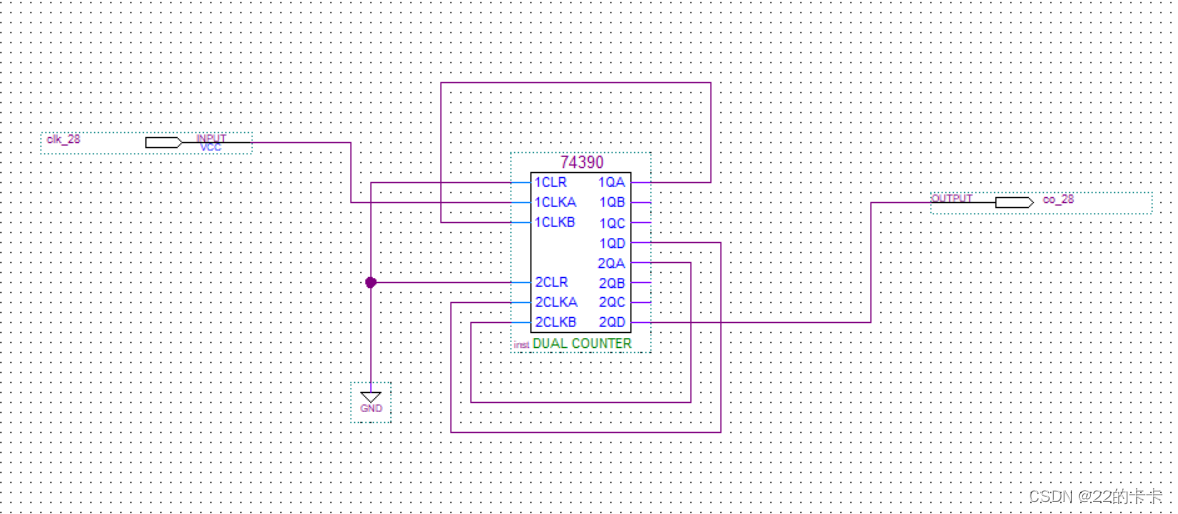

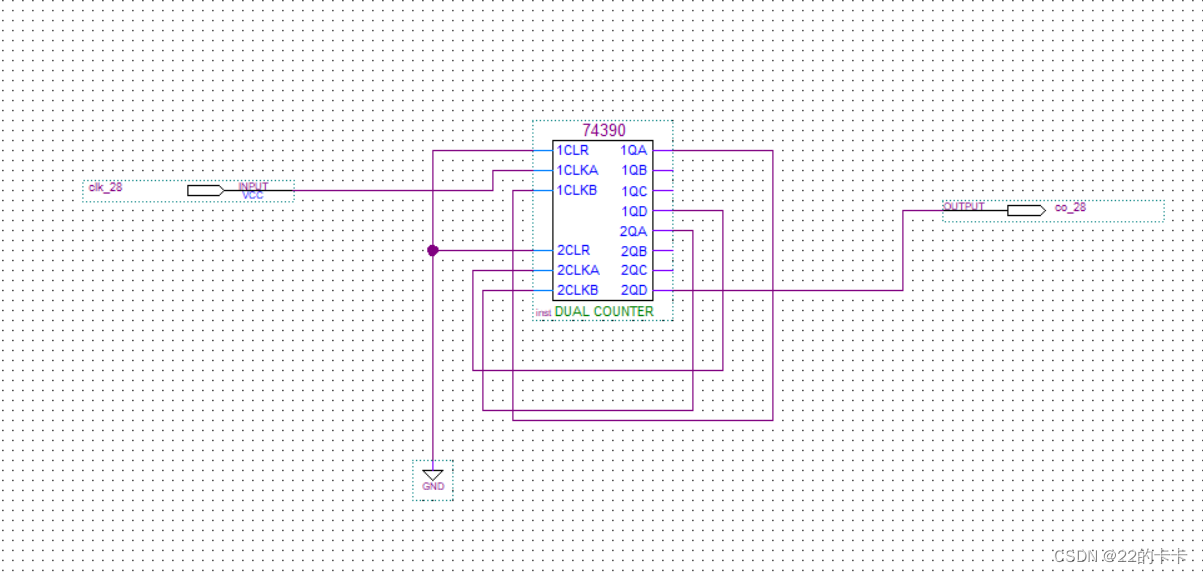

m100:

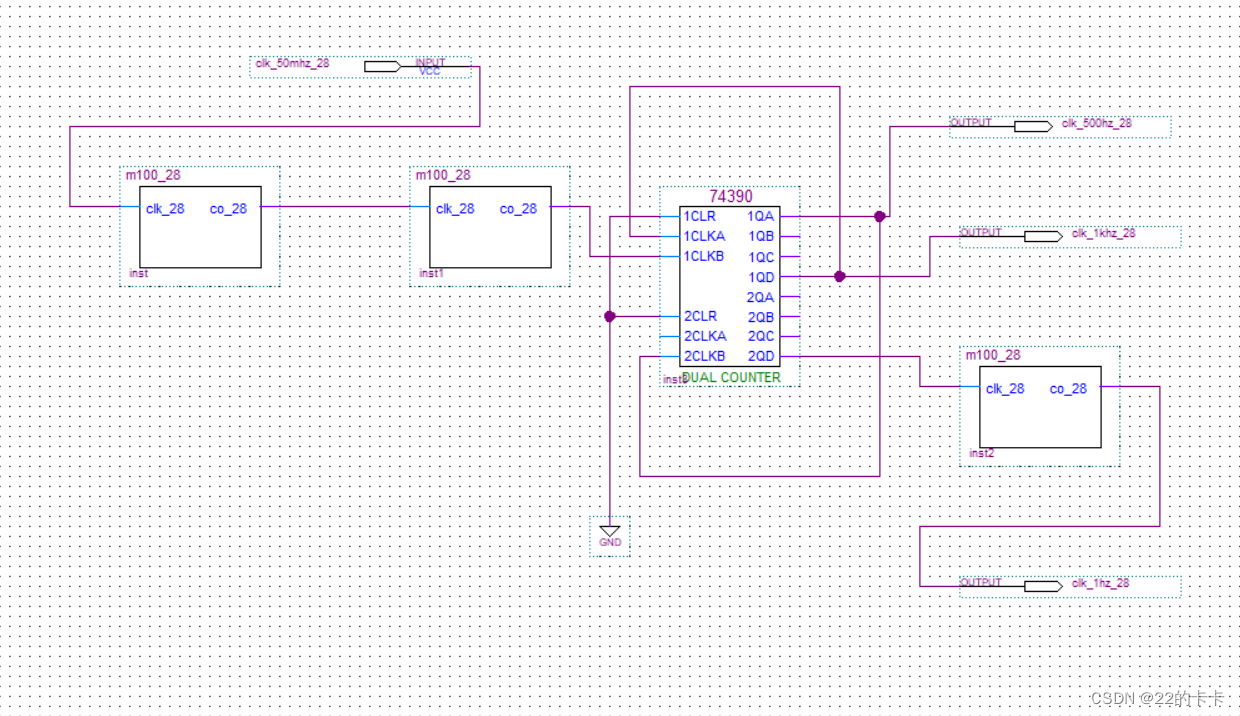

frediv:

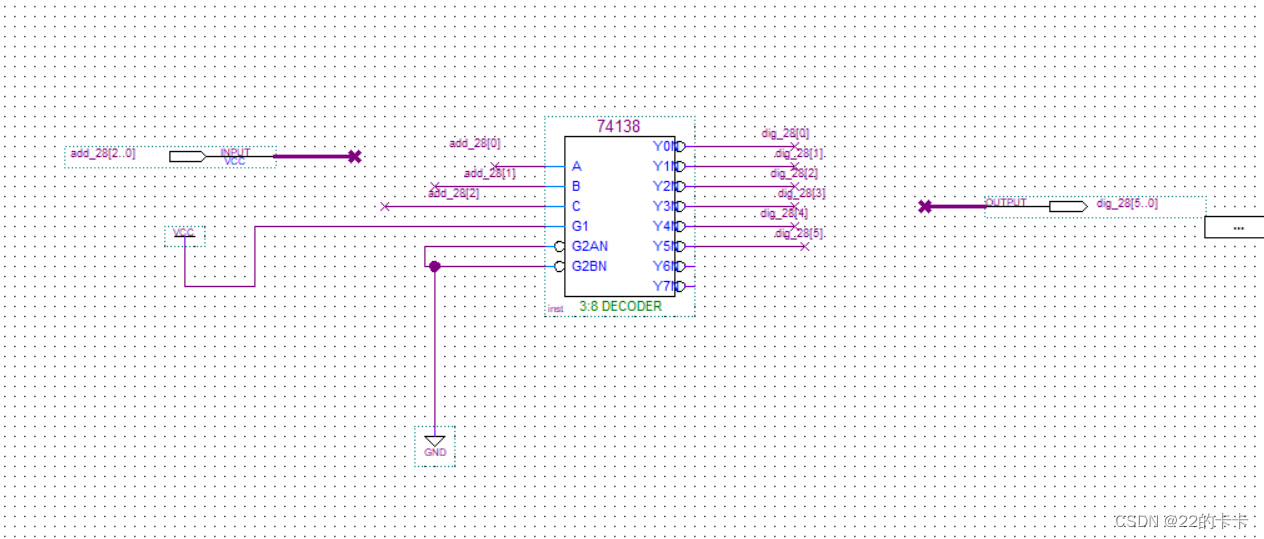

decoder:

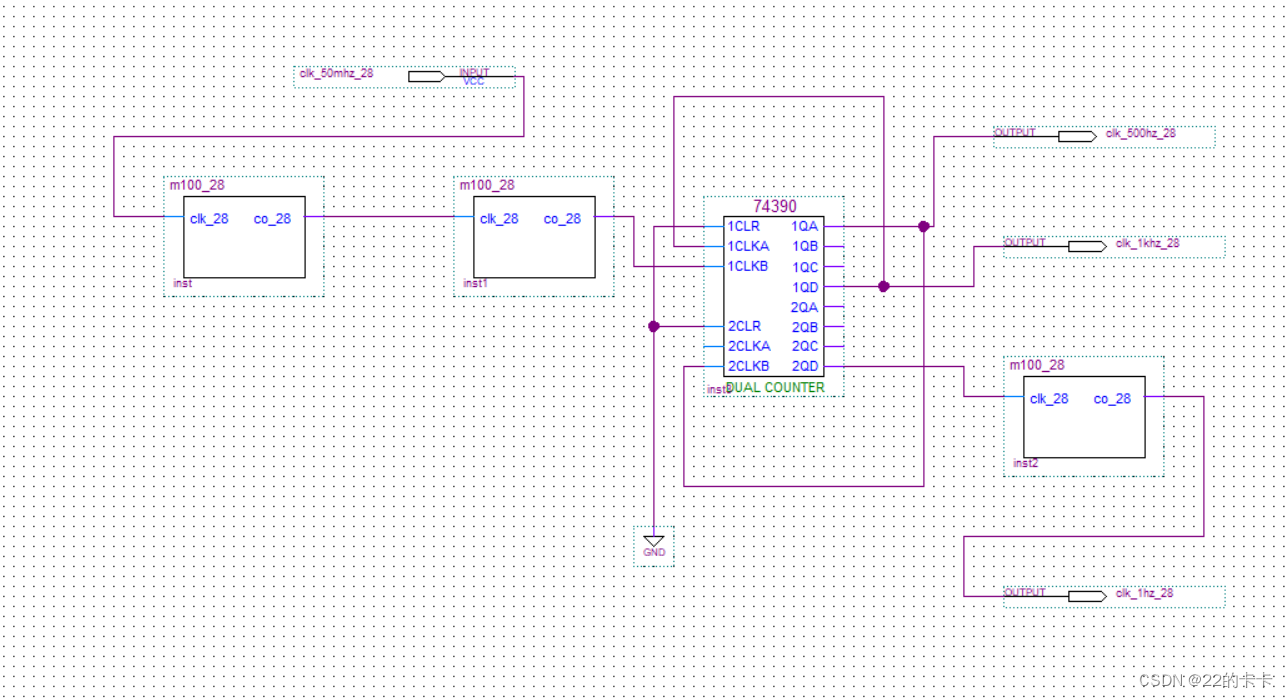

基本任务二:利用FPGA硬件平台上的4位数码管显示m10技术结果

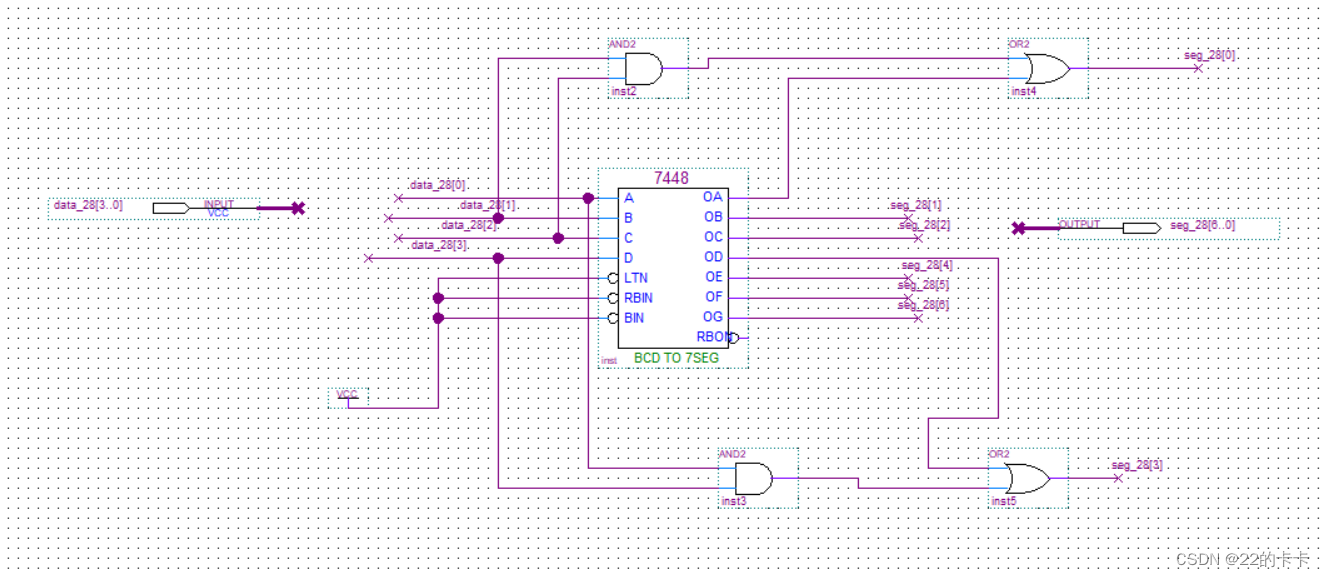

扩展任务一:对7448译码的6和9进行补段

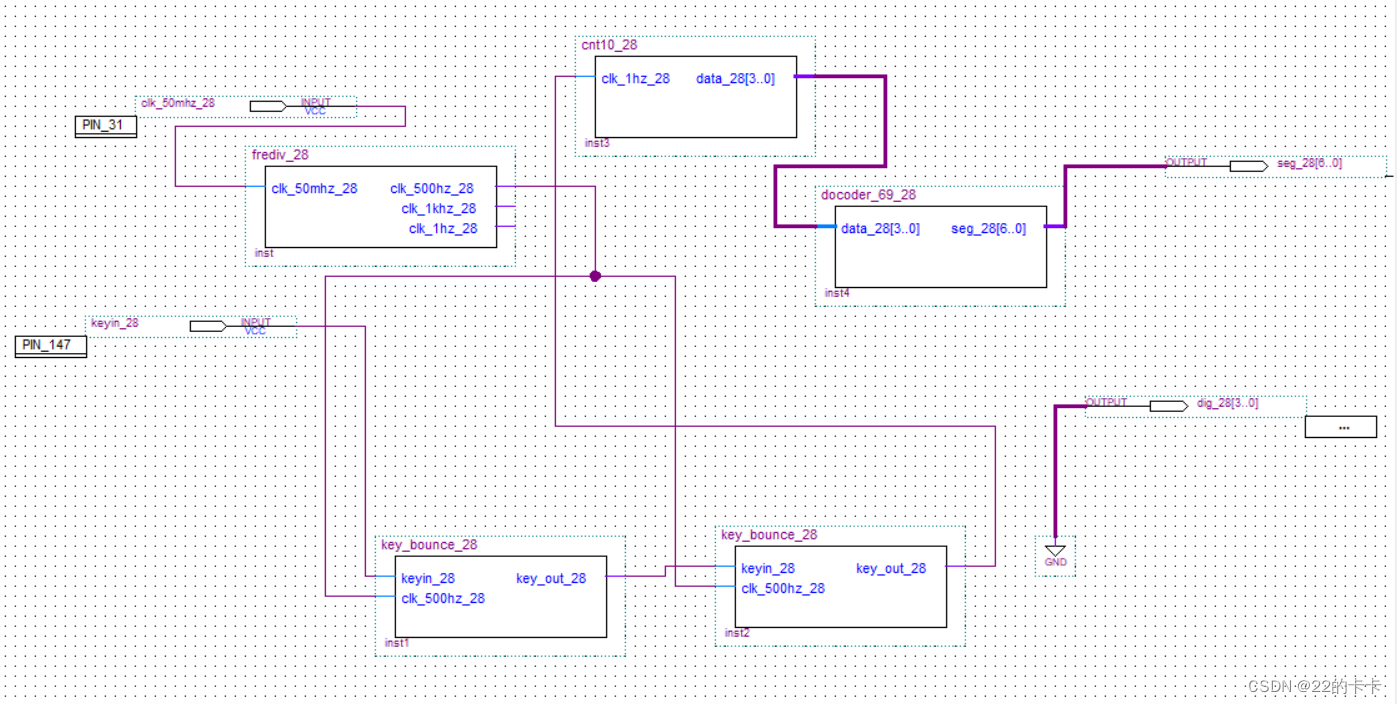

扩展任务二:用按键控制计数器从0-9计数,4位数码管显示技术结果。

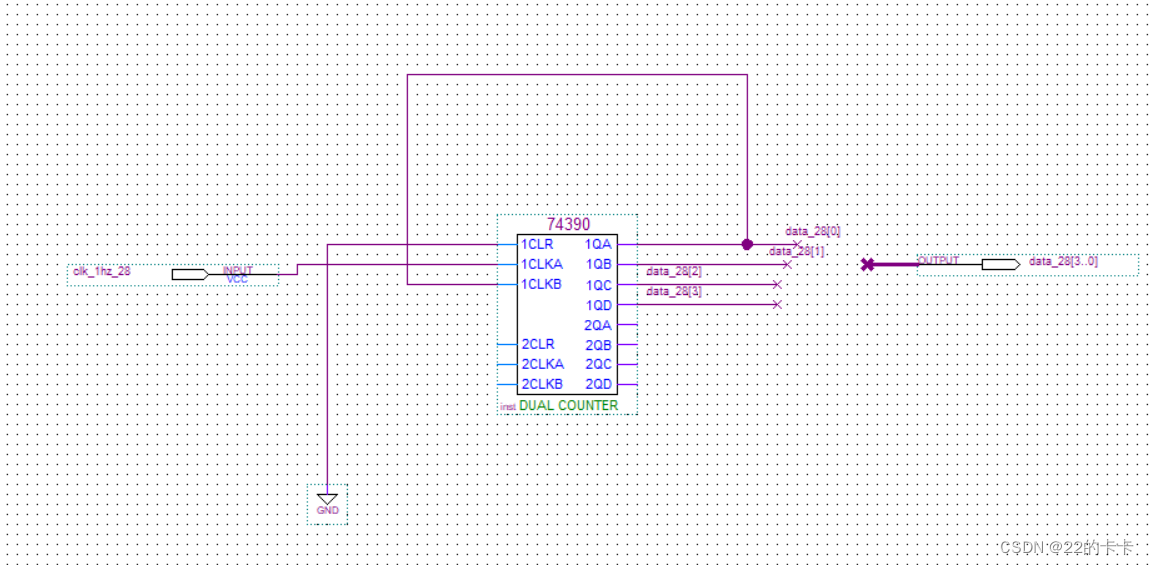

cnt10:

decoder69:

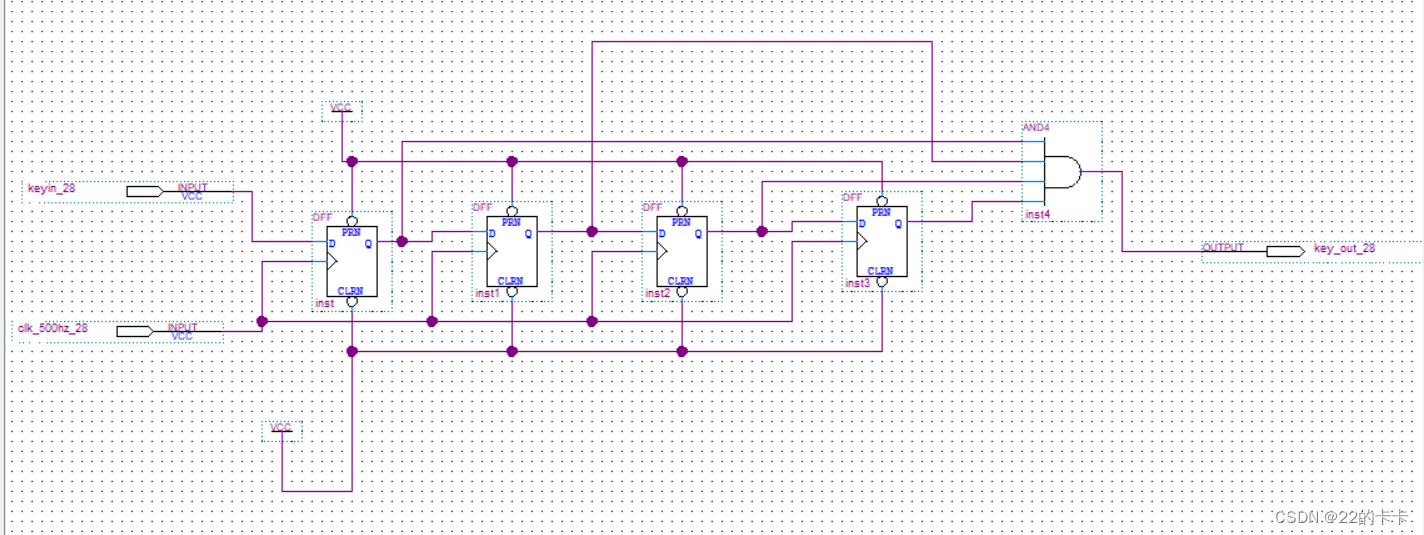

key_bounce:

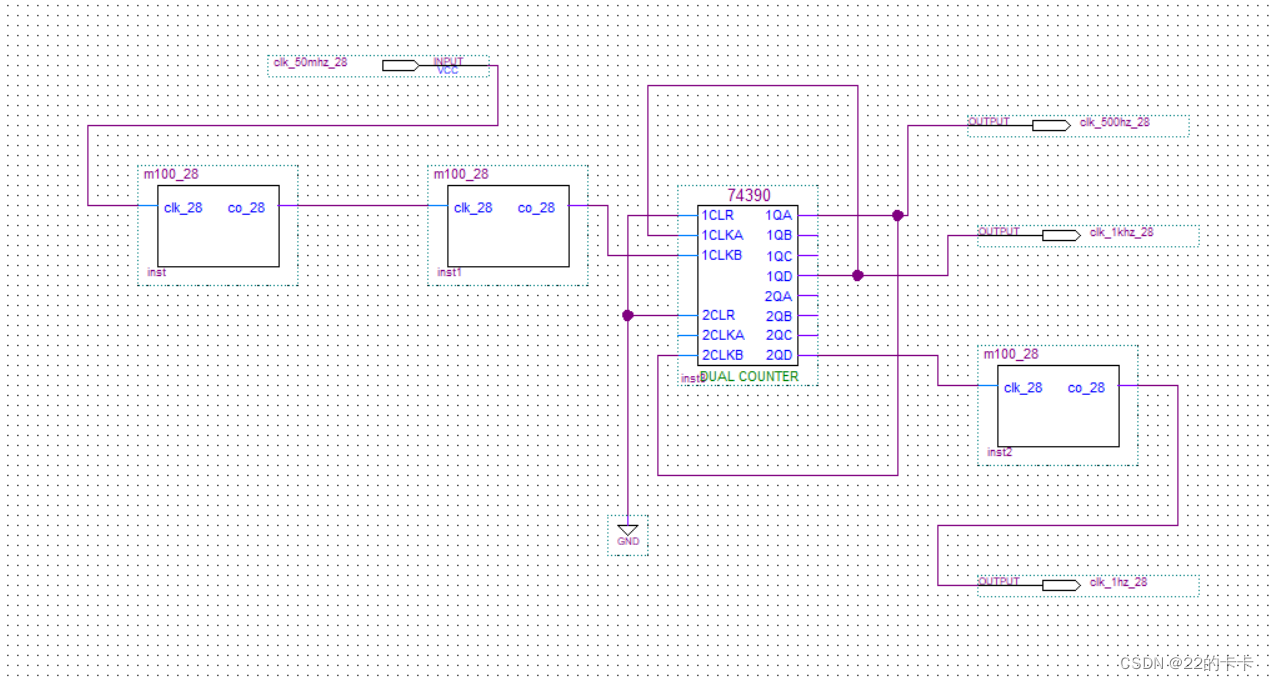

frediv:

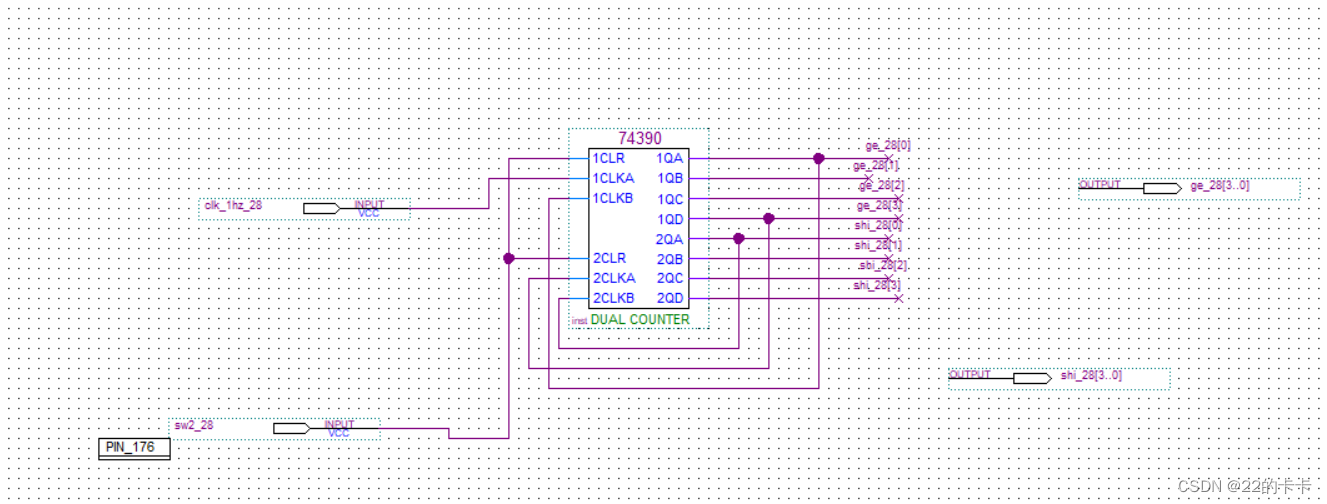

基本任务三:利用FPGA硬件平台上的6位数码管显示模100计数结果。

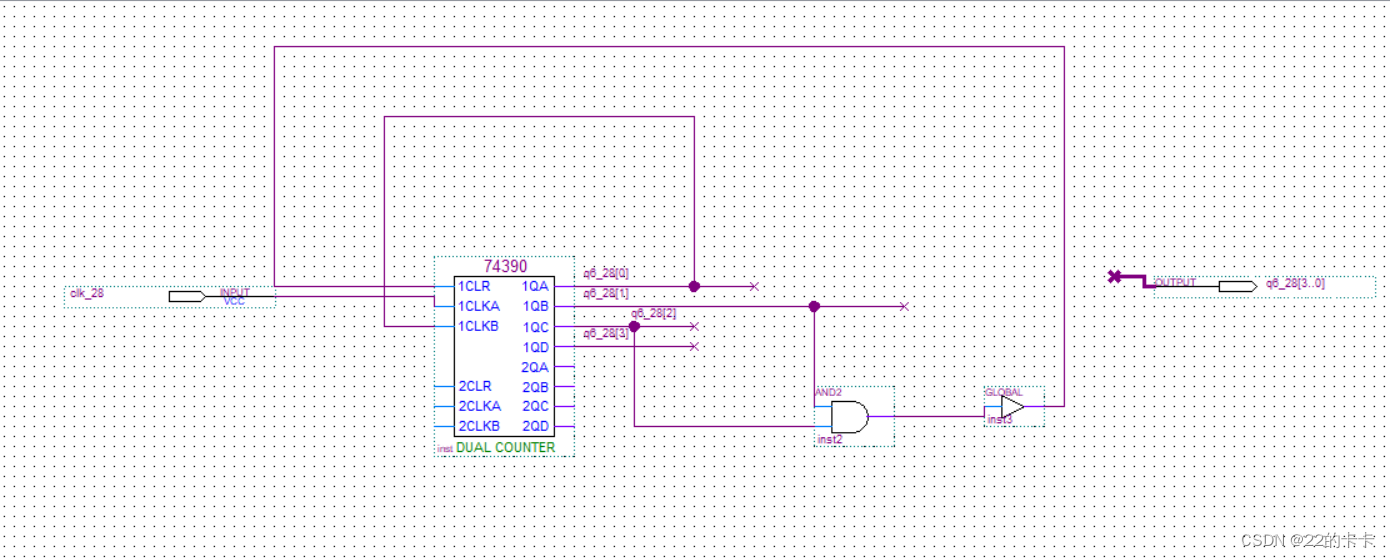

cnt6:

m100:

frediv:

decoder——69:

m100_2output:

dig_select:

code_select:

display_m100:

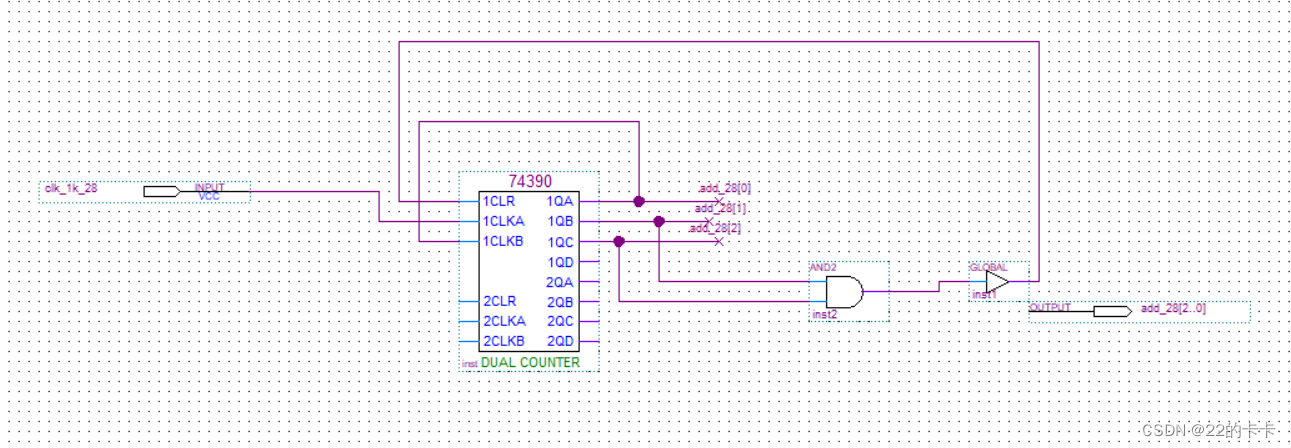

cnt6_add

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/花生_TL007/article/detail/643769

推荐阅读

相关标签