- 1STM32F103用IO口和DS1302模块通信_ds1302z i2c stm32

- 2React EasyUI插件 学习笔记(基础)详细版

- 3Android 开发中的SSL pinning_ssl pinning 抓包

- 4i春秋ctf练习_c7d888-36f66bfc_d2edc4f0-23def191a3

- 5fastdfs部署详解

- 6PTA 估值一亿的AI核心代码 正则表达式 regex_replace_ai正则表达式 开源

- 7第46届世界技能大赛网络系统管理项目江苏省选拔赛赛题-模块B样题v1.4——Windows功能模块配置(部分解析)_离线后自动切换为主要dns服务器

- 8寒武纪面试——数字IC,数字逻辑岗_寒武纪都是电话面试嘛

- 9uniapp里面tabbar自定义的方法_uniapp 自定义tabbar

- 10【CANFD详细介绍与CAN区别】

轻松成为设计高手_轻松学习 verilog pdf

赞

踩

目录

2、Verilog语言基础

2.1、三种描述方法

1)数据流描述:assign连续赋值语句

2)行为描述:过程赋值语句,always和initial过程块

3)结构化描述:实例化已有的功能模块

逻辑值:net型如果没有赋初始值,其值为高阻;reg型没有初始化,其值为x。这一点在仿真时verdi软件看出来。

变量的物理含义:

1)线网变量:通常用在连续赋值中,可以理解为时电路中的连线,一根导线

2)reg变量:并不能严格对应于电路中的存储单元(触发器或者锁存器)。寄存器类型存的值,是从一个赋值到下次赋值的值都被保存,并且在仿真过程中会保持而不会丢失。

这些是一直以来我们对这两个变量的理解,但是从仿真器的角度或者说从verilog语法的发明者来说说这两个变量:reg型变量是占用仿真环境的物理内存的,寄存器被赋值之后就一直保存物理内存中,并且保持该值不变,知道下一次对该寄存器变量进行赋值。而线网类型实际上是不占仿真内存的,它的值是由当前驱动他的变量决定的(可以理解是每个time都在计算这个wire型变量值)。

因此:所谓reg并不指示能综合成电路上的寄存器,而是指示这个变量占用实际的物理内存。但是在D触发器建模的时候必须用reg型的变量。

(实际电路-------实际物理内存)

驱动和赋值:

驱动:线网是被驱动的,该值不会被保持,在任意一个仿真步进上都需要重新计算。

赋值:寄存器是被复制的,并且在仿真过程中,该值会被保持,直到下一个赋值的出现

3、描述方式和设计层次

数据流描述:连续assign语句,信号经过组合逻辑类似数据的移动,信号从输入流向输出,信号不会存储,会实时影响。

1)连续驱动:任何时刻的输入都会影响输出

2)只有线网类型能够在assign中赋值,线网类型可以多驱,而寄存器不允许被多驱。

3)并行性:所有assign语句进程是并发的。

高级编程语句:

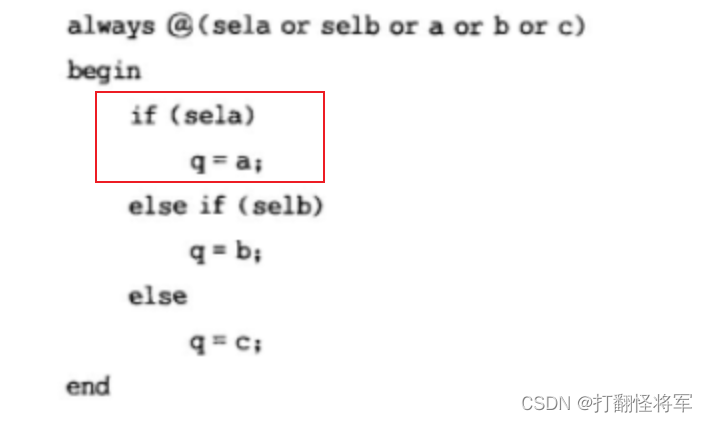

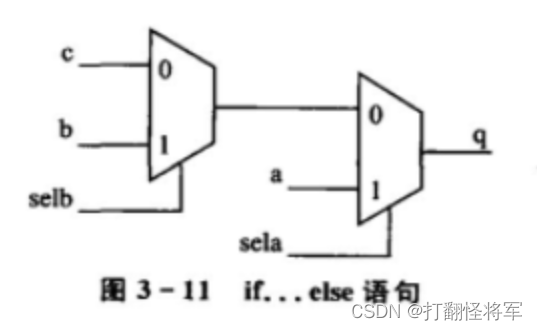

1)if else

从上到下逐条检查。具有优先级顺序,如果sela是关键路径的话,利用这样的优先级编码提高设计的性能,逻辑中的级数要明显少一些。(为什么需要组合逻辑的级数少一些?)学习以下if-else会综合成什么?

4、RTL概念与常用RTL建模

作者推荐的设计步骤

1)功能定义和模块划分

2)定义所有模块的接口

3)设计的时钟域

单单看这三点实际上是没有太多感触的,不妨谈一下我的感悟。

功能定义和模块划分:记得实习最初让我们做一个很简单的设计,但是当时菜的扣脚,甚至不能知道整个模块的顶层是什么样,输入输出接口是什么样,更别提内部模块划分了。所以第一步明确需求,了解顶层的输入输出,根据整个功能划分模块。其中划分模块又有几点需要注意,记得当时我们已经划分好模块了但是在逻辑设计的时候仍然是信号从前到后的画波形图理不清楚,当时出现这个原因的问题是,即使我明确了每个模块的功能,但是对每个模块的接口时序没有理清楚,导致一根信号从头到尾地去思考。其实一旦我们划分好模块就只思考该模块的功能,以及他最终要输出什么信号给后级模块。后级模块再利用这个信号去思考,做到真正模块划分。总结一下,明确每个模块的内部功能以及模块最终输出接口上的信号。时钟域相对复杂,暂时我也不太清楚(留个坑 当我有了新经验和感悟的时候再来填)

4)设计的关键路径

关键路径指的是设计中的时序要求最难以满足的路径。设计的时序主要再频率,建立时间,保持时间。(这儿我也不太懂,但是浅谈以下。实习的时候每次rt白盒化后,他们会算组合逻辑的级数看是否满足时序,应该是为了满足建立时间)通过一些时序手段(pipeline、retiming、逻辑复制等)缓解时序压力,这种方法比单依靠综合和布局布线工具的自动优化有效的多。

5)顶层设计

6)FSM设计

7)时序逻辑设计

根据时钟域划分好寄存器组,描述各个寄存器的数据传输方式(哎 不懂)

8)组合逻辑设计

一般来说,大段的组合逻辑最好和时序逻辑分开描述,这样有利于时序约束和时序分析,使综合器和布线布局达到更好的优化效果。

寄存器电路建模