- 1MySQL约束(Constraint)_mysql约束名是什么

- 2经典实例分割模型Mask RCNN原理与测试

- 32023-2024年中国人工智能计算力发展评估

- 4Mysql配置_mysql怎么配置

- 5MAGNet:Meta文本音乐生成工具,吉他摇滚、电子音乐都能搞定_meta 唱歌ai

- 6【Python】Python中assert语句的用法

- 7Android13系统导航栏添加隐藏导航栏功能按钮_we may show taskbar on the default display for lar

- 8服务发现:Zookeeper vs etcd vs Consul_consulratelimit kvloader

- 9头歌——一维数组和二维数组全对答案秒过_头歌二维数组右上部分求和

- 10go mod常用命令 以及 常见问题_go.mod already exists

软考中级-软件设计师【笔记】_软件设计师中级笔记

赞

踩

第一章 计算机组成与体系结构

-

进制转换问题

(1)短除法(十进制转其他进制)

(2)按权展开法(其他进制转10进制)

例:二进制10111转成十进制 1 * 2 ** 0 + 1 * 2 ** 1 + 1 * 2 ** 2 + 0 * 2 ** 3 + 1 * 2 ** 4 = 23

(3)二进制转八进制和十六进制

二进制转八进制严格按照三位数转换,十六进制按照四位数转换 -

编码问题

(1)原码:大部分都是32位的原码,首位为符号位(0为正数,1为负数),正数的反码补码与原码一样

(2)反码:符号位不变,其他跟原码取反

(3)补码:在反码的基础上加上1

(4)移码:在补码的符号位取反 -

浮点数运算

(1)表达式:N=M * R ** E(其中M称为尾数,E为指数,R为基数)

(2)运算过程:对阶->尾数计算->结果格式化

例:2451=2.451*10**3 -

计算机结构

(1)主机构成:CPU和主存储器(内存)

(2)CPU中的运算器

~算术逻辑单元ALU

~累加寄存器AC(暂时存放ALU运算的结果信息)

~数据缓冲寄存器DR(内存储器读数据时暂存)

~状态条件寄存器PSW(存储运算过程中相关标志位)

(3)CPU中的控制器

~程序计算器PC(用于存放下一条指令所在单元的地址)

~指令寄存器IR

~指令译码器

~时序部件(产生计算机各部件所需的定时信号的部件) -

Flynn分类法

(1)单指令流单数据流SISD

~早期串行计算机,在某种周期内只能处理一个数据流(单处理器系统)

(2)单指令流多数据流SIMD

~可以一个指令流处理多个数据流(并列处理器,阵列处理器和超级向量处理器)

(3)多指令流单数据流MISD

~多个指令流处理一个数据流(展示没有应用,文献中有流水线计算机)

(4)多指令流多数据流MIMD

~多个指令流处理多个数据流(多处理机系统,多计算机和双核处理器) -

CISC和RISC(指令系统)

(1)CISC(复杂)

~指令数量多,使用频率差别大,可变长格式

~支持多种寻址方式

~微程序控制技术可实现

~研制周期长

(2)RISC(精简)

~指令数量少,使用频率接近,定长格式,大部分为单调指令

~支持寻址方式少

~增加了通用寄存器;硬步逻辑控制为主,适合采用流水线

~优化编程,有效支持高级语言 -

流水线

(1)定义

~流水线技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。

(2)计算

~流水线周期是为执行时间最长的一段

~执行n条指令时间公式为:一条指令执行时间+(指令条数-1)* 流水线周期

~吞吐量是指单位时间内流水线所完成的任务数量或输出的结果数量。

~吞吐率公式:TP=指令条数/流水线执行时间

~流水线最大吞吐率:TPmax=1/Δt

~流水线加速比是指完成同样一批任务,不使用流水线的时间所用的时间之比。

~加速比计算公式:S=不使用流水线执行时间/使用流水线执行时间

~流水线的效率是指流水线的设备利用率。

~效率公式:E=n个任务占用的时空区 / k个流水段的总的空时区 -

层次化存储结构

(1)CPU中的寄存器的存储速度最高,但内存最小的->Cache:按内容存取(容量与存储速度成反比)

->内存(主存)->外存(辅存,硬盘,光盘,U盘) #->指速度越来越慢 -

Cache

(1)Cache的功能

~提高CPU数据输入输出的速率

~在计算机存储体系中,Cache是访问速度最快的层次(除寄存器)

~使用Cache改善系统性能的依据是程序的局部性原理

(2)计算平均周期

-

局部性原理

(1)分类

~时间局部性:在一段时间内多次访问相同的内容

~空间局部性:在一段时间内访问相邻空间

~工作集理论:工作集是进程运行时被频繁访问的页面集合 -

主存

(1)分类

~随机存取存储器

~只读存储器

(2)编址(计算题)

~地址单元数量:例:从AC000H到C7FFFH:C7FFFH+1-AC000H=1C0000(16进制计算;变成单位K,除以1024)

~公式(求公式里面的任意一个变量的值):(n个地址单位 * 内存地址按字m编址) / (由k片存储器芯片构成 * 每片有

j个存储单元 * 每个存储单元i位) -

磁盘结构与参数

(1)磁盘分为磁道和扇区

(2)计算

~存取时间 = 寻道时间 + 等待时间(平均定位时间 + 转动延迟)

~单缓存区处理,需要一个处理完才能处理下一个 -

计算机总线(根据位置不同分)

(1)内部总线:一种内部结构,是cpu、内存、输入、输出设备传递信息的公用通道。

(2)系统总线:一个单独的计算机总线,是连接计算机系统的主要组件。

~数据总线:它既可以把CPU的数据传送到存储器或输入输出接口等其它部件,也可以将其它部件的数据传送到CPU。

~地址总线:属于一种电脑总线 (一部份),是由CPU 或有DMA 能力的单元,用来沟通这些单元想要存取(读取/写入)电脑内 存元件/地方的实体位址。

~控制总线:主要用来传送控制信号和时序信号。

(3)外部总线:指片外总线,是CPU与内存RAM、ROM和输入/输出设备接口之间进行通讯的通路。 -

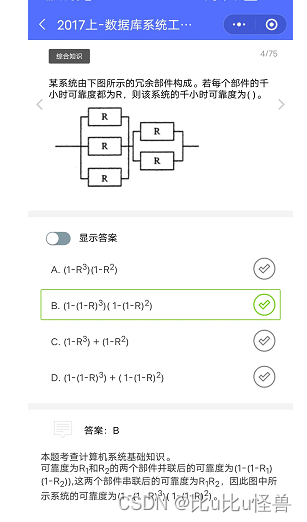

串联并联系统计算

(1)串联需要每一个串联部件都能成功,才能实现

~串联需要每一个部件可靠性相乘**(R=R1*R2…RN)**

(2)并联只需要并联中其中一个部件可以用即可

~ 1-(1-R1) * ( 1-R2) * …(1-RN)

例:

-

海明校验码(我也没听懂)

(1)差错控制

~差错控制在数字通信中利用编码方法对传输中产生的差错进行控制,以提高传输正确性和有效性的技术。

(2)循环校验码CRC(可以检错不能纠错)

~掌握模2除法(进行异或操作)

(3)海明校验码

~m个数据+k个校验位=m+k个码字

公式:m+k+1<2^k