- 1使用CSS3 + Vue3 + js-tool-big-box工具,实现炫酷五一倒计时动效_vue3倒计时插件

- 2人工智能五子棋实现原理

- 3ChromaDB:开启AI原生嵌入式数据库的新纪元_chromadb数据库

- 4面试如何进行自我介绍_少儿编程面试自我介绍

- 5数据结构的选择-“数组、链表、树、哈希表”选哪个(性能比较)?

- 6Mybatis-plus-join连表查询_mybatisplus 连表查询

- 72021年软考信息安全工程师下午真题(考生回忆版)_软考信息安全工程师真题

- 8Elasticsearch Search API之(Request Body Search 查询主体)_collapsebuilder.setinnerhits

- 9使用frps建立内网穿透从而实现外界连接内网电脑的全教程

- 10ElasticSearch7 使用总结_elasticsearch 7

FPGA设计时序约束_三种工况对时序约束的影响

赞

踩

原博客地址:https://blog.csdn.net/u012176730/article/details/54412323

FPGA方面的心得,将会由以下几个方面进行总结:

1. FPGA时序约束以及高速ADC约束实例

2. TDC进位延时链设计以及研究

3. TDC的精度以及自动校正算法的实现

STA:Static Timing Analysis

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的,其作用是:

1. 帮助分析和验证一个FPGA设计的时序是否符合要求;

2. 指导fitter(布线综合器)布局布线出符合要求的结果;

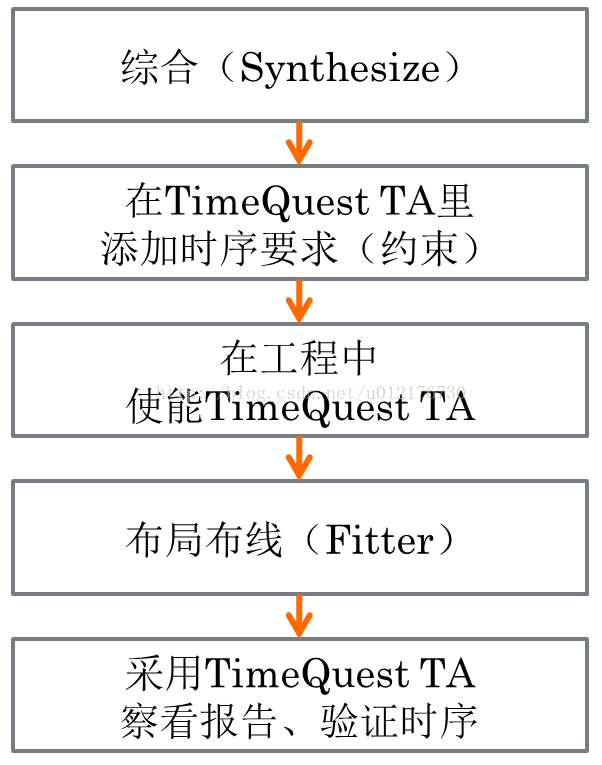

简单地说,静态时序分析(STA)告诉我们电路的实际表现如何,而提供约束(SDC文件,即上面的要求)来告诉分析工具我们希望电路的表现应该是怎样。Quartus II自带的STA工具TimeQuest TA在整个FPGA设计过程中的使用流程如下图所示:

图 1 TimeQuest TA使用流程

简而言之,我们需要学会:

A. 正确理解时序,看背景知识介绍

B. 正确编写SDC文件,以及利用TimeQuest TA生成SDC约束命令,SDC介绍

C. 利用TimeQuest TA来查看和验证时序

一、 背景知识介绍:

1.1 启动沿(launch)和锁存沿(latch):

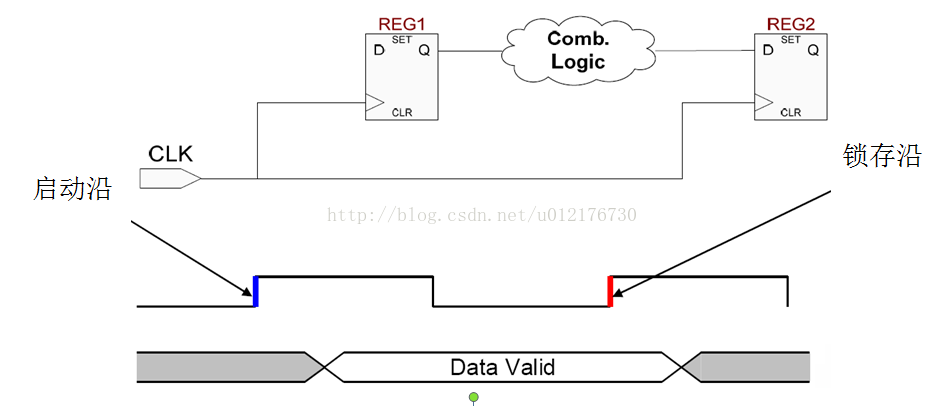

图 2 启动沿和锁存沿

启动沿:数据被launch的时钟边沿;也就是说,每一个启动沿,一般都会产生一个新的数据!

锁存沿:数据被latch的时钟边沿;也就是说,每一个锁存沿,都会有一个新的数据被保存!

对于如上图所示的级联的寄存器电路而言(忽略上一级触发器输出到下一级触发器输入之间的逻辑关系),一般蓝色的上升沿作为第一个触发器的启动沿,而红色的上升沿(一般都是紧跟着启动沿后的有效边沿)。所以说:蓝色的启动沿之后由REG1输出有效数据,并在红色的边沿被锁存进REG2并输出到下级。

1.2 建立(setup)和保持(hold)时间

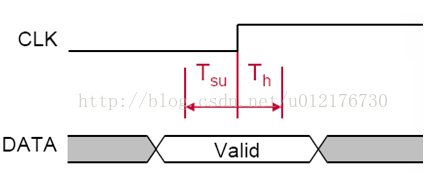

图 3 建立和保持时间

上述的锁存沿会将数据保存下来,但是必须要满足一定的条件:

建立时间Tsu:在时钟有效沿之前,数据必须保持稳定的最小时间;

保持时间Th:在时钟有效沿之后,数据必须保持稳定的最小时间;

这就相当于一个窗口时间,在有效边沿的窗口时间内,数据必须保持稳定;这里的时钟信号时序和数据信号时序,都是寄存器实际感受到的时序;什么事实际感受到的,下面会继续分析;

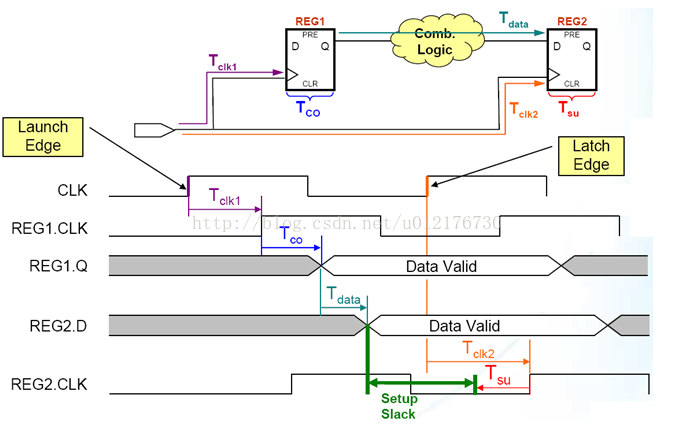

1.3 数据到达时间(DAT:data arrival time)

所有的信号在FPGA内部传播都会有延时,包括时钟信号、数据信号(实际上不该如此可以的区分这两种信号,在一定条件下,这两个信号可能可以相互转换,这个是题外话了),也就是说,从信号的发出点到信号的接收点,会存在一个延时,这个延时可能是因为FPGA内部空间分布所致,也有可能是因为组合逻辑造成,这里不再深究;

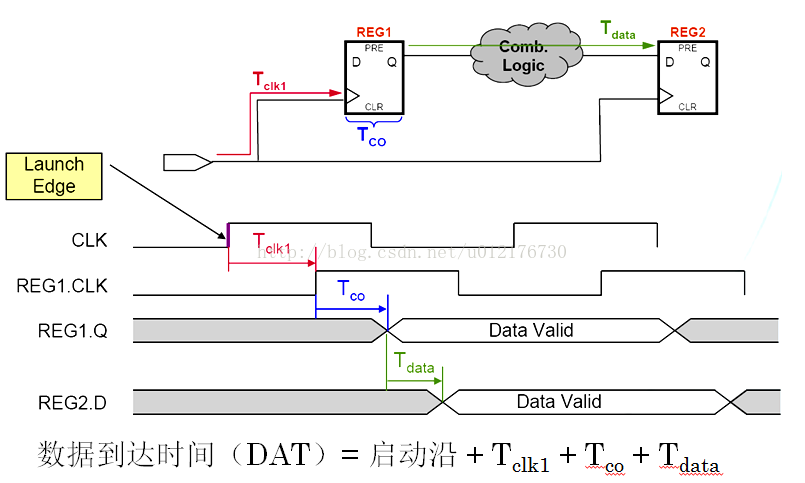

图 4 数据到达时间示意图

正如上图所示,在计算数据到达时间时,一般都会存在3个延时:

1. Tclk1:时钟信号从起点(一般是PLL输出或者时钟输入引脚)到达启动寄存器(或说启动触发器)的相应clk端口所耗的时间;假如CLK是由PLL发出的时钟信号(称之为源时钟),这个信号经过FPGA内部的“连线”最终来到了REG1(启动触发器)的clk端,所以此时在REG的clk1处也会有周期性的时钟信号REG1.CLK(如图所示);可以看到,此时的CLK(源时钟)和REG1.CLK实际上有个(相位差)时间差,这个时间差就是Tclk1;

2. Tco:启动寄存器内部延时,是寄存器REG1感受到有效的上升沿后,到数据真正从从REG1的Q输出之间延时;请注意:上述所谓的有效的上升沿,就是REG1.CLK,而不是CLK;所以实际的有效数据输出的时序如上图的REG1.Q;

3. Tdata:数据从上级寄存器输出Q(经过所有其他组合逻辑以及FPGA内部走线)到下级寄存器的数据输入D之间的延时;如图所示,数据从从REG1的Q流向了REG2的D,所以REG2.D实际感受到的数据时序是REG2.D;

假如将上图中的launch Edge作为时间0点,将一些列的延时累加,所得结果称之为数据到达时间,DAT:

DAT=启动沿+Tclk1+Tco+Tdata;

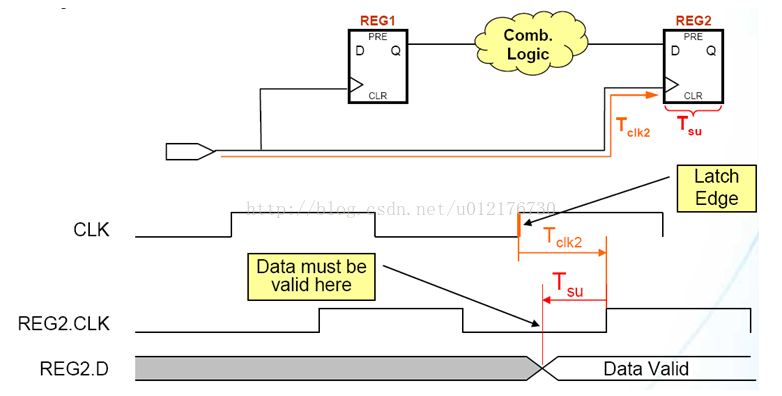

1.4 数据建立需要时间(DRTsu:data require time (setup))

图 5 数据建立需要时间

分析方法同上,需要计算数据建立时间,也需要两个延时:

1. Tclk2,不同于上述的Tclk1,这个延时是时钟从起点(一般是PLL或者时钟输入引脚)到锁存触发器之间的延时;如上图所示,REG2实际感受到的时钟来自于其本身的clk引脚,而不是源时钟CLK,他们之间存在一个延时,即Tclk2;所以REG2实际感受到的时钟,实际上是上图的REG2.CLK;

2. Tsu:上面分析过了,每一个数据被锁存都要满足建立时间和保持时间,Tsu就是建立时间,也就是在REG2实际感受到Latch Edge时,数据如果需要被正确锁存,就必须提前Tsu的时间来到REG2的D;

综合时钟走线延时Tclk2以及Tsu,我们得到了数据建立时间DRTsu:

DRTsu=锁存沿+Tclk2-Tsu。

也就是说在DRTsu时刻之前,数据必须已经有效且稳定

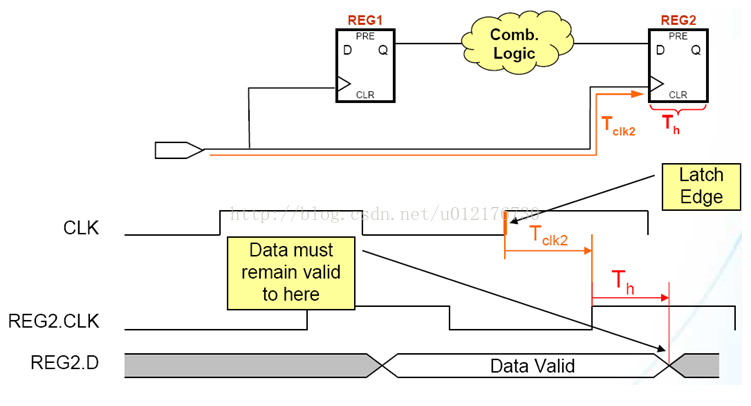

1.5 数据保持需要时间(DRTh:data require time (hold))

图 6 数据保持需要时间

即DRTh=锁存沿+Tclk2+Th;

也就是说,数据在DRTh时间之前必须保持住不变;

1.6 建立时间裕量(Setup Slack)

建立时间裕量指的是数据到达时间和数据建立需要时间之间的关系:

图 7 建立时间裕量

如上图所示,在0时刻(Launch edge),源时钟CLK说,“啊,我要产生一个新的数据”,但是这个命令(启动沿)并没有马上传达到REG1,而是有个延时Tclk1。所以在Tclk1时刻,REG1终于听到了(感受到了有效的时钟上升沿,就是启动沿)老大的命令,就开始准备,他憋了一会儿,又延时了Tco,终于产生了数据(REG1.Q上有了valid data);这个有效数据也是慢吞吞的来到了他的终点,又浪费了Tdata。最终在Tclk1+Tco+Tdata时间后,REG2得到了这个数据;别以为REG2得到这个数据就完事了,REG2也是个傲娇的娃,怎么个傲娇法,下面继续分析;老大CLK在0时刻发送了启动沿之后,休息了一个时钟周期,在Latch edge时突然想起来,刚才让REG1发出的数据,REG2要接受啊,不然就浪费了,于是乎他又对REG2下达了命令,新数据要来了,准备好接受!但是这个命令也不是马上就到了REG2的耳中,而是经过了Tclk2的时间。等到REG2接收到命令后(实际感受到了有效的Latch Edge),他就看看自己家门口没有数据已经来了(检查REG2.D是否有数据),同时要看看这个数据是不是符合他的胃口的(满足锁存的条件),他要求数据必须在他接收到老大命令的时候已经等了Tsu时间(数据建立时间),由要求这个数据在他家门口不能早退,必要再保持Th时间(数据保持),如果都满足了,REG2就开心的接受了这个数据,反之,他就会觉得,REG1准备的数据太懒惰了(没有提前Tsu时间到达),又或者性子太急(没有多逗留th),一概不收!

所以这里涉及到两个要求,第一个就是建立时间裕量:

正如上图所示Setup Slack=DRTsu-DAT。

如果Setup Slack为正,则说明数据在规定的时间内达到了目标。反之,则认为数据并没有在规定的时间达到目标,此时REG2锁存的数据很有可能是亚稳态;

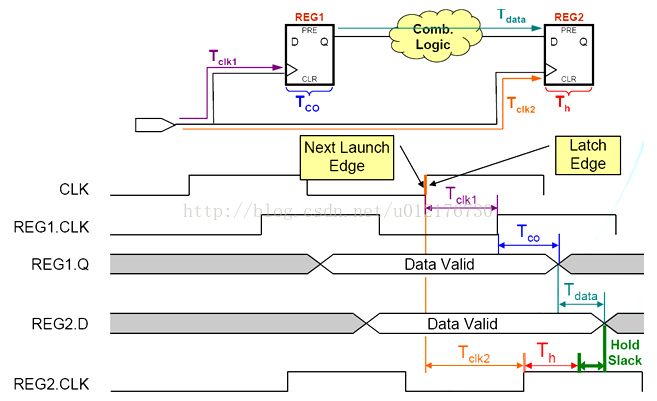

1.7 保持时间裕量(hold slack)

图 8保持时间裕量

如上所述,hold slack = DAT – DRTh

如果为正,则认为数据在被锁存的时候有足够多的稳定时间,是有效的。反之则认为数据有误或者数据可能是亚稳态;

小结:

理解了上面的7个概念,就明白了:如果时钟频率过快或者数据延时太大,都会导致错误的时序。在FPGA内部寄存器到内部寄存器之间,所有的延时都是建立在时序模型上的,如slow和fast,这些模型从两个极端工作情况来分析FPGA能否正常工作;只要满足这两个工况,则FPGA在其他环境下都能满足时序!