热门标签

热门文章

- 1一款专业的Mac系统清理软件CleanMyMac X 4.15.1破解版_cleanmymac 4.15.1

- 2java8新特性(2)-Lambda表达式_lambo表达式

- 32020-10-11《多重背包 单调队列优化》_第1行有2个整数n,m,表示物品的种类和背包的容积; 第2-n+1行,每行有3个整数vi,wi,p

- 4【LeetCode热题100】【技巧】下一个排列

- 5Altas 200 DK环境配置_atlas200dk

- 6宝塔面板mysql怎么用navicat 连接数据库呢,详细步骤_宝塔进服务器数据库

- 7简表报表配置以及ftl文件的一些功能_ftl文件中columnwidth设置

- 8什么?JS 异步原来还能这么处理?

- 9蓝桥杯单元测试专项练习Java版(单元测试4)(修正版)_请使用基本路径覆盖法 + 简单循环覆盖法的标准规则,对被测源代码 goods、goodsser

- 10git submodule 如何同步更新_git submodule update

当前位置: article > 正文

Vitis AI(03) Vivado Flow_project is an extensible vitis platform

作者:我家小花儿 | 2024-04-26 08:25:53

赞

踩

project is an extensible vitis platform

从本文开始,将正式介绍VitisAI的工作流程。第一个流程就是Vivado Flow,在Vivado开发环境中创建一个硬件平台,为后续的PetaLinux和Vitis提供基础。Vivado中的大部分的内容都是在Block Design中完成的,核心目标是创建一个Zynq UltraScale MPSoC的运行硬件环境,以及为DPU的正常运行提供硬件支持。这里需要注意,较老版本的VitisAI教程中,需要在Vivado中导入DPU的IP核,这种做法已经成为历史,本文介绍的流程中,在Vivado中是不需要导入DPU IP核的,只是对DPU运行环境进行支持,例如中断、时钟等

创建Vivado工程

打开vivado

- source /opt/pkg/xilinx/Vivado/2021.1/settings64.sh

- vivado

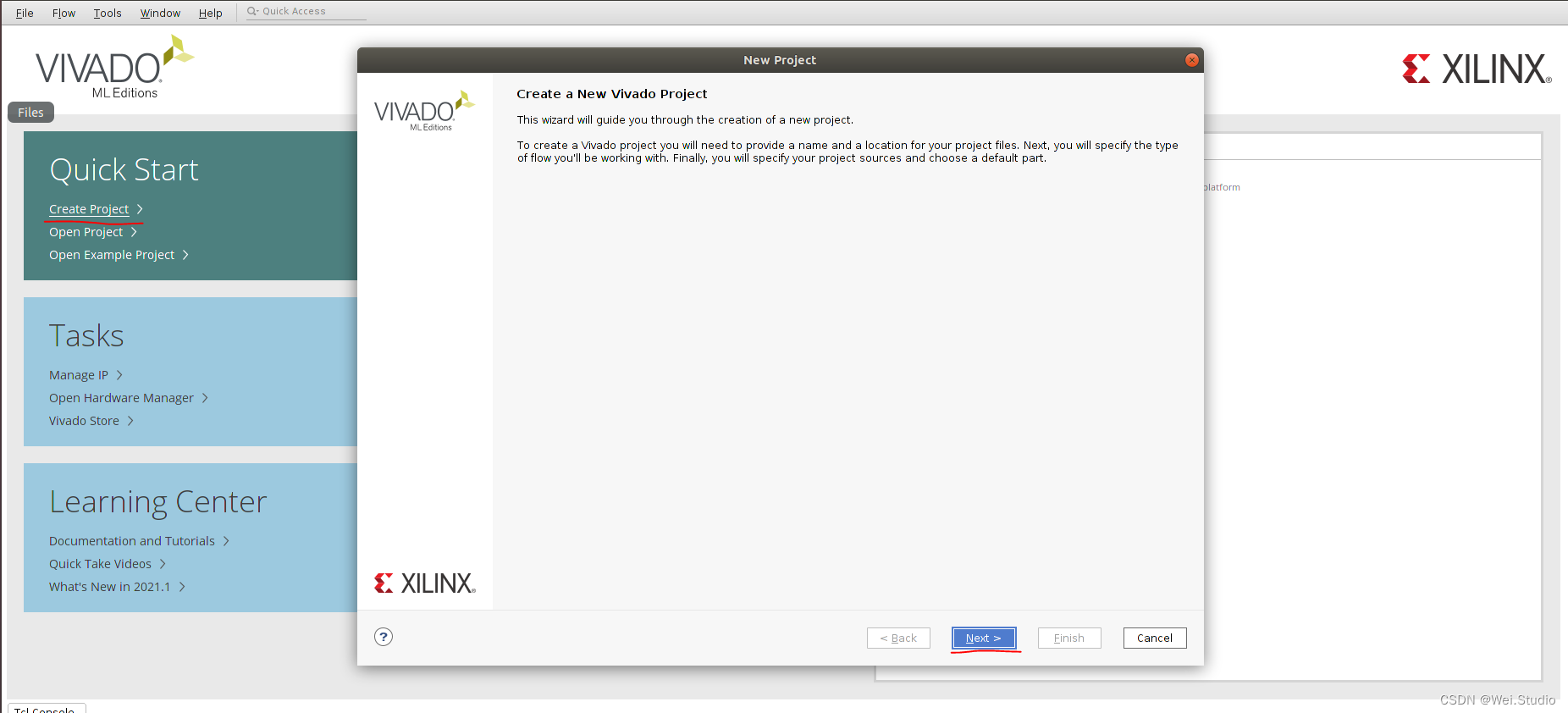

vivado打开后,点击Create Project->Next

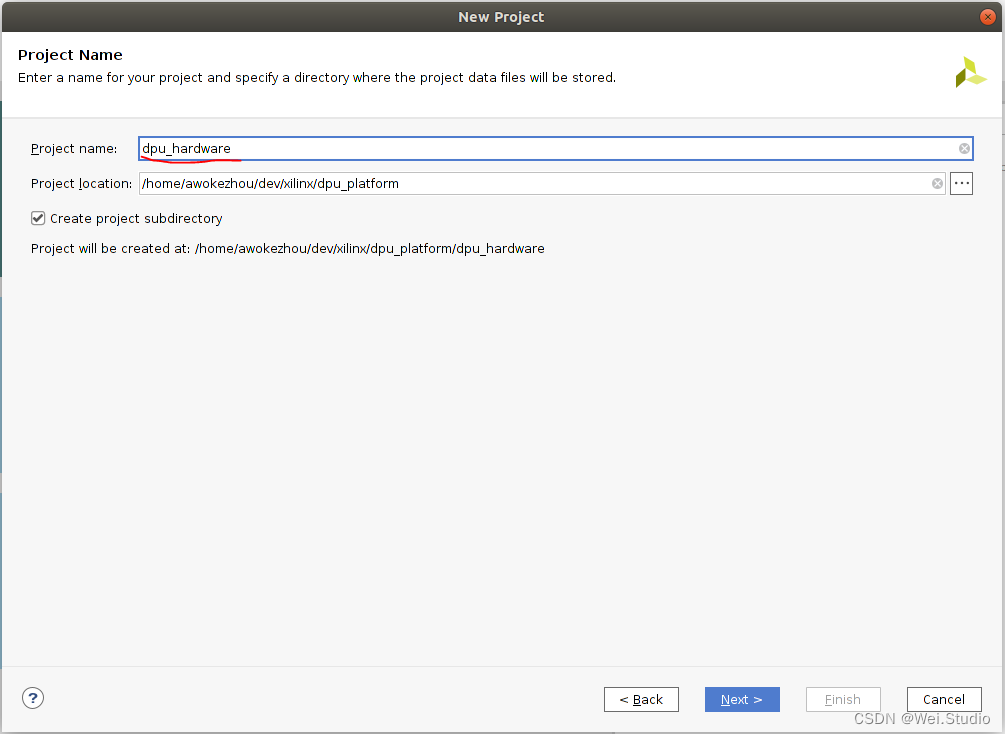

输入项目名称,这里我输入的是”dpu_hardware”,点击Next

在Project Type页面中选中RTL Project,并选中Project is an extensible Vitis platform,点击Next

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/489963

推荐阅读

相关标签