- 1Flink DataSource介绍

- 2【VUE项目实战】16、主页Header和左侧菜单栏布局_vue3实现header和侧边菜单栏

- 3GLM-4

- 4二叉树的创建和基本操作(详解)

- 5Java集成ElasticSearch及配置类工具类整理_java es配置和util

- 6SOA方法—商业银行应用架构变革之路_soa银行攻略

- 7面试AI岗,为什么我在100人中拿到了唯一年薪70万的offer?

- 8数据中心液冷及冷却液行业分析:算力提升驱动,氟化液迎来机遇

- 9Jenkins配置gitlab仓库时,提示“Failed to connect to repository : returned status code 128”_repo: error: "git" failed with exit status 128

- 10@PostMapping注解解析

从零开始利用MATLAB进行FPGA设计(四)生成优化HDL代码_matlab程序写到fpga

赞

踩

文章灵感来源于MATLAB官方免费教程:HDL Coder Self-Guided Tutorial

考虑到MATLAB官网的英文看着慢,再加上视频讲解老印浓浓的咖喱味,我决定记录利用MATLAB&Simulink&SystemGenerator进行FPGA数字信号处理的学习过程。

往期回顾:

从零开始利用MATLAB进行FPGA设计(二)用于HDL代码生成的Simulink模型并用于流水线设计

从零开始利用MATLAB进行FPGA设计(三)将Simulink模型转化为定点数据类型

目录

2.生成HDL代码(HDL Workflow Advisor)

1.检查模型在代码生成方面的兼容性

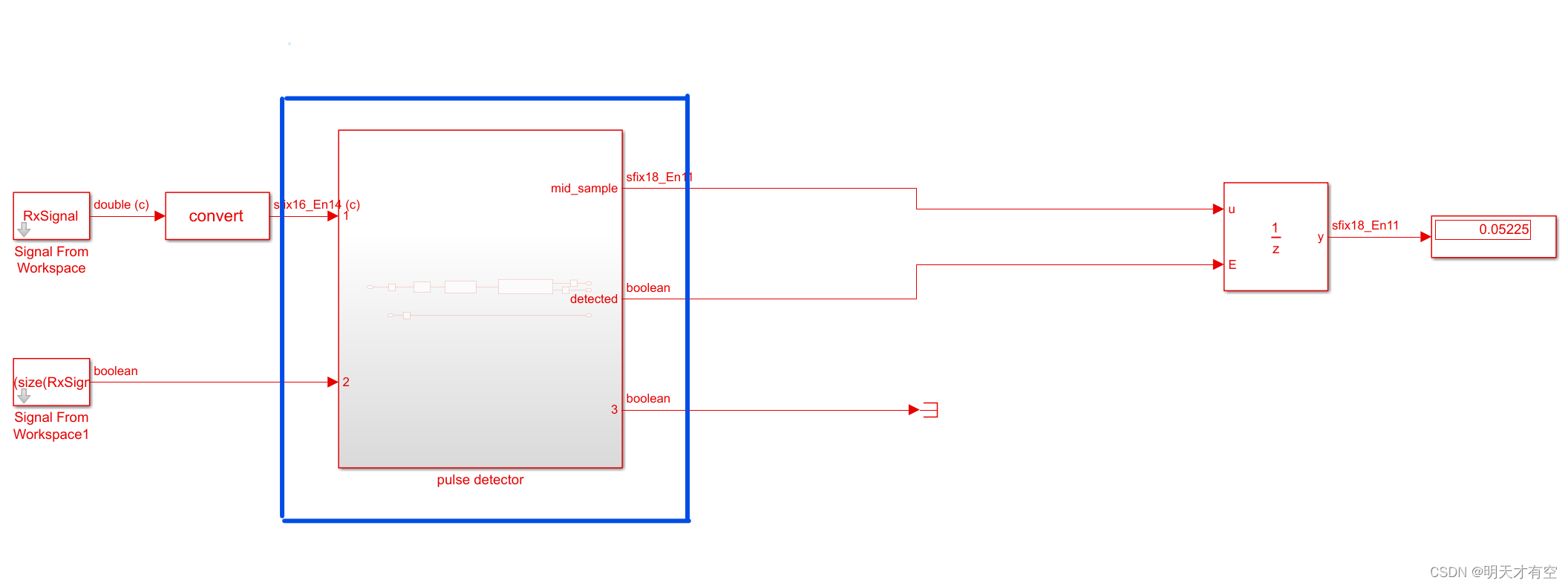

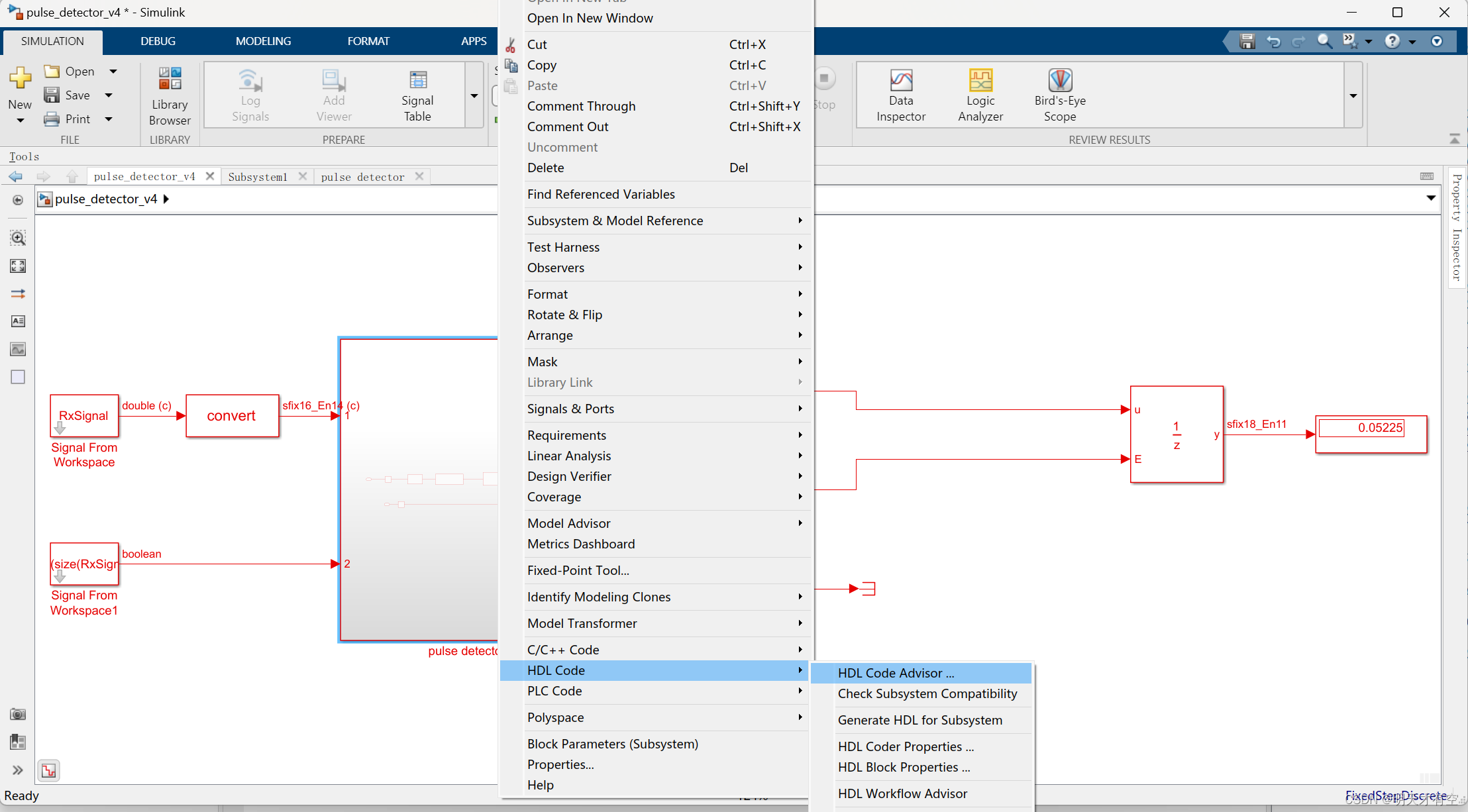

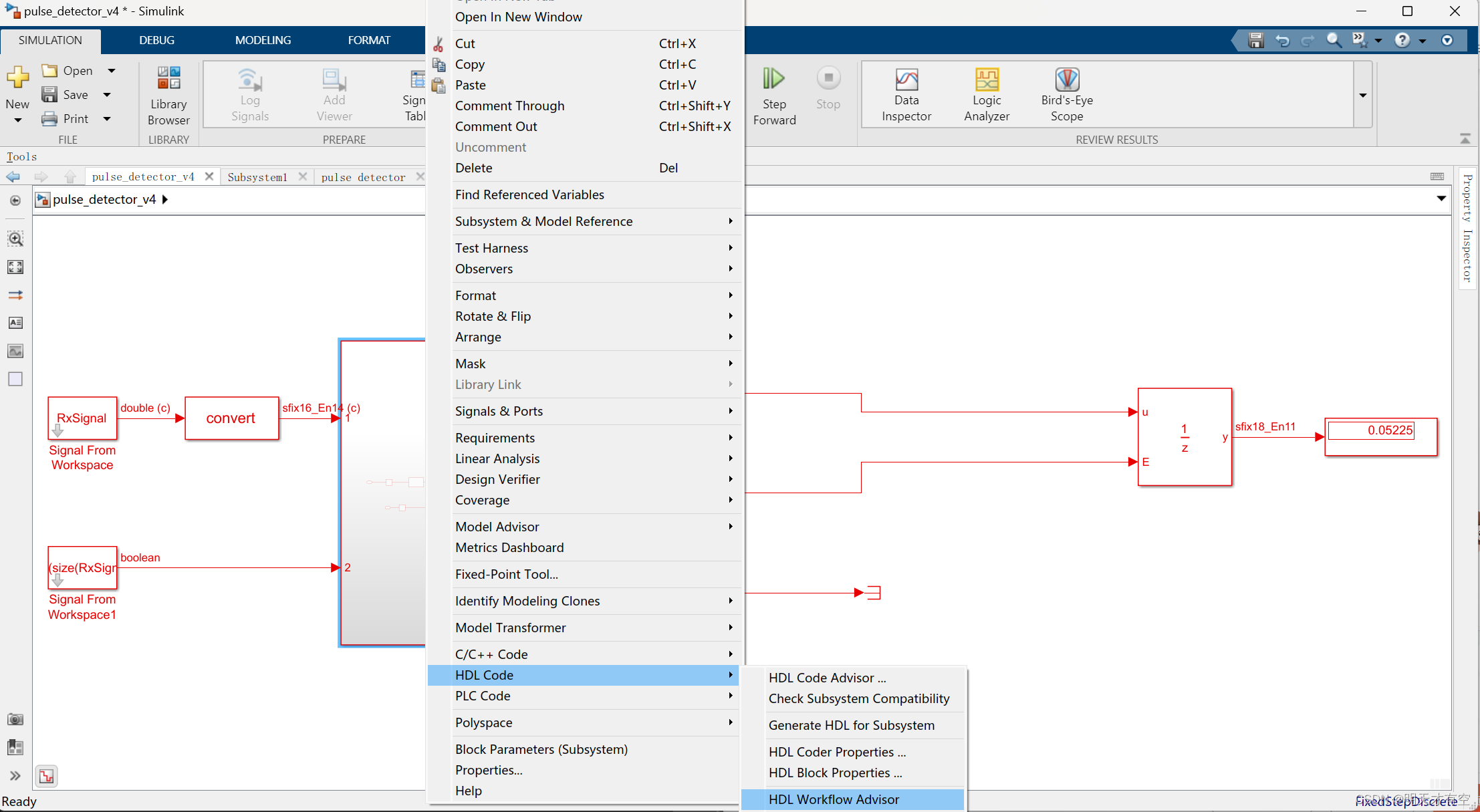

本章内容将要生成的是前文模型中的脉冲检测子系统。右击模块,在HDL Code选项下选择HDL Code Advisor

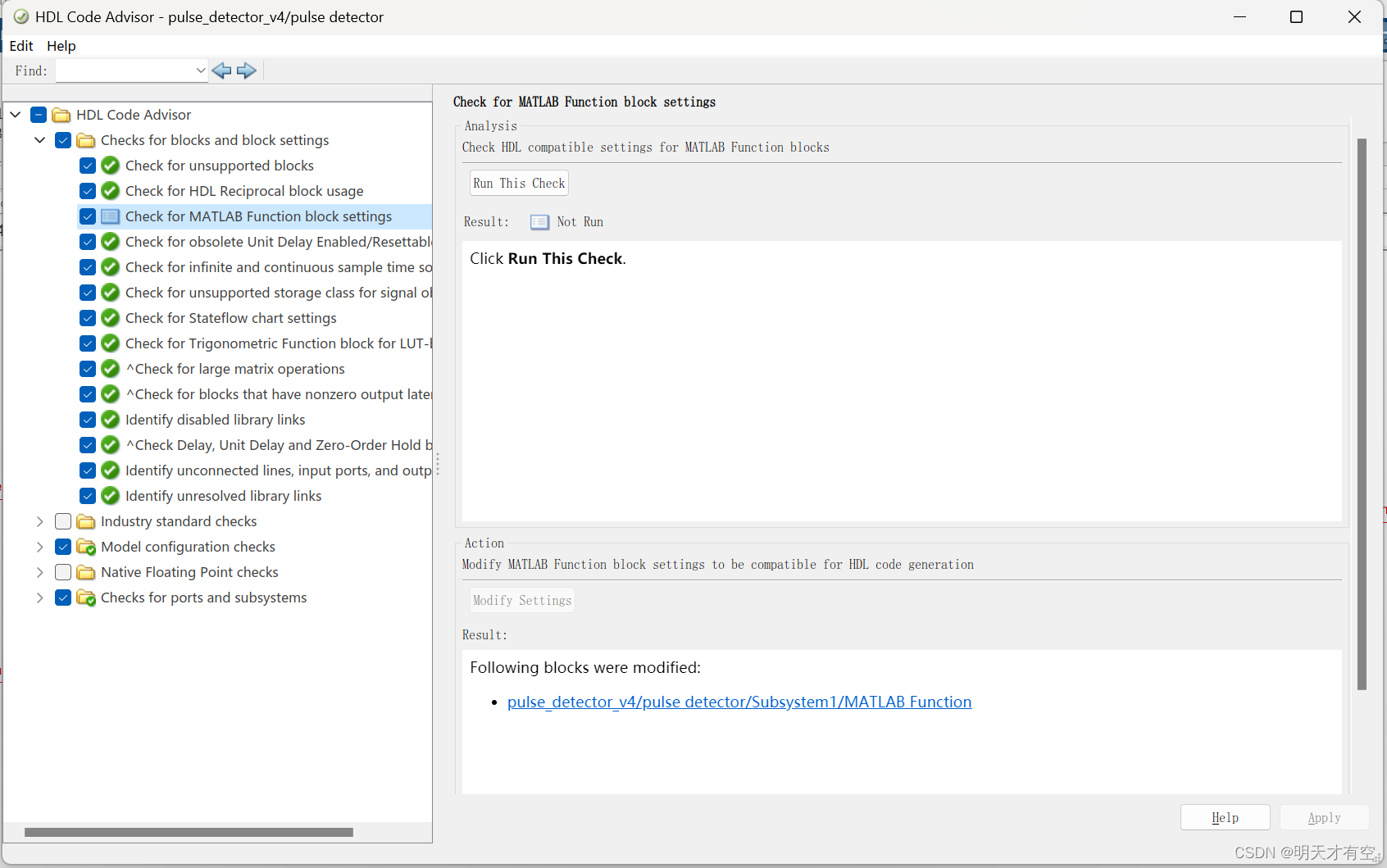

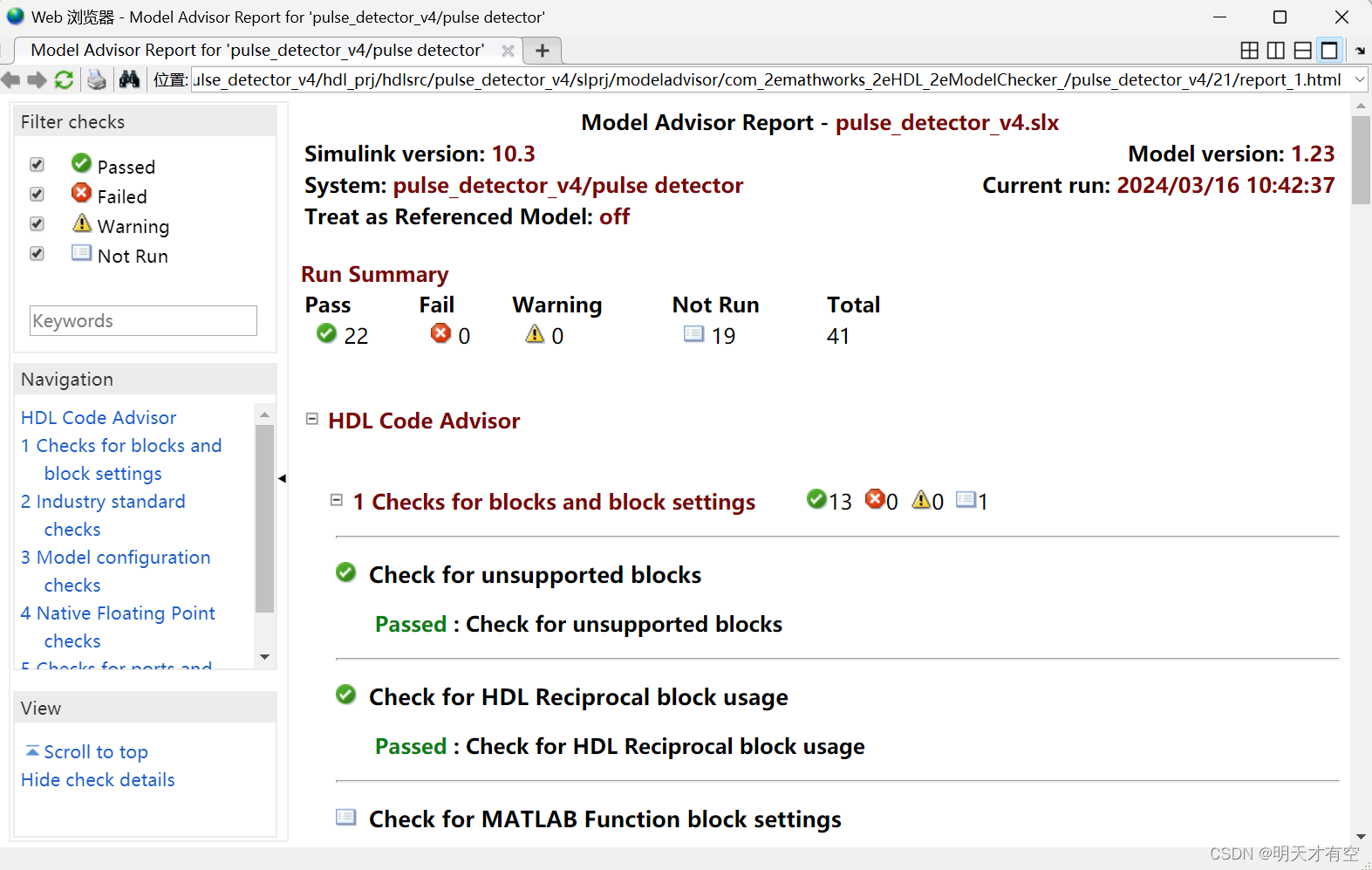

该功能可确保子系统中使用的模块兼容HDL,并确保这些模块的设置、端口和配置不会产生低效的硬件,浮点检查和行业标准检查不适用于本例,所以进行忽略。运行选定的检查后,不符合的状态将显示为警告或失败:

警告可以通过报告的连接直接跳转,可以使用“Modify Settings”自动更正警告。

在HTML报告中会显示每次运行模型检查器的结果和时间戳。

2.生成HDL代码(HDL Workflow Advisor)

要综合生成HDL代码,需要使用vivado。在命令行中使用:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','Xilinx bin的位置')将综合工具写入MATLAB系统路径。

右键单击子系统,启动HDL Workflow Advisor:

HDL Workflow Advisor会一步一步完成生成HDL代码的各个阶段最终完成FPGA设计。

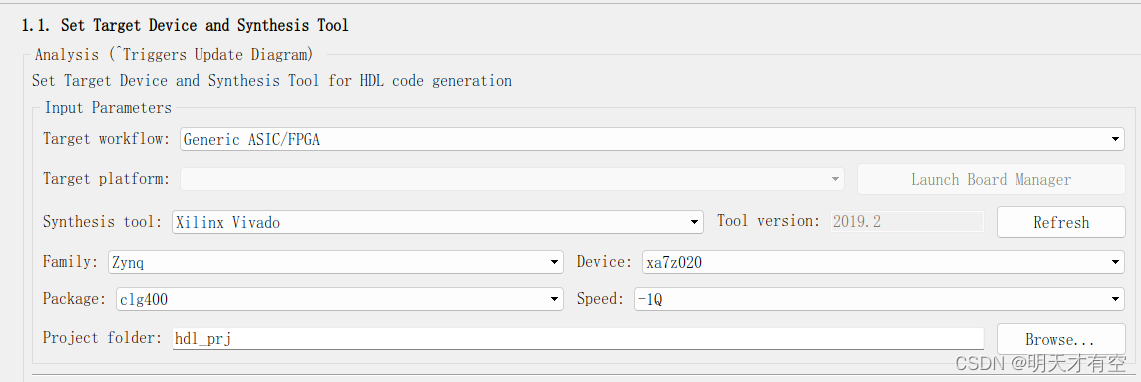

首先进行FPGA的硬件信息定义:

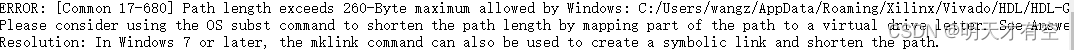

本文使用的是ZYNQ7000系列芯片。需要注意的是,创建的文件目录总长度不能超过80个字母,否则在后续生成中非常容易出错(若在MATLAB的默认目录下进行创建很容易出现这个问题)。

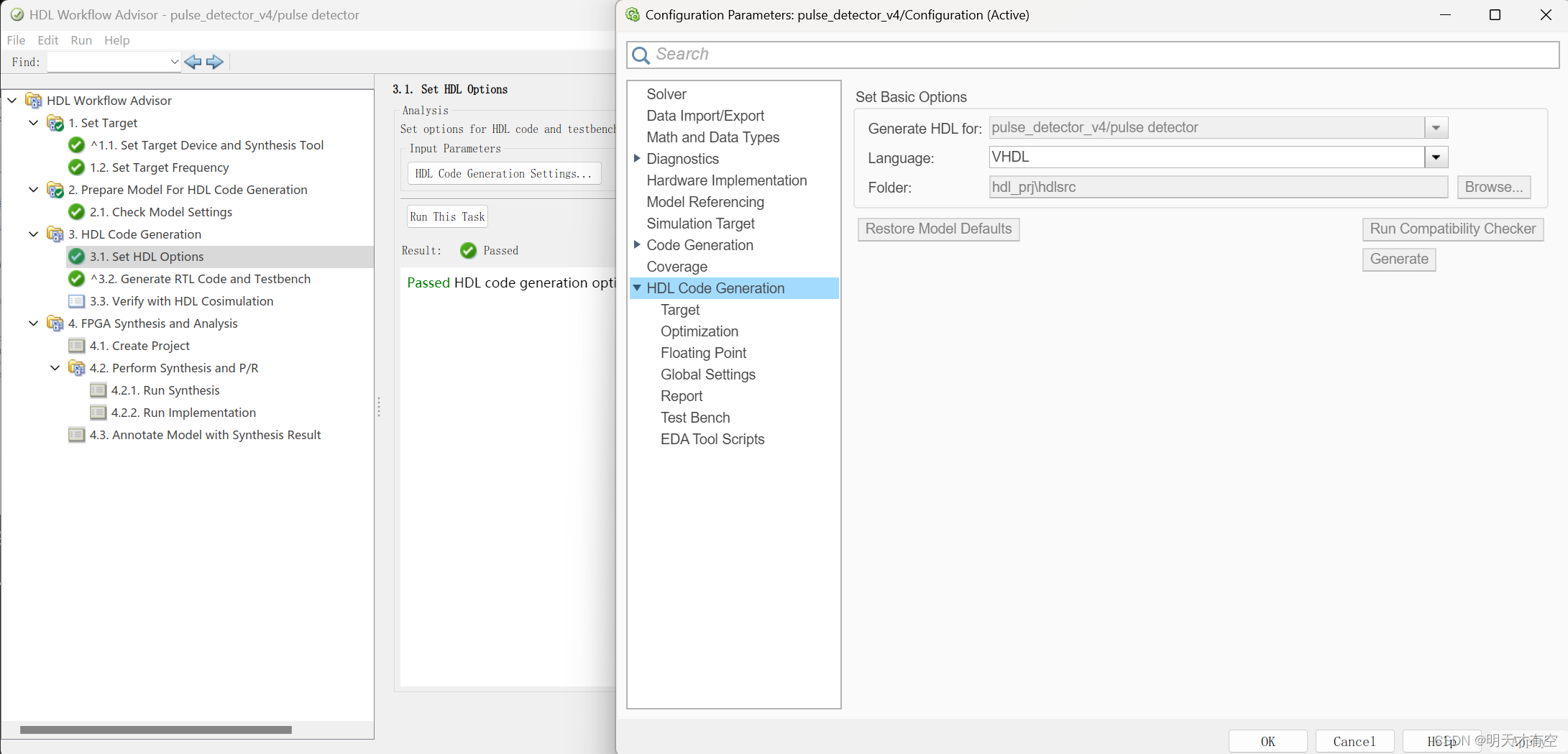

与全局设置和报告生成有关的设置在3.1菜单中点击“HDL Code Generation Settings”:

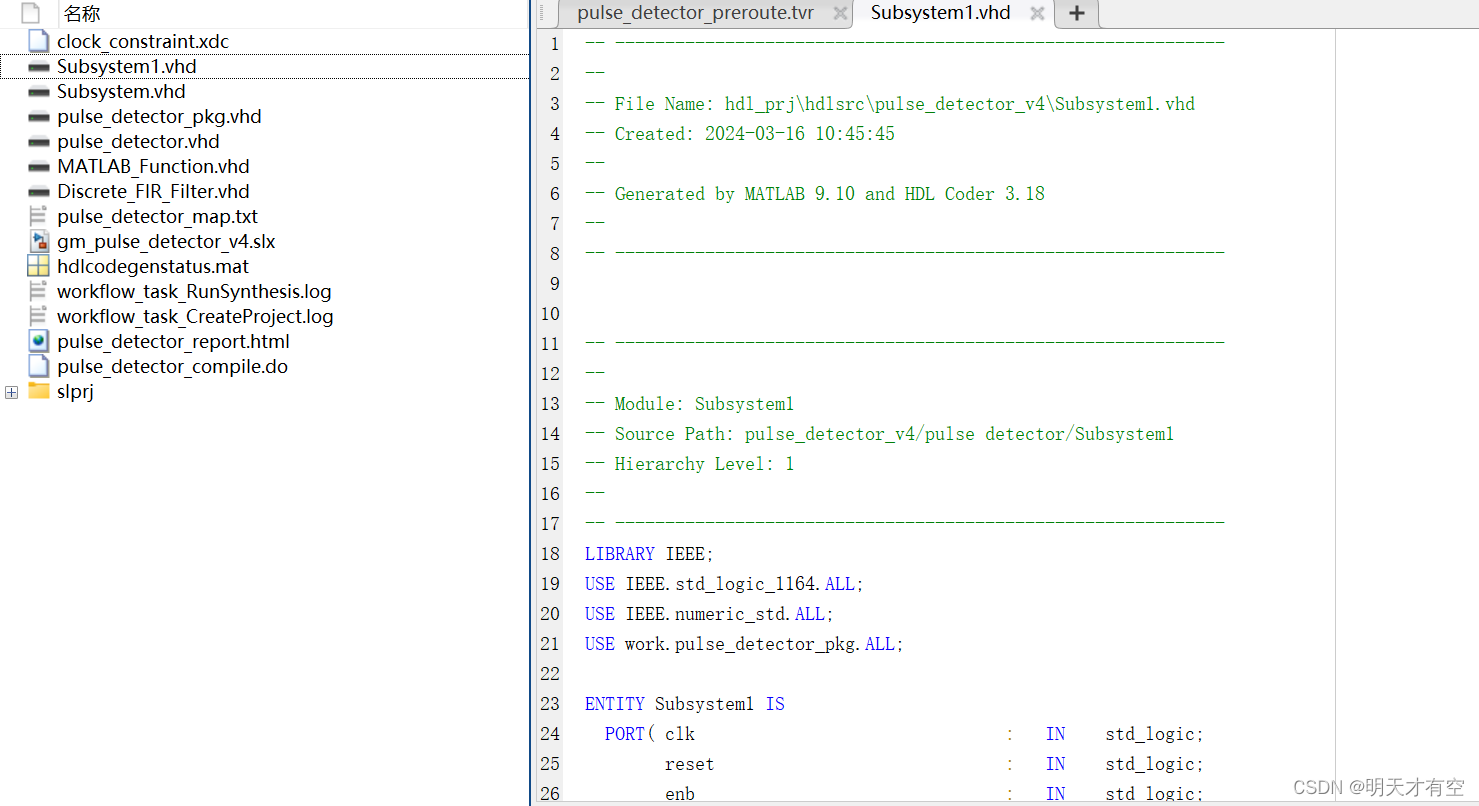

全部设置完毕后运行至任务3.2以启动HDL代码的生成。任务完成后即可看到生成的HDL代码:

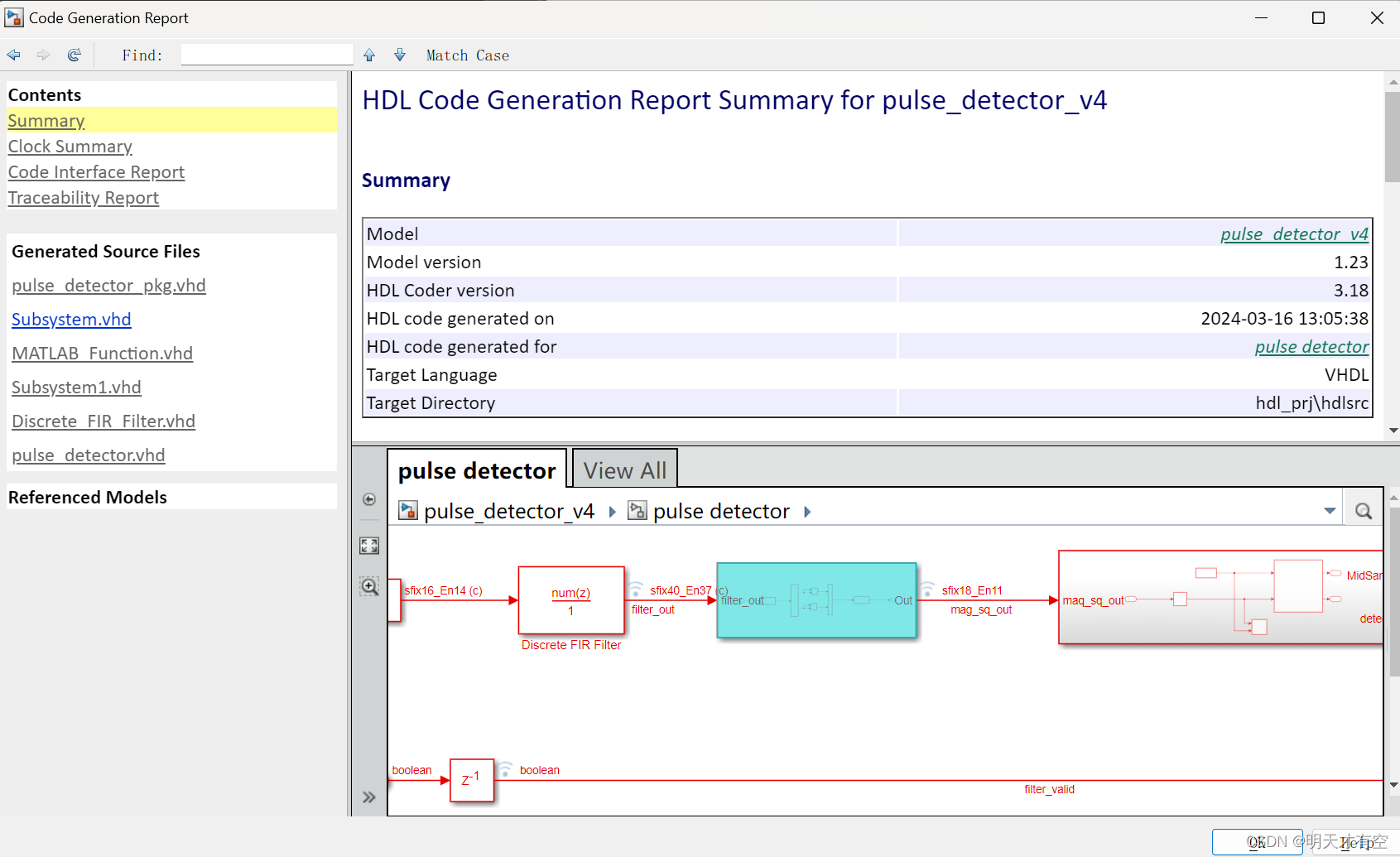

代码生成报告中包含了资源利用率估算值和优化选项:

要进行仿真操作,必须安装ModelSim。

生成HDL代码后,可以继续在Workflow Advisor中创建FPGA综合工程,也可以在Vivado中继续设计。

若在生成过程中报错找不到Vivado中的文件,可以尝试打开Vivado进行生成。