- 1C语言自定义类型详解(保姆级教学)_c定义类型名称

- 2home brew 安装mysql_Mac 安装MySQL(Homebrew)

- 3mpu6050和mpu9250姿态解算_mpu9250 mpu6050

- 4编译报错:The project is using an incompatible version_the project is using an incompatible version (agp

- 5部署Nginx Web服务器_nginx site-enable

- 6CSDN的崛起与发展:共享技术,连接未来_csdn谁创办的

- 7如何使用 XGBoost 对时序数据进行精准预测?_xgboost时间序列预测模型

- 8大数据分析R中泊松回归模型实例_泊松数据分析

- 9【重磅开源】MapleBoot项目启动部署

- 10Apache Atlas技术实践V1.0_atlas 二次开发

FPGA HDMI IP之DDC(本质I2C协议)通道学习_kvdat

赞

踩

目的:

使用KingstVIS逻辑分析仪软件分析HDMI的DDC通道传输的SCDC数据(遵循I2C协议),同时学习了解SCDC的寄存器与I2C通信协议。

部分英文缩写:

HDMI High Definition Multi-media Interface 高清多媒体接口 DDC Display Data Channel 显示数据通道 SCDC Status and Control Data Channel 状态和控制数据通道

一、资源:

参看附件:FPGA HDMI IP之DDC_I2C_SCDC协议.zip

解压缩后内容如下:

1.1 HDMI_2.0_协议.pdf

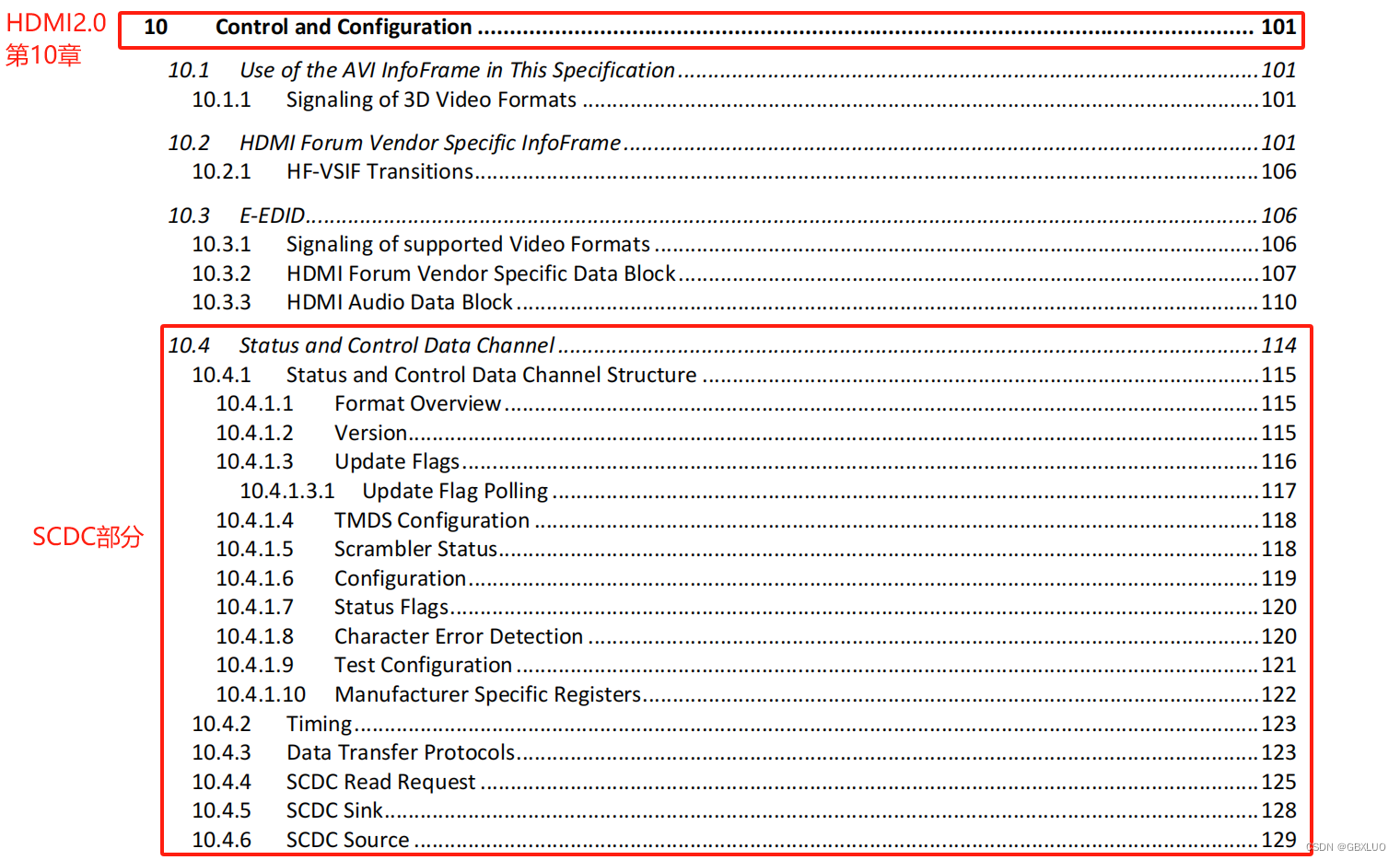

SCDC学习内容参考HDMI2.0第10章,如下图:

1.2 HDMI_DDC协议解读.kvdat

附件HDMI_DDC协议解读.kvdat是通过逻辑分析仪抓取的一次HDMI DDC通道通信的数据,仅供学习HDMI SCDC使用。

全部内容如下图所示:

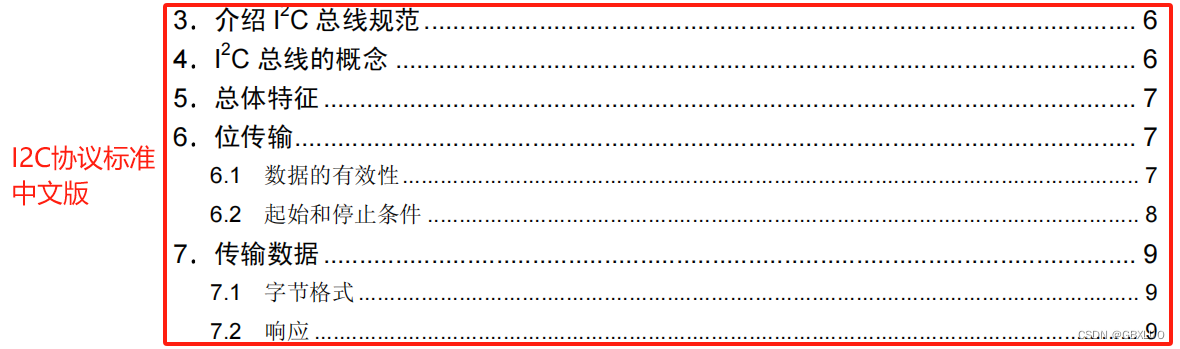

1.3 I2C协议标准中文版

1.4 KingstVIS逻辑分析仪软件:

用于打开HDMI_DDC协议解读.kvdat数据进行分析学习。

二、DDC通道遵循的I2C协议

2.1 I2C总体特征

2.1.1 I2C通信速率

总线上的数据传输速率有三个标准:标准模式、快速模式与高速模式。

| I2C总线模式 | 通信速率 |

| 标准模式 | 100kbit/s |

| 快速模式 | 400kbit/s |

| 高速模式 | 3.4Mbit/s |

2.1.2 I2C总线能支持的IC接口数量

注意:

连接到总线的I2C接口数量只由总线电容是400pF的限制决定

2.1.3 其他补充

- SDA和SCL都是双向线路

- SDA和SCL都通过一个电流源或上拉电阻连接到正的电源电压,因此当总线空闲时这两条线路都是高电平

- 连接到总线的器件输出级必须是漏极开路或集电极开路才能执行线与的功能

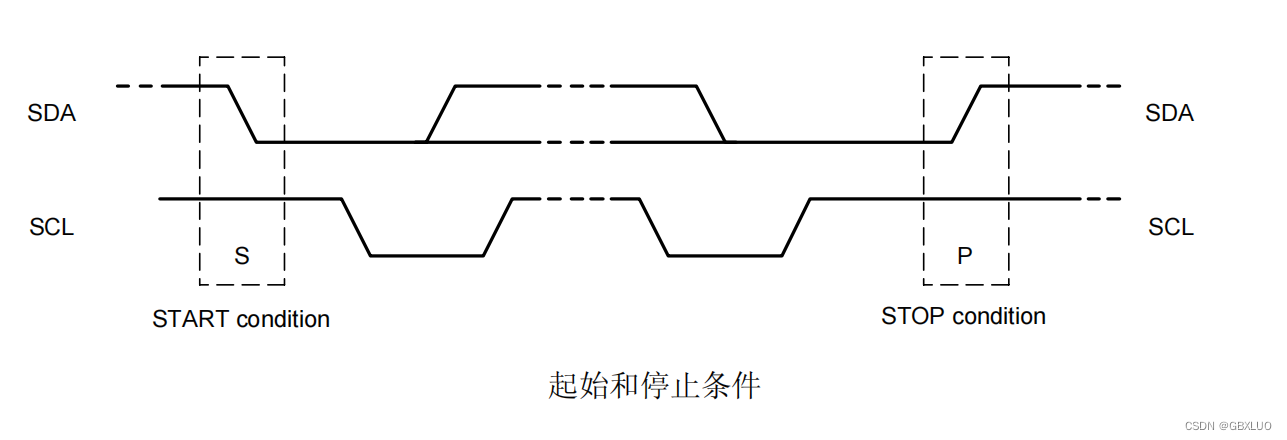

2.2 起始和停止条件

如上图所示,可以看到起始条件和停止条件:

起始条件:

SCL高电平期间SDA由高电平向低电平切换

停止条件:

SCL高电平期间SDA由低电平向高电平切换

2.3 传输数据

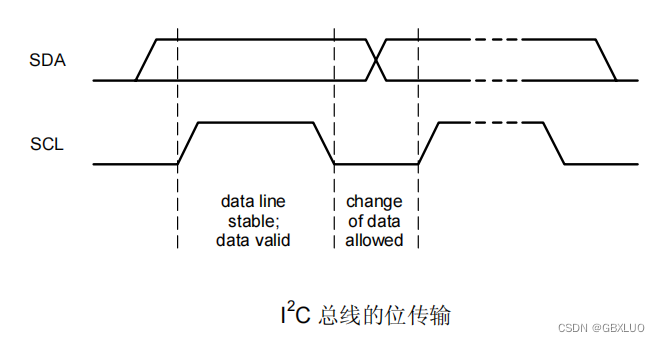

2.3.1 传输SDA数据的有效性

SDA数据的传输需要遵循两个基本约束:

SDA 必须在SCL的高电平周期保持稳定

SDA只能在 SCL的低电平周期进行高低电平转换

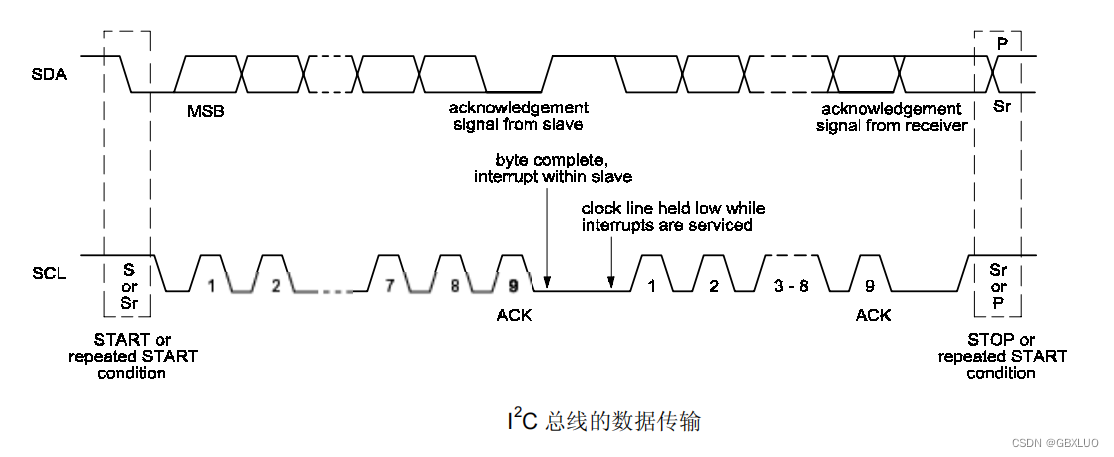

2.3.2 字节格式

- 发送到 SDA 线上的每个字节必须为 8 位;

- 首先传输的是数据的最高位MSB;

- 每次传输发送的字节数量不受限制;

- 每个字节后必须跟一个响应位;

2.3.3 响应ACK

- 响应ACK时钟脉冲由主机Master产生;

- 在响应ACK的时钟脉冲高电平期间,发送器(Master/Slave都可以是发送器)释放 SDA 线为高电平;

- 在响应ACK的时钟脉冲高电平期间,接收器必须将 SDA 线拉低,使SDA在这个时应的时钟脉冲的高电平期间保持稳定的低电平;

- 非响应NACK就是在响应的时钟脉冲高电平期间,接收器没有将 SDA 线拉低

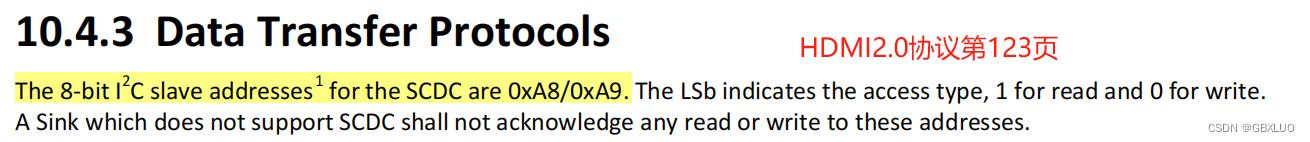

三、DDC数据传输协议:

HDMI2.0明确规定从机(Slave)地址为0xA8/0xA9:

| 十六进制 | 二进制 | 意思 |

| 0xA8 | 1010 1000 | Master写 |

| 0xA9 | 1010 1001 | Master读 |

数据/地址Byte是左高右低,发送顺序是高位先发送:

高7位对应Slave地址位为:0x54=0b101_0100

最低位代表Master读写位:

最低位为0,代表Master接下来要写数据:0xA8=0b1010_1000

最低位为1,代表Master接下来要读数据:0xA9=0b1010_1001

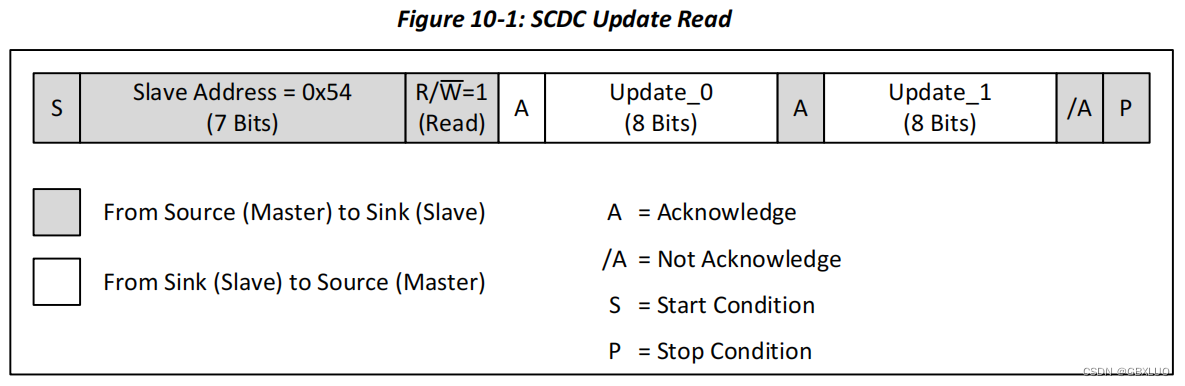

3.1 SCDC Update Read模式

SCDC Update Read作用:在Source读取更新标志时最小化消息的长度。

In this mode, the 8-bit I 2 C address 0xA9 is used without a repeated Start and reads commence from offset 0x10, corresponding of the UPDATE_0 sub-address.

暂时没用到~

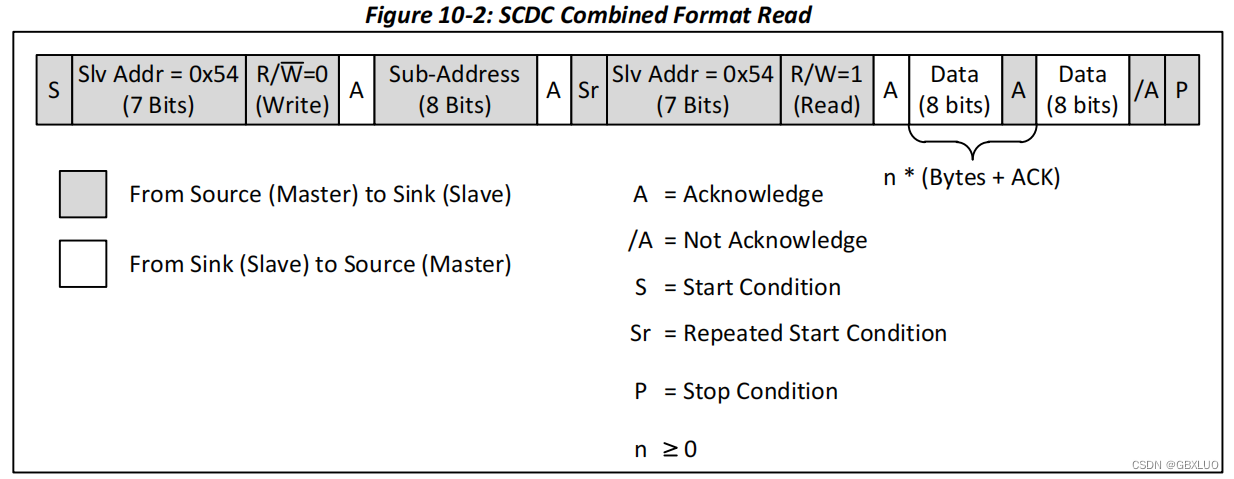

3.2 SCDC Combined Format Read模式

SCDC Combined Format Read模式支持连续读多个Bytes数据。

协议如下:

Master端使用组合格式读取,先是0xA8表示写入接下来的一个子地址(表示偏移量),然后是重复START条件,最后0xA9表示读取接下来的数据,可以是n个。

所有实现SCDC的HDMI sink都应该支持多字节读取,并自动增加偏移量。

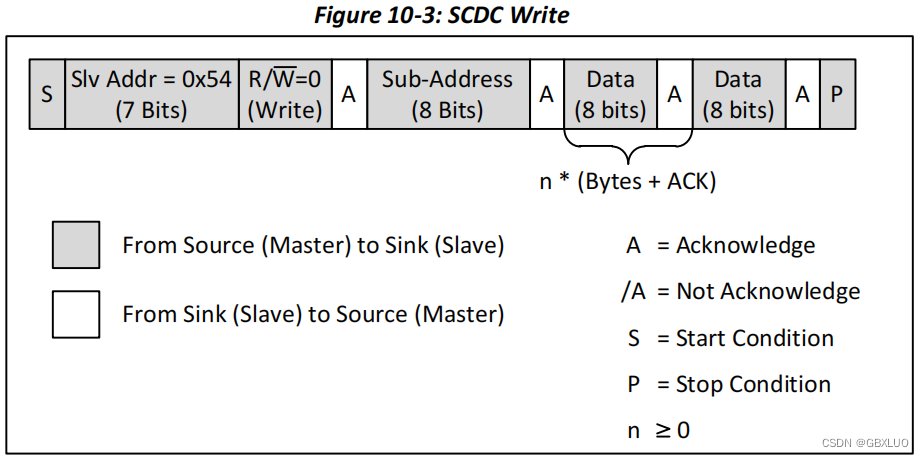

3.3 SCDC Write模式

SCDC Write模式支持写入多Byte数据。

Master端写模式,先是0xA8表示写入接下来的一个子地址(表示偏移量),接着读取接下来的n个数据,并自动增加偏移量。

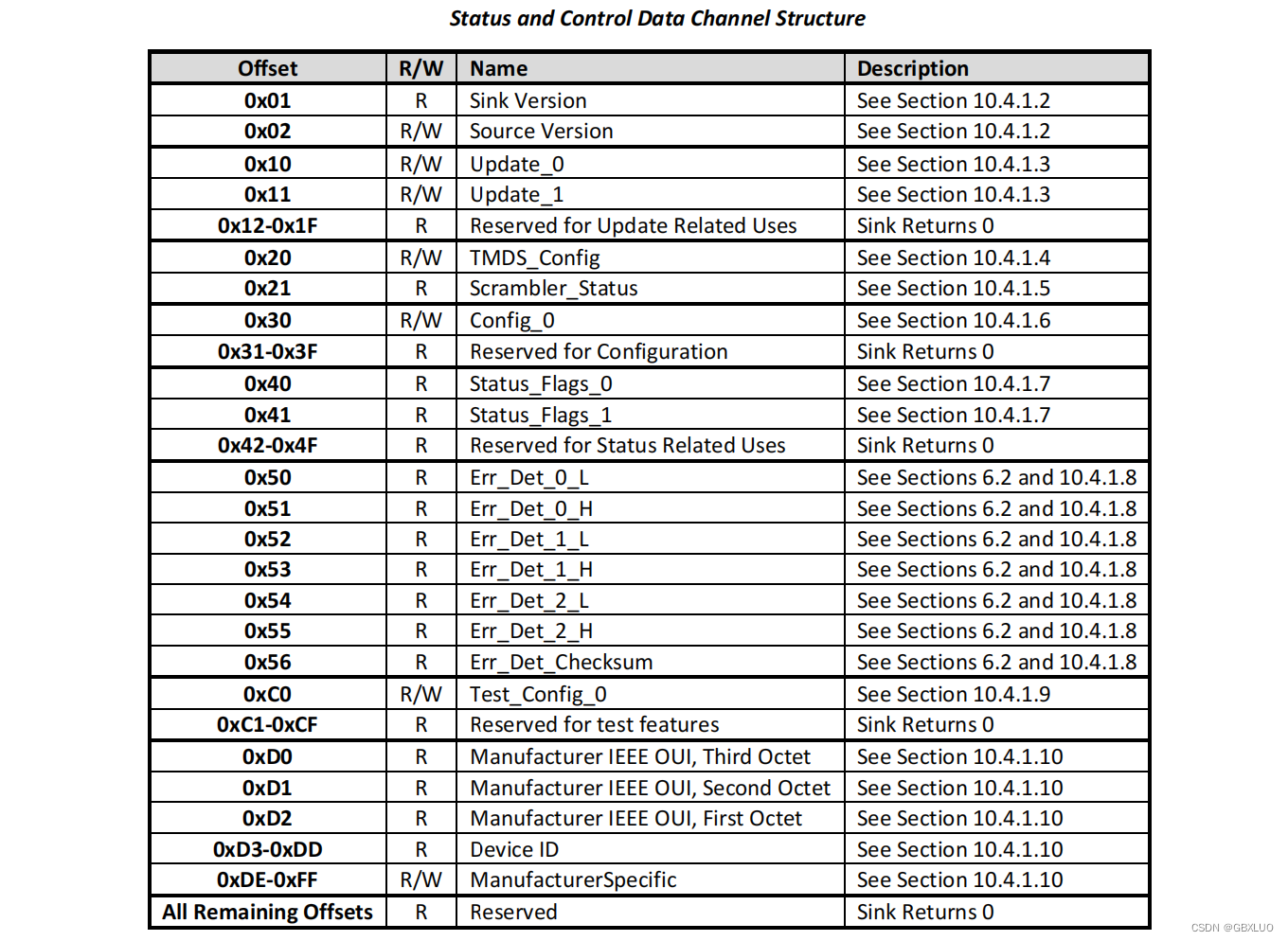

四、SCDC Channel Structure通道结构-寄存器地址与功能

参看HDMI2.0协议的10.4.1 Status and Control Data Channel Structure节:

Reserved默认为0x00.

各寄存器的功能查看HDMI2.0协议。

五、分析HDMI_DDC协议解读.kvdat文件

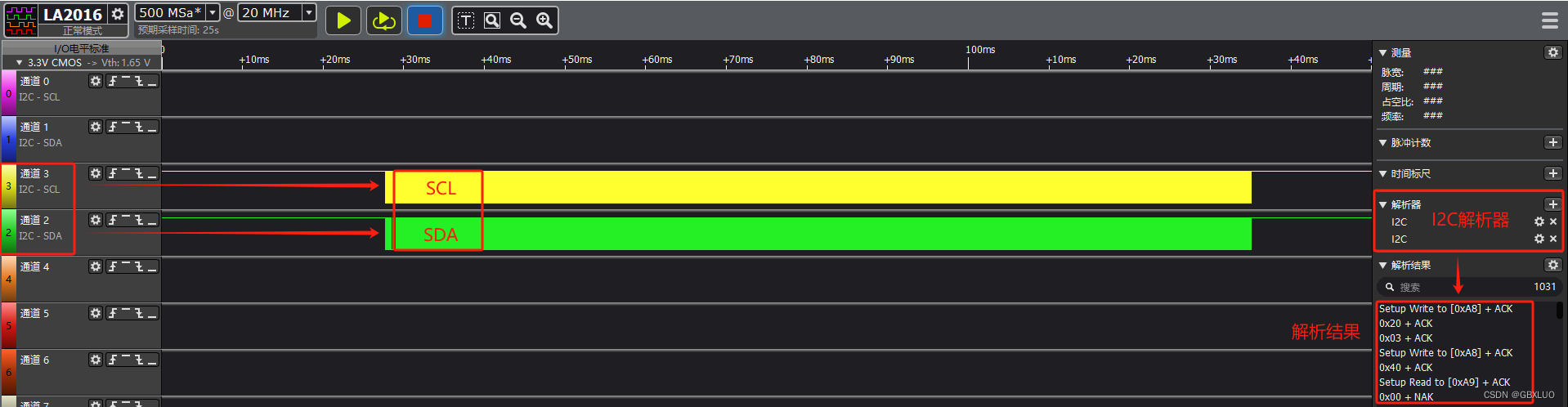

5.1 使用KingstVIS软件打开DDC数据附件

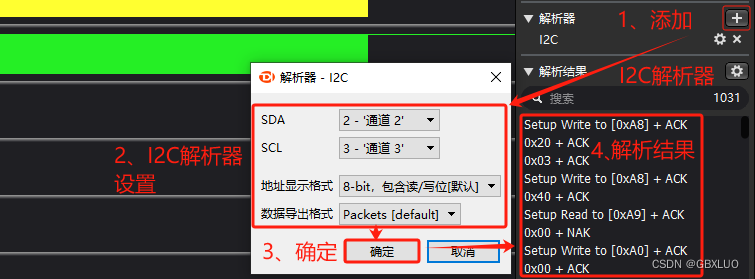

使用KingstVIS打开HDMI_DDC协议解读.kvdat文件后使用I2C解析器设置如下:

I2C解析器设置:

SDA:2-“同道 2”

SCL:3-“通道 3”

地址显示格式:8-bit,包含读写位

数据导出格式:默认Packets

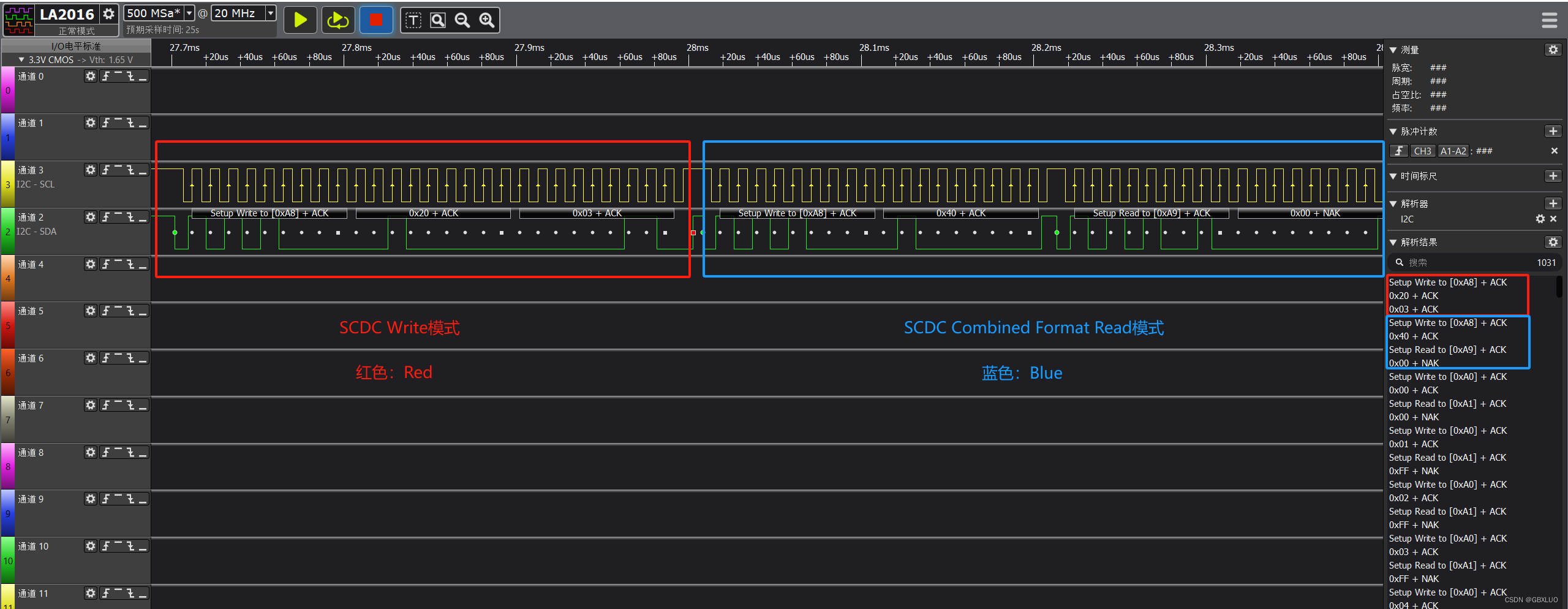

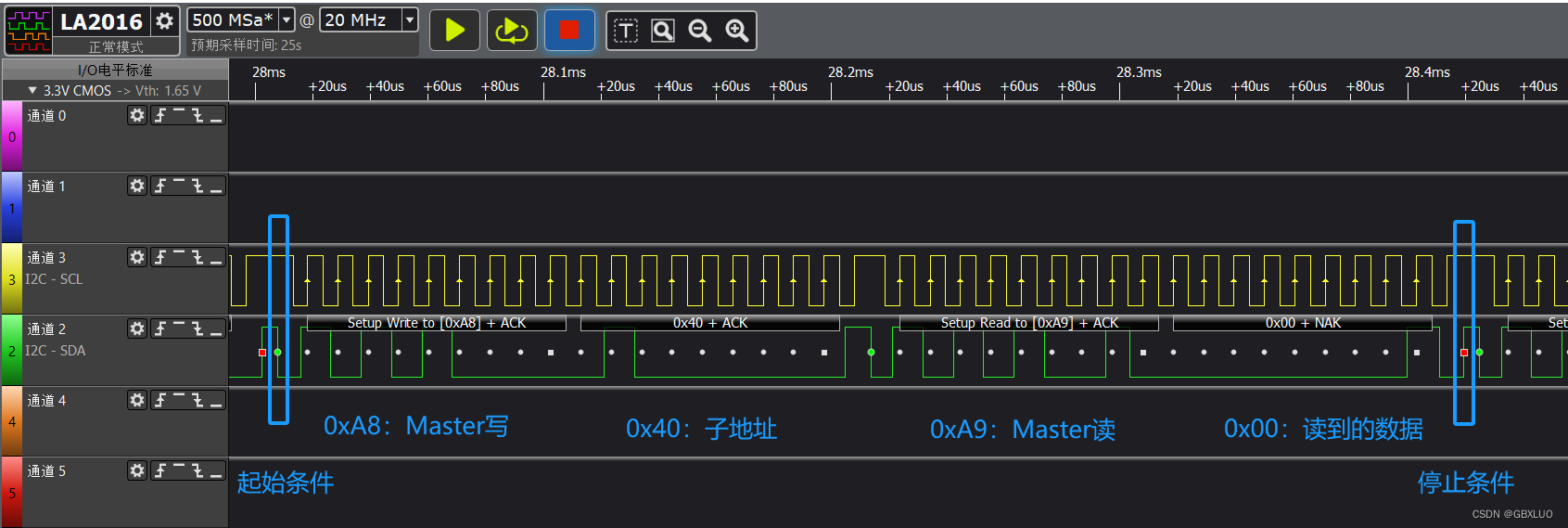

并截取HDMI_DDC协议解读.kvdat开始通信部分数据分析:

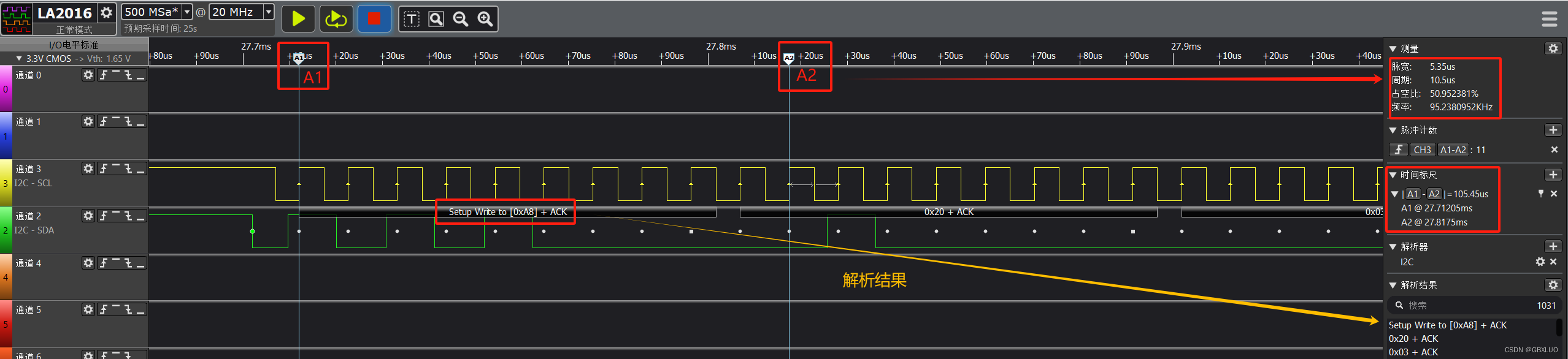

5.2 查看时钟频率

首先截取10个周期clk查看时钟频率约为95.2KHz,是I2C的标准模式(100KHz)。

5.3 数据分析

这里仅分析SCDC Write模式与SCDC Combined Format模式,SCDC Update Read模式本质一样。

5.3.1 SCDC Write模式数据分析

上图通过逻辑分析仪看出是:

0xA8:Master写

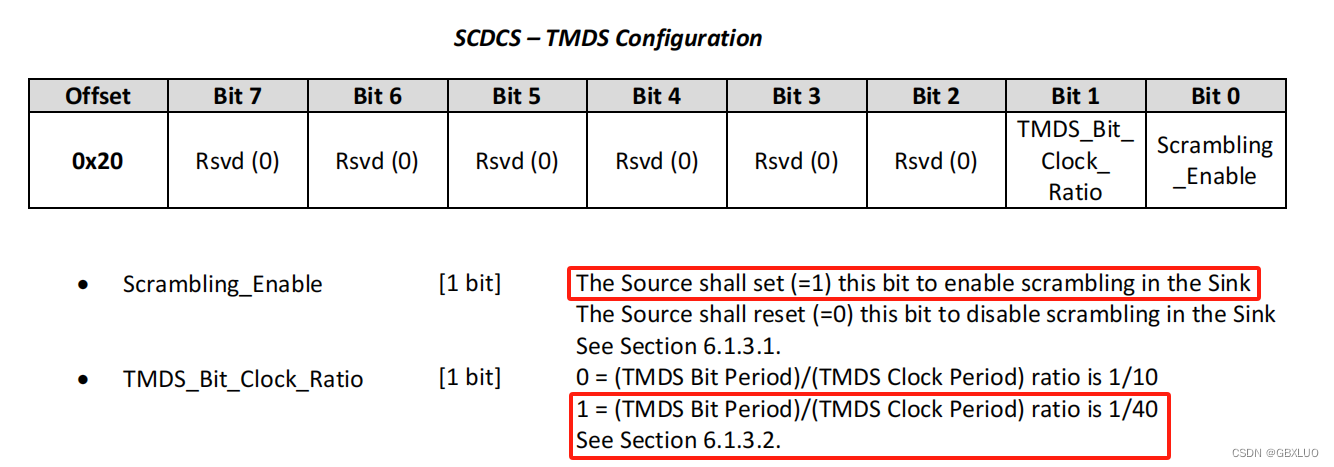

0x20:子地址,通过查HDMI2.0规格书可以知道0x20是TMDS配置寄存器;

| Offset | R/W ? | Name |

| 0x20 | R/W均可 | TMDS_Config |

0x03:要写进到Slave的寄存器0x20的数据Data为0x03=0b0000_0011.

Scrambling_Enable(Bit 1)置1;

TMDS_Bit_Clock_Ratio(Bit 0)置1;

使能扰码并设置每个TMDS Clock周期与TMDS Bit的比率为40:1。

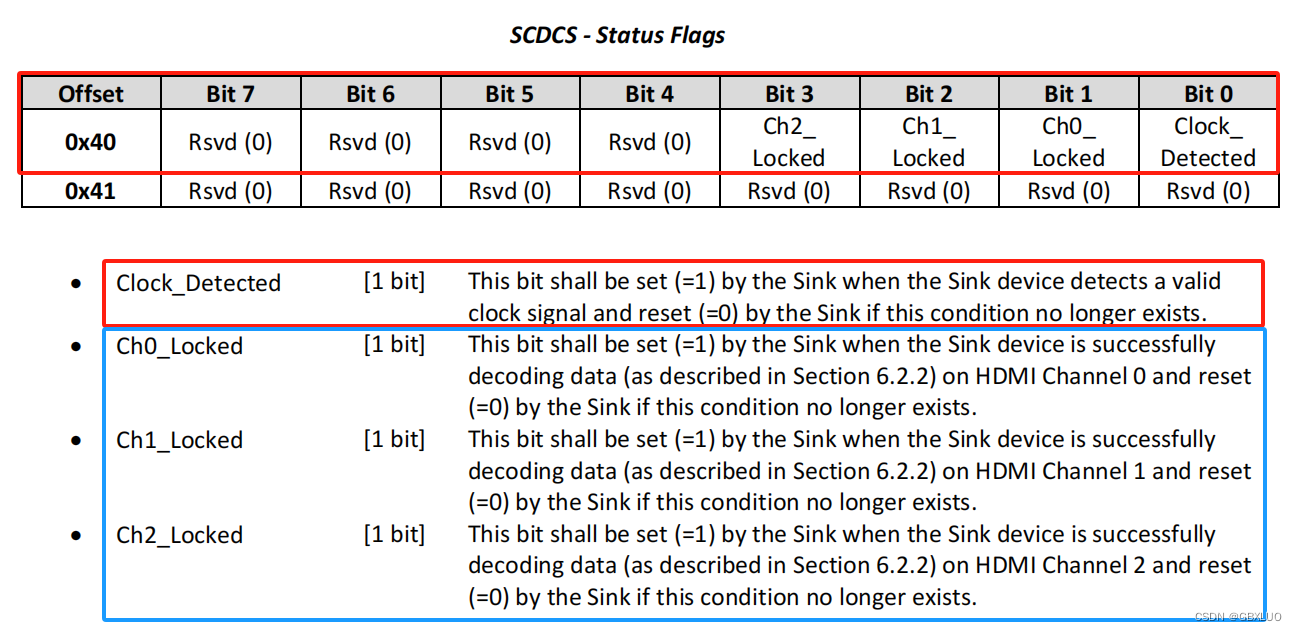

5.3.2 SCDC Combined Format模式数据分析

0xA8:Master写

0x40:子地址,通过查HDMI2.0规格书可以知道0x40是Status_Flags_0标志寄存器;

| Offset | R/W ? | Name |

| 0x40 | 仅支持R | Status_Flags_0 |

0xA9:Master读

0x00:Master从Slave的寄存器0x40读到的数据Data为0x00=0b0000_0000.

该寄存器用于检测Slave端是否成功识别Clock以及3个数据通道是否成功Lock住,很显然,时钟与数据都没lock 住,也就是通信不成功。

其他HDMI_DDC协议解读.kvdat数据解析同上。