- 1小学生计算机课堂实践的重要性,小学《信息技术》有效课堂教学的实践与研究课题方案...

- 2前后端分离开发

- 3开发环境上云,打造五星级开发体验_研发环境上云案例

- 4大模型部署手记(20)Windows+Qwen-VL-Chat-Int4_qianwen大模型本地部署

- 5Rabbit 登录遇到问题:User can only log in via localhost

- 6AI,爱_-ai-愛 博客

- 7深度强化学习(DRL)算法 1 —— REINFORCE_llm drl

- 8Python 霸榜的一周,又有什么新 AI 力作呢?「GitHub 热点速览」

- 9通过selenium框架爬取图片_selenium爬取网页中所有图片

- 10React 之 lazy(延迟加载)(十七)

FPGA 静态时序分析与约束(2)_quartus unconstrained path

赞

踩

Quartus II时序约束工具简要操作

项目简述

这里提醒,在看这篇文章之前一定要先把前一篇时序约束的文章看完,前面一篇才是重点,这篇就是一些简单的工具使用。

我们前面的一篇博客已经讲解了FPGA内部、IO接口的延迟约束。对建立时间、保持时间进行了深入的讲解,并且通过几个例子让大家明白了input delay max、input delay min、output delay max、output delay min四个值得计算。那么我们这篇论文得目的就是讲解软件得操作。我们先以Quartus II为例进行讲解,然后讲解Vivado。这样讲解得目的是Quartus II得时序分析工具TimeQuest工具非常标准容易理解。Vivado与Quartus II又十分相似,借助里面得原语又可以得到更深得理解。相当于Vivado与Quartus II的两篇博客综合学习可以更深的理解时序约束概念。等到下篇博客将解时序约束的原语与GUI操作的时候,大家会深有同感。

我们这里认为时序约束的步骤按照下面步骤比较好:

时序约束步骤

Quartus II的时序工具的操作步骤主要如下:

1、打开TimeQuest工具

2、创建时序网表(直接默认即可,不用选择特定的快速或慢速网表)

3、读取SDC文件

4、可以查看报告,也可以加入约束

上述的图形化操作如下:

查看时序报告从Tasks中查看,常见的报告时序操作如下:

1、报告时钟

2、报告最差的路径

3、报告特定的时序:

这是几个常见的时序报告的操作步骤,至于其他的可以尝试自己点击进行测试。然后,我们将严格按照图中顺序介绍Quartus II的软件操作步骤。

约束时钟

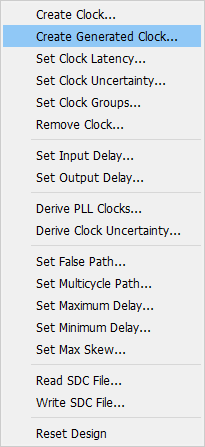

Quartus II所有的时钟约束都在下面的选项中完成:

创建输入时钟

我们点击Creak Clock可以创建时钟约束:

创建生成时钟

点击Create Generated Clock创建生成时钟,所谓的生成时钟就是PLL衍射出来的时钟,这里Quartus II与Vivado就有所不同,因为Vivado中PLL的衍射时钟默认是给生成的,而Quartus II不给默认生成。

出下面界面:

1、这里是生成时钟的原时钟,换句话说也就是PLL的输入时钟

2、这里描述生成时钟与原时钟的倍分频关系

3、这里指明生成时钟的信号

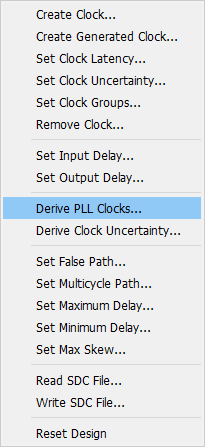

当然也有简单的方法一步约束所有的PLL的生成时钟,点击约束菜单中的Derive PLL Clocks

然后点击运行:

约束自己分频的时钟

约束步骤与约束PLL时钟的第一种方法一摸一样。

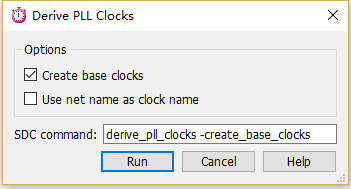

输入延迟的约束

根据输入延迟的约束有许多种情况,比如系统同步、原同步、SDR数据输入、DDR数据输入、中心对齐、边缘对齐。这里面的难点主要是不同情况下input delay min、input delay max的计算。这个值得计算,同学们结合第一篇文章与Vivado中对原语得操作可以学会计算方法。这里我们只简要说明TimeQuest工具得使用。

对输入延迟约束首先得约束延迟数据得随路时钟。 方法与前面时钟得约束完全相同。

约束完数据的时钟之后,约束数据的输入延迟:

点击确定如下:

1、当数据是中心对齐而且把下降沿当成发射沿的时候,勾选1,否则即便是中心对齐也不勾选。当然两种情况的input delay min、input delay max值不同,但对于EDA分析工具都一样。

2、input delay min的约束

3、input delay max的约束,注意max、min需要分别进行这个界面的约束

4、一般勾选add delay,这是与物理约束的一些关系

5、一般SDR数据选择Both即可,对于DDR数据约束分别选择Rise、Fall进行input delay min、input delay max的约束

至于上面input delay min、input delay max两个值得计算可以结合第一篇时序博客与Vivado得原语介绍部分进行相应的学习。

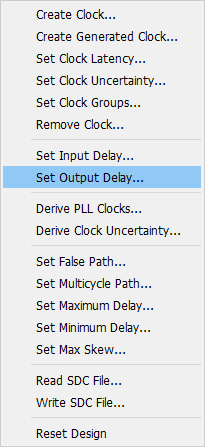

输出延迟的约束

输出时间的延迟与输入延迟一样分为:系统同步、原同步、SDR数据输入、DDR数据输入。与输入延迟不一样的是没有没对边沿对齐与中心对齐加以区分,因为我们输出延迟的设计只需要满足下游器件的建立时间与保持时间即可。至于每种情况

output delay min、output delay max的计算同样查阅第一篇文章。

对输入延迟约束首先得约束延迟数据得随路时钟,一般这个时钟是生成时钟。 方法与前面生成时钟得约束完全相同。

约束完数据的时钟之后,约束数据的输出延迟:

点击Set Output Delay得到下面界面:

1、当数据是中心对齐而且把下降沿当成发射沿的时候,勾选1,否则即便是中心对齐也不勾选。当然两种情况的output delay min、outputdelay max值不同,但对于EDA分析工具都一样。

2、outputdelay min的约束

3、outputdelay max的约束,注意max、min需要分别进行这个界面的约束

4、5、输出延迟值得设置,一般勾选add delay,这是与物理约束的一些关系

6、选择输出数据得信号对象

7、一般SDR数据选择Both即可,对于DDR数据约束分别选择Rise、Fall进行output delay min、output delay max的约束

输出延迟要比输入延迟简单,因为我们主要是为了满足下游器件得时序要求。

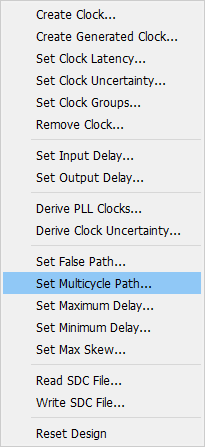

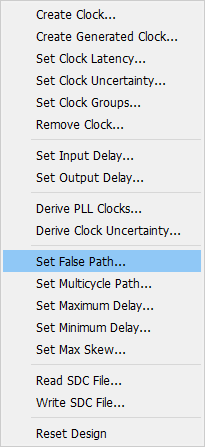

设置时序例外

设置时序例外主要有两种操作,一个是多周期路径,另一个是false路径。这两个其实在EDA工具进行布局布线得时候没什么作用,前者是让数据发射沿与数据接收沿之间的时间增大给建立时间带来好处,后者是告诉EDA工具不分析这一块。但是时序例外之前,一定要进行相应的处理,多周期路径的设置一定要是真的多周期路径,false掉的路径一定要对齐做跨时钟域处理、或者像是复位信号这种频率特别低的信号。

设置多周期路径

点击Set Multicycle Path弹出下面窗口:

1、选择需要设置多周期的路径

2、设置需要进行多周期的是建立时间还是保持时间

3、多周期路径到底是针对发射沿还是采样沿来说的,一般是采样沿

设置false路径

false路径在约束菜单栏中的如下位置:

点击Set False Path如下:

选择需要设置false的路径即可。

操作小结

上面所有的时序约束都可以跟着Report Timing来走,尤其是时序例外操作,在时序不满足要求的地方进行右击设置相应的多周期与false路径,这样就避免了自己寻找相应的节点,减少了自己的工作量。

解决时序违例另一种常见的方法就是插入寄存器,改成流水线操作,但是插寄存器的时候不能随便乱插,见组合逻辑就插寄存器。我们要根据Report Timing来插寄存器。

总结

接触了FPGA已经两年时间,直到现在才敢说自己掌握了静态时序分析,学习过程可以说非常坎坷,因为当时的学习资料太少。后面的文章,我们将介绍Quartus II与Vivado的时序工具的使用。上面文章的学习途径在参考文献中已经给出。创作不易,认为文章有帮助的同学们可以关注、点赞、转发支持。为行业贡献及其微小的一部分。或者对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群: