热门标签

热门文章

- 1kafka集群搭建以及运行kafka监控平台kmonitor_kafka 监控k-million

- 2在VMware安装Androidx86_64系统要点_vmware android

- 3Traefik v3.0 Docker 全面使用指南:基础篇_traefik middleware开发

- 4安全测试必学神器 -- BurpSuite 安装及使用实操指南_burpsuite安装及使用-实验报告

- 5C++多线程编程学习一 [关于数据竞争问题]_c++下面哪些方法可以减少数据竞争

- 6Spring项目&spring-boot-starter组件&Spring Cloud生态圈以及微服务简介_spring cloud starter

- 7mysql数据库的url及,MYSQL教程详解数据库连接的URL的写法及总结

- 8Kafka系列之:实现对Kafka集群的监控_java实现kafka数据监控

- 9前端页面莫名出现了NaN的问题怎么解决?_前端网页出现nan

- 10zmud之小技巧

当前位置: article > 正文

基于FPGA的带闹钟功能的数字钟设计VHDL代码Quartus仿真_基于fpga的定时闹钟

作者:2023面试高手 | 2024-06-17 08:39:30

赞

踩

基于fpga的定时闹钟

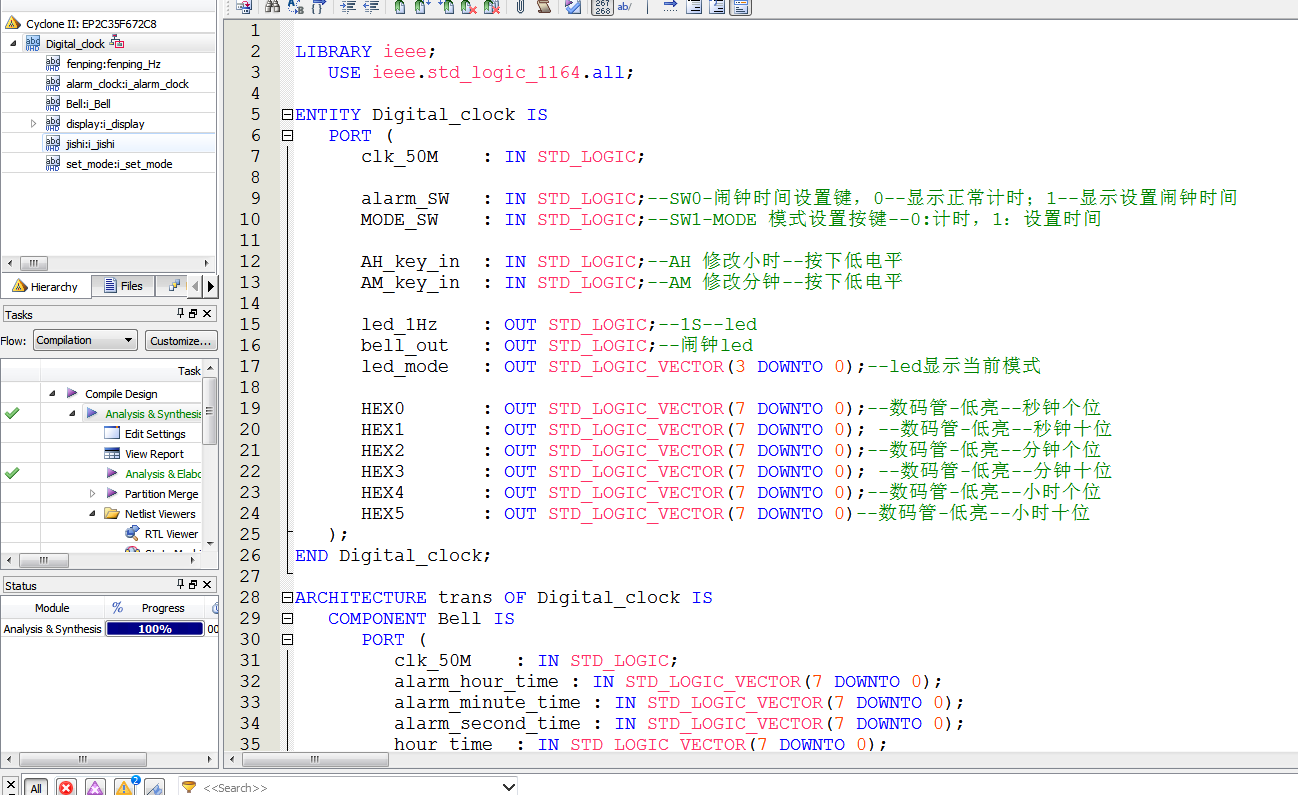

名称:基于FPGA的带闹钟功能的数字钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

1、可以调节小时、分钟

2、可以调整闹钟时间

3、到设置的时间闹铃响

4、整点报时

控制方法:

2个拨码开关SW0和SW1控制模式:

SW0=0,SW1=0为正常计时模式;

SW0=0,SW1=1为修改时间模式;

SW0=1,SW1=0为显示闹钟时间模式;

SW0=1,SW1=1为修改闹钟时间模式;

2个按键,BT0修改小时,BT1修改分钟:

将拨码开关设置为SW0=0,SW1=1,此时可以修改当前时间;

将拨码开关设置为SW0=1,SW1=1,此时可以修改闹钟时间;

1. 工程文件

2. 程序文件

3. 程序编译

4. 程序RTL图

5. Vwf文件

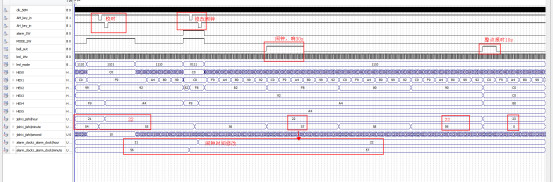

6. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Digital_clock IS PORT ( clk_50M : IN STD_LOGIC; alarm_SW : IN STD_LOGIC;--SW0-闹钟时间设置键,0--显示正常计时;1--显示设置闹钟时间 MODE_SW : IN STD_LOGIC;--SW1-MODE 模式设置按键--0:计时,1:设置时间 AH_key_in : IN STD_LOGIC;--AH 修改小时--按下低电平 AM_key_in : IN STD_LOGIC;--AM 修改分钟--按下低电平 led_1Hz : OUT STD_LOGIC;--1S--led bell_out : OUT STD_LOGIC;--闹钟led led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--led显示当前模式 HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--秒钟个位 HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管-低亮--秒钟十位 HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--分钟个位 HEX3 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管-低亮--分钟十位 HEX4 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--小时个位 HEX5 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管-低亮--小时十位 ); END Digital_clock; ARCHITECTURE trans OF Digital_clock IS COMPONENT Bell IS PORT ( clk_50M : IN STD_LOGIC; alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bell_out : OUT STD_LOGIC ); END COMPONENT; COMPONENT alarm_clock IS PORT ( clk_50M : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); AH_key : IN STD_LOGIC; AM_key : IN STD_LOGIC; alarm_hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; COMPONENT display IS PORT ( clk : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX3 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX4 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX5 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; COMPONENT set_mode IS PORT ( clk_50M : IN STD_LOGIC; alarm_SW : IN STD_LOGIC; MODE_SW : IN STD_LOGIC; led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); state_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; COMPONENT fenping IS PORT ( clk_50M : IN STD_LOGIC; led_1Hz : OUT STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_50M : IN STD_LOGIC; clk_1Hz : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); AH_key : IN STD_LOGIC; AM_key : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/730449

推荐阅读

相关标签