- 1【机器学习:推荐系统】什么是推荐系统?

- 2全网最细海龟 (turtle) 画图讲解 (三):设置画笔样式_python的turtle模块更改画笔形状

- 3多表连接查询详细解析(详细版)_连表查询

- 4threeJS 实现加载模型 + 页面按钮交互 + 显示css2Renderer标注_css2drenderer

- 5unity中rectTransform的宽和高如何取_recttransform 获取宽度

- 6async python两个_摆脱js回调地狱,Async/Await实用指南,完美实现同步操作

- 7window pytorch unet代码学习之random_split_sum of input lengths does not equal the length of

- 8VS+Qt — Vistual Studio 2022+Qt6安装教程以及解决Qt Vistual Studio Tools下载慢和VS无法打开.ui进行设计的问题_legacy qt visual studio tools

- 9连接Sql2005报的错误:Caused by: com.microsoft.sqlserver.jdbc.SQLServerException: 到主机 的 TCP/IP 连接失败

- 10大模型入门到应用——LangChain:索引(Indexes)-[文本分割器(Text Splitters)]_langchain.text_splitter

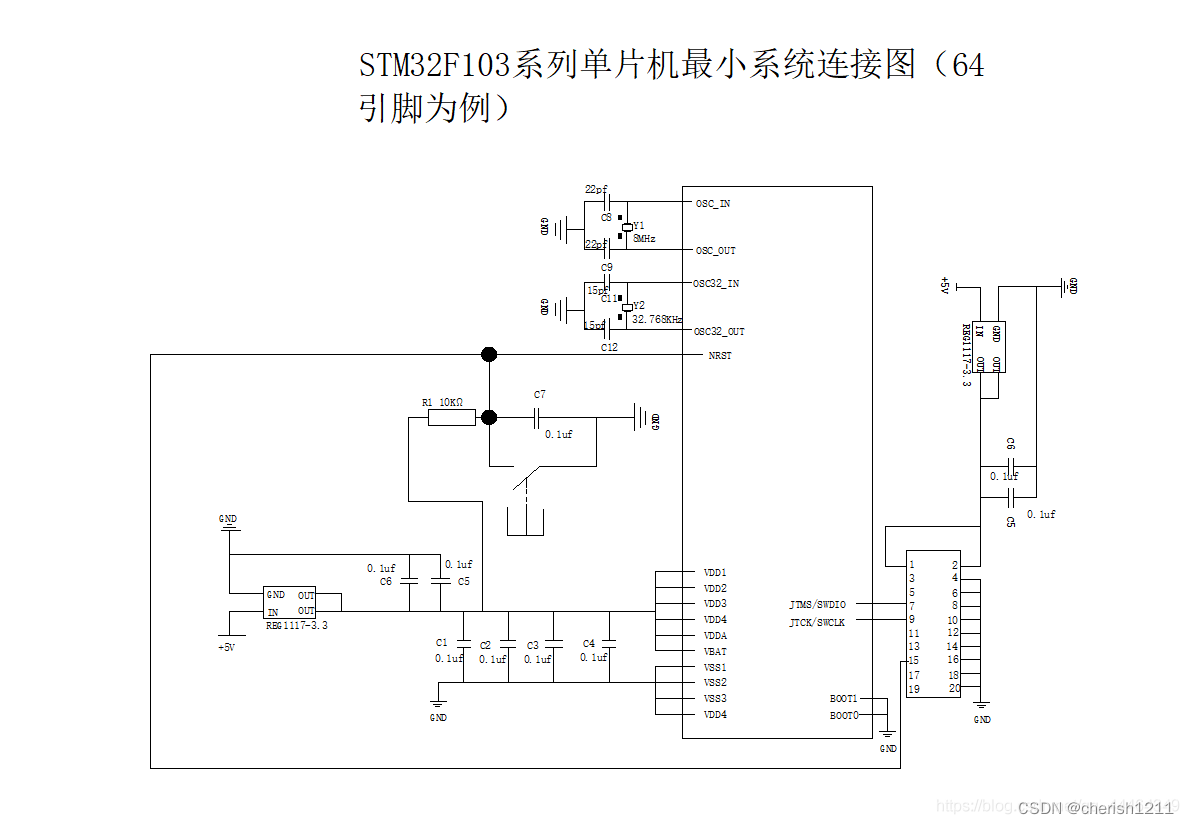

stm32f103c8t6最小系统

赞

踩

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

stm32f103c8t6构成

单片机芯片、供电电路、时钟电路、复位电路、程序下载电路、启动配置电路。

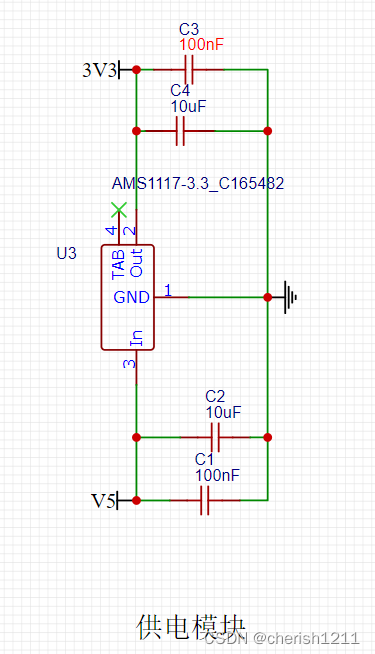

二:电源电路

5v转3.3v,中间的是线性降压 VDDX、VBAT、VDDA分别为接口、RTC、ADC供电。

稳压模块

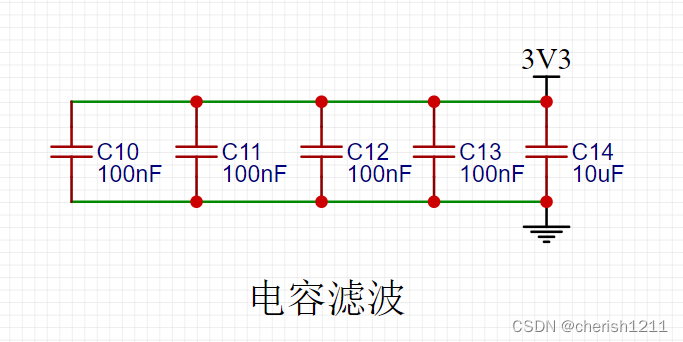

STM32F103的电源必须稳定,所以加上多个电容用于稳定电压。

也叫去耦电路

去耦电路:去除 芯片 电源管脚上的噪声

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转变为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去偶电容可以抑制因负载变化而产生的噪声

注意

这些电容也尽量离芯片相关引脚近一点。分布在芯片四周即可。

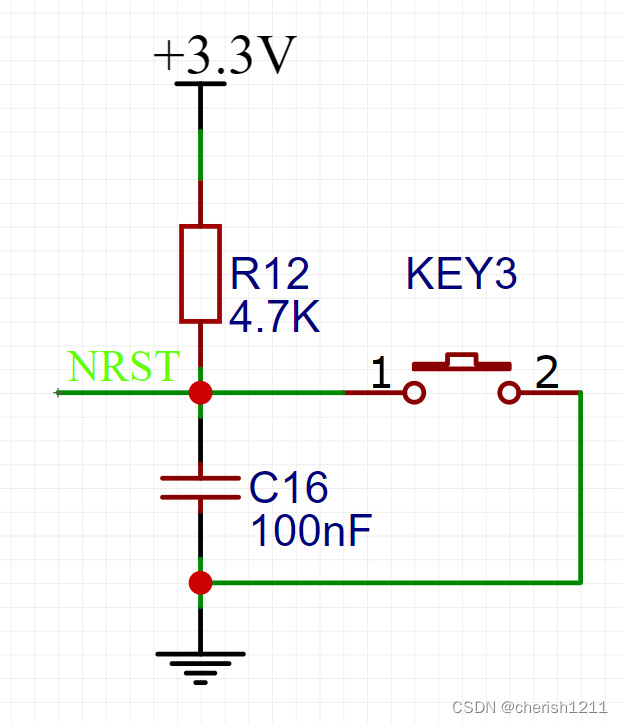

复位电路

NRST

STM32F的NRST是异步复位脚。 当NRST输入低电平的时候,MCU处于复位状态,重设所有的内部寄存器,及片内几十KB的SRAM。

当NRST从低电平变高时,PC指针从0开始。

但是复位的时候不会将STM32F片内RTC的寄存器以及后备存储器重置,因为它们是用电池通过专门的VBAT脚供电。

STM32中的NRST有施密特功能。大概在输入电压低于1.V的时候将芯片复位

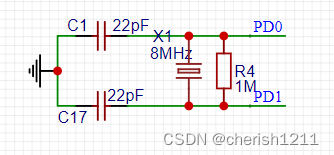

时钟电路

左图为高速外部电路

右图为外部低速电路

负载电容是指晶振要正常震荡所需要的电容。 换句话说,晶振的频率就是在它提供的负载电容下测得的,能最大限度的保证频率值的误差。 晶振的负载电容值是已知数,在出厂的时候已经定下来。 单片机晶振上两个电容是晶振的外接电容,分别接在晶振的两个脚上和对地的电容,一般在几十皮发,在选择外接电容的时候是根据晶振厂家提供的晶振要求选值的,一般外接电容是为了使晶振两端的等效电容等于或接近负载电容。

晶振电路都是在一个反相放大器的两端接入晶振,再有两个电容分别接入到晶振的两端,另一个电容则接地,这两个电容串联的电容量就等于负载电容。

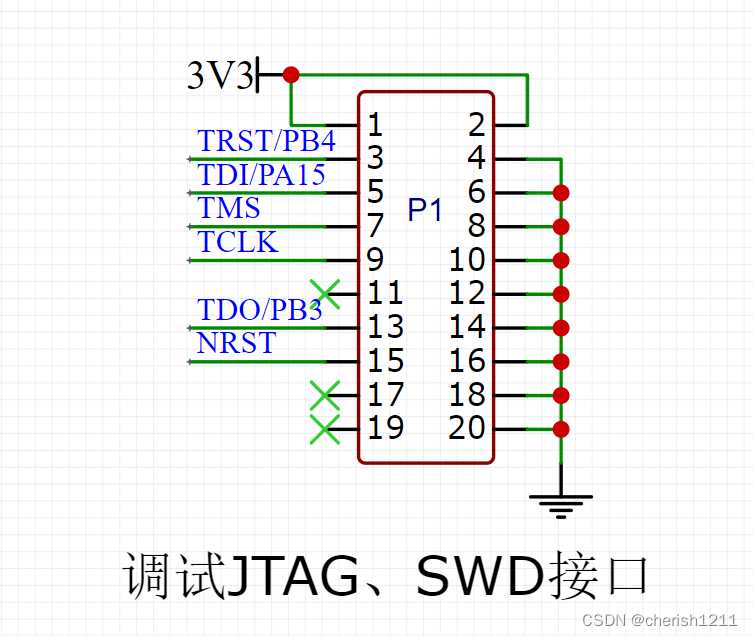

程序下载电路

JTAG

SWD

JTAG接口标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

其中TRST是可选项

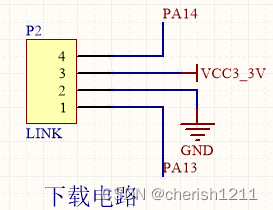

SWD接口

.SWD是一种串行调试接口,与JTAG相比,SWD只要两根线,分别为:SWCLK和SWDIO SWDIO–串行数据线,用于数据的读出和写入

SWDCLK–串行时钟线,提供所需要的时钟信号

PA14为SWCLK,PA13为SWDIO

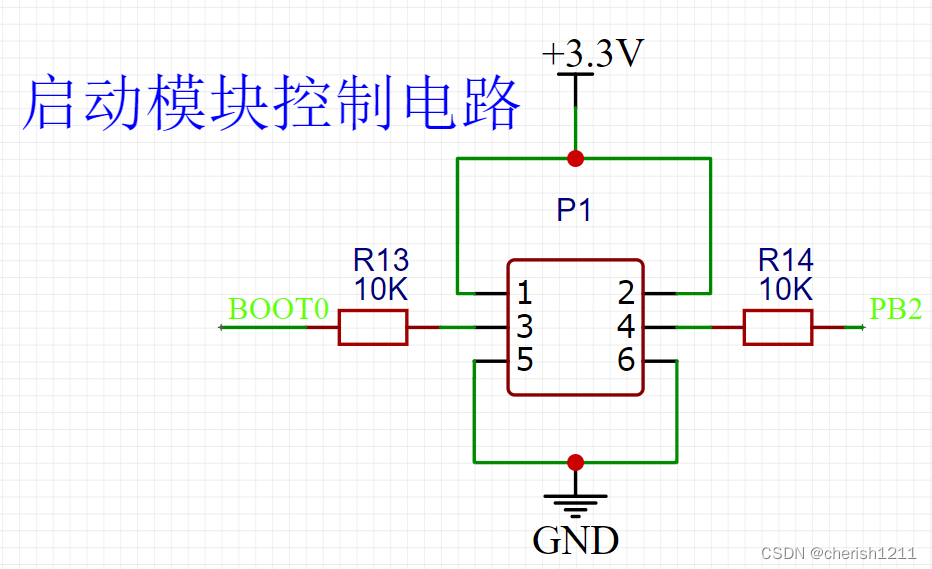

启动配置电路

BOOT2为PB2

晶振电路

注意

画板时晶振尽量离芯片近一点

晶振底部尽量不要穿过其他支路,防止信号串扰