- 1《Python自然语言处理》第二章 习题解答 练习6

- 2YOLOv7改进:BoTNeT(Bottleneck Transformer)_yolov7使用botnet

- 3计算机毕业设计springboot农贸市场摊位出租系统k52bf9【附源码+数据库+部署+LW】_农贸菜市场租位管理系统的类图

- 4第一课:什么是树莓派_树莓派为啥叫树莓派

- 5InstructGPT高效实践——【DeepSpeed-Chat】源码详解(1/3):基本概念、数据集管理_deepspeed chat数据集

- 621.5k Star , AI 智能体项目OpenDevin:少写代码,多创造(附部署教程)_opendevin部署到windows

- 7go语言kafka入门_kafka-go

- 8【C语言】库函数—qsort

- 9Python的安装_python 阿里源

- 10高可靠性部署系列(3)--- ASG双机热备(HA)

Verilog--除法器的简单实现_verilog除法

赞

踩

除法器在FPGA里怎么实现呢?当然不是让用“/”和“%”实现。

在Verilog HDL语言中虽然有除的运算指令,但是除运算符中的除数必须是2的幂,因此无法实现除数为任意整数的除法,很大程度上限制了它的使用领域。并且多数综合工具对于除运算指令不能综合出令人满意的结果,有些甚至不能给予综合。即使可以综合,也需要比较多的资源。对于这种情况,一般使用相应的算法来实现除法,分为两类,基于减法操作和基于乘法操作的算法。

1 组合实现

基于减法的除法器的算法

对于32的无符号除法,被除数a除以除数b,他们的商和余数一定不会超过32位。首先将a转换成高32位为0,低32位为a的temp_a。把b转换成高32位为b,低32位为0的temp_b。在每个周期开始时,先将temp_a左移一位,末尾补0,然后与b比较,是否大于b,是则temp_a减去temp_b将且加上1,否则继续往下执行。上面的移位、比较和减法(视具体情况而定)要执行32次,执行结束后temp_a的高32位即为余数,低32位即为商。

module div_rill ( input[31:0] a, input[31:0] b, output reg [31:0] yshang, output reg [31:0] yyushu ); reg[31:0] tempa; reg[31:0] tempb; reg[63:0] temp_a; reg[63:0] temp_b; integer i; always @(a or b) begin tempa <= a; tempb <= b; end always @(tempa or tempb) begin temp_a = {32'h00000000,tempa}; temp_b = {tempb,32'h00000000}; for(i = 0;i < 32;i = i + 1) begin temp_a = {temp_a[62:0],1'b0}; if(temp_a[63:32] >= tempb) temp_a = temp_a - temp_b + 1'b1; else temp_a = temp_a; end yshang <= temp_a[31:0]; yyushu <= temp_a[63:32]; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

testbench代码

`timescale 1ns/1ns module div_rill_tb; reg [31:0] a; reg [31:0] b; wire [31:0] yshang; wire [31:0] yyushu; initial begin #10 a = $random()%10000; b = $random()%1000; #100 a = $random()%1000; b = $random()%100; #100 a = $random()%100; b = $random()%10; #100 a = $random()%100; b = $random()%10; #100 a = $random()%100; b = $random()%10; #100 a = $random()%100; b = $random()%10; #1000 $stop; end div_rill DIV_RILL ( .a (a), .b (b), .yshang (yshang), .yyushu (yyushu) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

1,将组合逻辑改成时序逻辑,用32个clk实现计算。

2,计算位宽可以配置,具有扩展性。

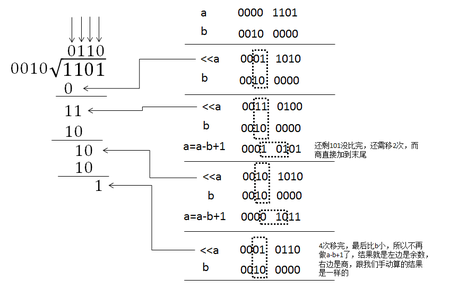

附录:算法推倒(非原创)

假设4bit的两数相除 a/b,商和余数最多只有4位 (假设1101/0010也就是13除以2得6余1)

我们先自己做二进制除法,则首先看a的MSB,若比除数小则看前两位,大则减除数,然后看余数,以此类推直到最后看到LSB;而上述算法道理一样,a左移进前四位目的就在于从a本身的MSB开始看起,移4次则是看到LSB为止,期间若比除数大,则减去除数,注意减完以后正是此时所剩的余数。而商呢则加到了这个数的末尾,因为只要比除数大,商就是1,而商0则是直接左移了,因为会自动补0。这里比较巧因为商可以随此时的a继续左移,然后新的商会继续加到末尾。经过比对会发现移4位后左右两边分别就是余数和商。

画个简单的图:

2 时序实现

相比于上面的组合实现,增加了下面的信号:

1,改成clk方式。

2,添加clk,50MHz。

3, 添加rst,同步复位。

4,添加calc_done,指示计算完成,高有效。

/* * module:div_rill * file name:div_rill.v * syn:yes * author:network * modify:rill * date:2012-09-10 */ module div_rill ( input clk, input rst, input[31:0] a, input[31:0] b, output reg [31:0] yshang, output reg [31:0] yyushu, output reg calc_done ); reg[31:0] tempa; reg[31:0] tempb; reg[63:0] temp_a; reg[63:0] temp_b; reg [5:0] counter; always @(a or b) begin tempa <= a; tempb <= b; end always @(posedge clk) begin if(!rst) begin temp_a <= 64'h0000_0000_0000_0000; temp_b <= 64'h0000_0000_0000_0000; calc_done <= 1'b0; end else begin if(counter <= 31) begin temp_a <= {temp_a[62:0],1'b0}; if(temp_a[63:32] >= tempb) begin temp_a <= temp_a - temp_b + 1'b1; end else begin temp_a <= temp_a; end counter <= counter + 1; calc_done <= 1'b0; end else begin counter <= 0; calc_done <= 1'b1; temp_a <= {32'h00000000,tempa}; temp_b <= {tempb,32'h00000000}; yshang <= temp_a[31:0]; yyushu <= temp_a[63:32]; end end end endmodule /*************** EOF ******************/

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

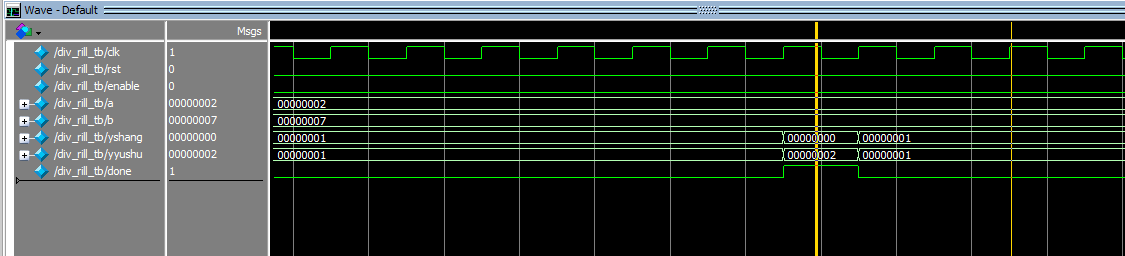

Testbench

/* * module:div_rill_tb * file name:div_rill_tb.v * syn:no * author:rill * date:2012-09-10 */ `timescale 1ns/1ns module div_rill_tb; reg clk; reg rst; reg [31:0] a; reg [31:0] b; wire [31:0] yshang; wire [31:0] yyushu; wire calc_done; initial begin clk = 0; rst = 0; #20 rst = 1; #40 a = $random()%10000; b = $random()%1000; #1000 a = $random()%1000; b = $random()%100; #1000 a = $random()%100; b = $random()%10; #1000 $stop; end always #10 clk = ~clk; div_rill DIV_RILL ( .clk (clk), .rst (rst), .a (a), .b (b), .yshang (yshang), .yyushu (yyushu), .calc_done (calc_done) ); endmodule /******** EOF ******************/

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

3 状态机实现

/* * module:div_rill * file name:div_rill.v * syn:yes * author:rill * date:2014-04-10 */ module div_rill ( input clk, input rst, input enable, input [31:0] a, input [31:0] b, output reg [31:0] yshang, output reg [31:0] yyushu, output reg done ); reg[31:0] tempa; reg[31:0] tempb; reg[63:0] temp_a; reg[63:0] temp_b; reg [5:0] status; parameter s_idle = 6'b000000; parameter s_init = 6'b000001; parameter s_calc1 = 6'b000010; parameter s_calc2 = 6'b000100; parameter s_done = 6'b001000; reg [31:0] i; always @(posedge clk) begin if(rst) begin i <= 32'h0; tempa <= 32'h1; tempb <= 32'h1; yshang <= 32'h1; yyushu <= 32'h1; done <= 1'b0; status <= s_idle; end else begin case (status) s_idle: begin if(enable) begin tempa <= a; tempb <= b; status <= s_init; end else begin i <= 32'h0; tempa <= 32'h1; tempb <= 32'h1; yshang <= 32'h1; yyushu <= 32'h1; done <= 1'b0; status <= s_idle; end end s_init: begin temp_a = {32'h00000000,tempa}; temp_b = {tempb,32'h00000000}; status <= s_calc1; end s_calc1: begin if(i < 32) begin temp_a = {temp_a[62:0],1'b0}; status <= s_calc2; end else begin status <= s_done; end end s_calc2: begin if(temp_a[63:32] >= tempb) begin temp_a = temp_a - temp_b + 1'b1; end else begin temp_a = temp_a; end i <= i + 1'b1; status <= s_calc1; end s_done: begin yshang <= temp_a[31:0]; yyushu <= temp_a[63:32]; done <= 1'b1; status <= s_idle; end default: begin status <= s_idle; end endcase end end endmodule /*************** EOF ******************/

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

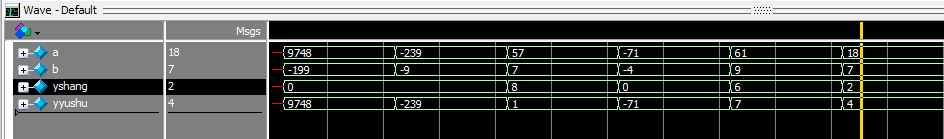

Testbench

/* * module:div_rill_tb * file name:div_rill_tb.v * syn:no * author:rill * date:2014-04-10 */ `timescale 1ns/1ns module div_rill_tb; reg clk; reg rst; reg enable; reg [31:0] a; reg [31:0] b; wire [31:0] yshang; wire [31:0] yyushu; wire done; initial begin clk = 0; #10 rst = 1; #20 rst = 0; #15 enable =1; a = 2;//$random()%10000; b = 7;//$random()%1000; #10 enable =0; #1000 enable =1; a = 7;//$random()%1000; b = 2;//$random()%100; #10 enable =0; #1000 enable =1; a = 7;//$random()%100; b = 7;//$random()%10; #10 enable =0; #1000 $stop; end always # 5 clk = ~clk; div_rill DIV_RILL ( .clk (clk), .rst (rst), .enable (enable), .a (a), .b (b), .yshang (yshang), .yyushu (yyushu), .done (done) ); endmodule /******** EOF ******************/

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

仿真