热门标签

热门文章

- 1关于jsonobject类型的Null值怎么判断的问题,JSONObject$Null_jsonobject判断null

- 2INTELLIJ IDEA 项目(初始化/删除) GIT_idea删除git信息

- 3逻辑思维训练1200题-蓝桥杯计算思维参考_蓝桥杯计算思维u8

- 4优化算法|遗传算法求解作业车间调度问题(Python)_python实现遗传算法车间调度求解的代码

- 5mysql8 Incorrect datetime value: '0000-00-00 00:00:00'_mysql-connector-java-8.0.22 incorrect datetime val

- 6几道数据结构选择题_数据结构多选题

- 7唯一索引 oracle 空值,pgsql 组合唯一约束或唯一索引 null失效的情况

- 8【米哈游】2024秋招接近尾声,还没投递的抓紧上车啦!_深圳欣锐科技 计算机硕士 知乎

- 9FPGA实现的高效CIC滤波器:内插滤波器与数字信号多采样率处理_高效 数字滤波

- 10解决Win10找不到msvcp140_atomic_wait.dl文件_msvcp140-atomic-wait.dll

当前位置: article > 正文

verilog语法:reg与wire_virlog语言中wire和reg是什么意思

作者:2023面试高手 | 2024-05-23 18:13:58

赞

踩

virlog语言中wire和reg是什么意思

reg与wire

wire型数据常用来表示用于以assign关键字指定的组合逻辑信号。Verilog程序模块中输入输出信号类型缺省时自动定义为wire型。wire型信号可以用作任何方程式的输入,也可以用作“assign”语句或实例元件的输出。

reg型数据常用来表示用于“always”模块内表示时序逻辑电路,常代表触发器。通常,在设计中要由“always”块通过使用行为描述语句来表达逻辑关系。在“always”块内被赋值的每一个信号都必须定义成reg型。注意,always中的reg不一定只表示时序逻辑电路,也可以表达组合逻辑电路,取决于具体情况。

以上内容不过多介绍,书本上都有。下面介绍构建module和使用例化好的module时输入输出信号的类型要求。

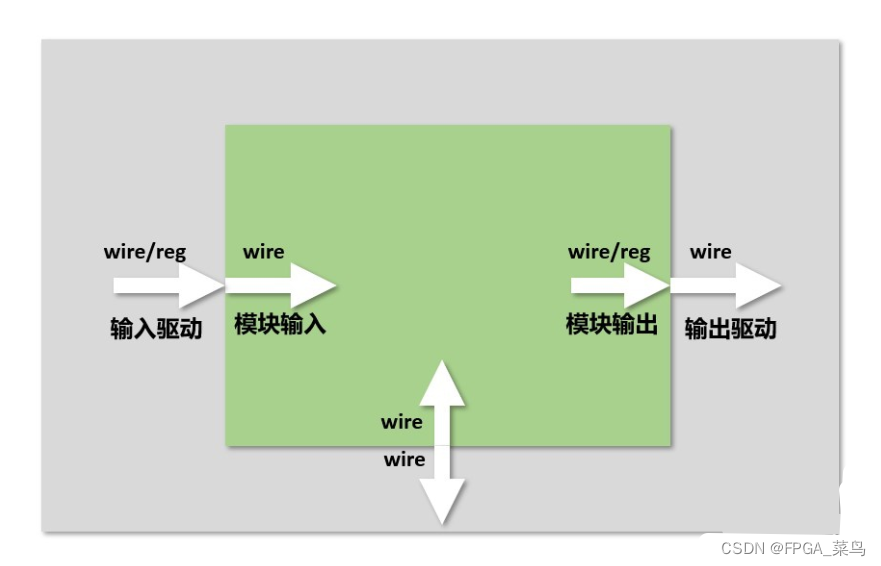

如上图,构建一个模块module时,

input必须是wire;(输入不定义默认就是wire)

output可以是wire也可以是reg;(输出不用赋值就默认wire,要赋值就定义reg)

inout必须是wire;

注:INOUT类型一般信号线用做总线等双向数据传输的时候。就是一个端口同时做输入和输出。 inout 在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻’Z’。当 inout 端口不输出时,将三态门置高阻。

使用例化好的模块时,

外部连接input端口的可以是wire也可以是reg;(比如写testbench时,与输入连接的通常定义为reg,但也可以是wire)

外部连接output端口的必须是wire;(参考test bench)

外部连接inout端口的必须是wire;

以上内容参考自下文:

链接: Verilog语法之三:变量

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/613911

推荐阅读

相关标签