热门标签

热门文章

- 1微信小程序使用wx.request()函数发送get和post请求到onenet平台_微信小程序下发命令到onenet

- 2学C++_第0章 引言/指南_0.2 编程语言简介_10110000是用哪种语言编写的?

- 3python telnetlib登录服务器并获取命令执行结果_telnetlib获取接收数据

- 4【滑动窗口】滑窗模板,在小小的算法题里滑呀滑呀滑_滑窗移动模型代码

- 5云计算的三种模式IaaS/PaaS/SaaS/BaaS对比:SaaS架构设计分析_云计算 iaas

- 6手把手教如何在VMware上安装redis_虚拟机上重装redis

- 7利用Git查看项目代码总行数_gitee如何查看代码总共有多少行

- 8Redis与MySQL数据库数据一致性方案

- 9go 简单实现Java线程池阻塞任务_goroot=d:\pojie-go\go-sdk #gosetup gopath=d:\gowor

- 10网站程序开发中的版本控制和代码管理工具介绍

当前位置: article > 正文

FPGA的ADC&DAC转换与检验(一)_fpga dac

作者:AllinToyou | 2024-04-20 20:53:09

赞

踩

fpga dac

之前跟小梅哥文档做的练手小实验,放上来做个总结。

本试验基于开发板上已有的ADC128S102CIMTX和DAC TLV5618a这两块芯片,他们的用户手册会随代码一同打包。

实验内容大概是:没有画图是因为了重装电脑,visio没下好,不是偷懒(

ADC芯片 ← ← ← ↑

↓ ↑

PC ← 串口发送 ←FPGA →DAC芯片 ↑

首先阅读用户手册:

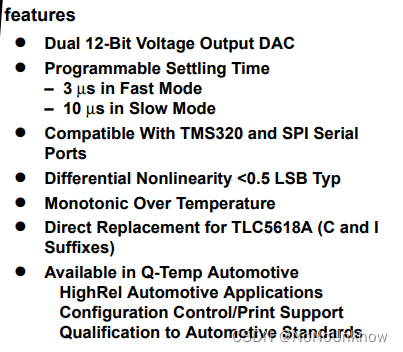

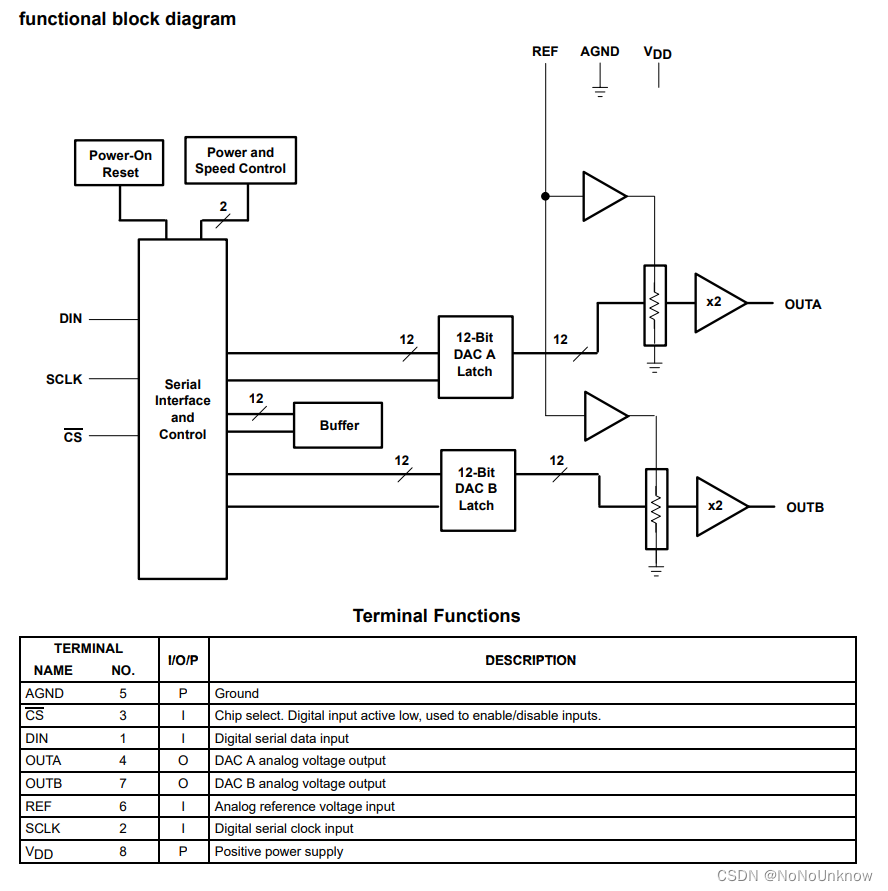

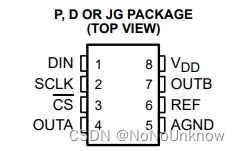

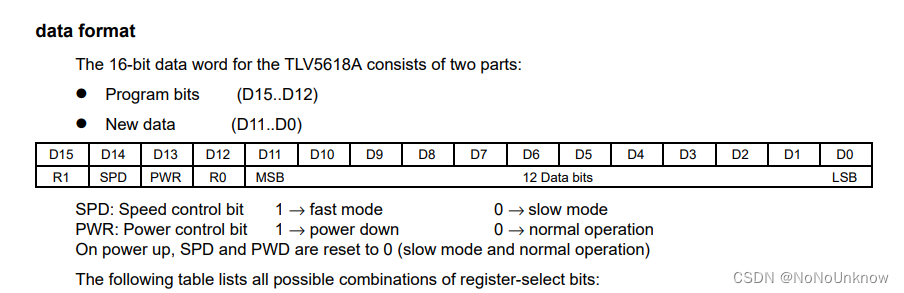

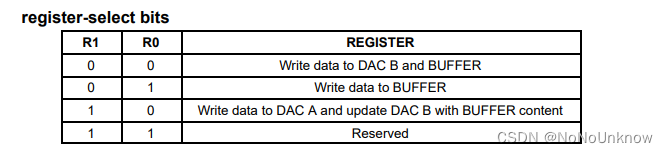

DAC手册:

12位两路电压输出,SPI协议。

非常简单。至少比我找CSDN怎么关水印要简单很多。

非常简单。至少比我找CSDN怎么关水印要简单很多。

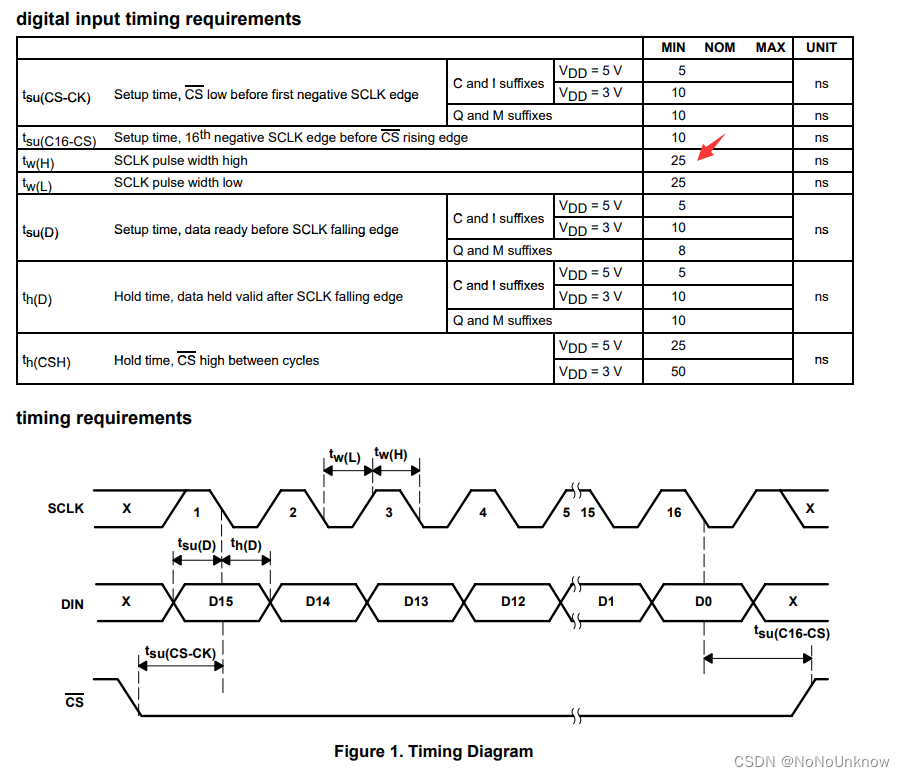

1/50ns→20mhz,信号保持一个周期问题不大,可满足su,hold time。

数据将在FPGA时钟上升沿修改,其在下降沿读取。

参数配置:通过同时控制双通道的有序输出,可以实现多位输出,但此处不做赘述。

代码如下:

///

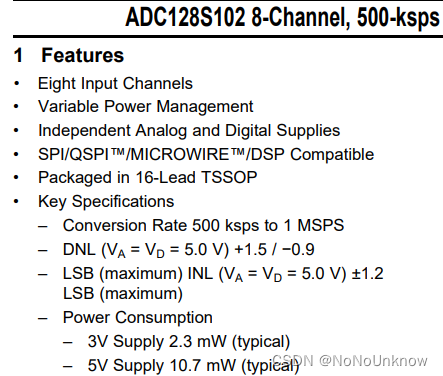

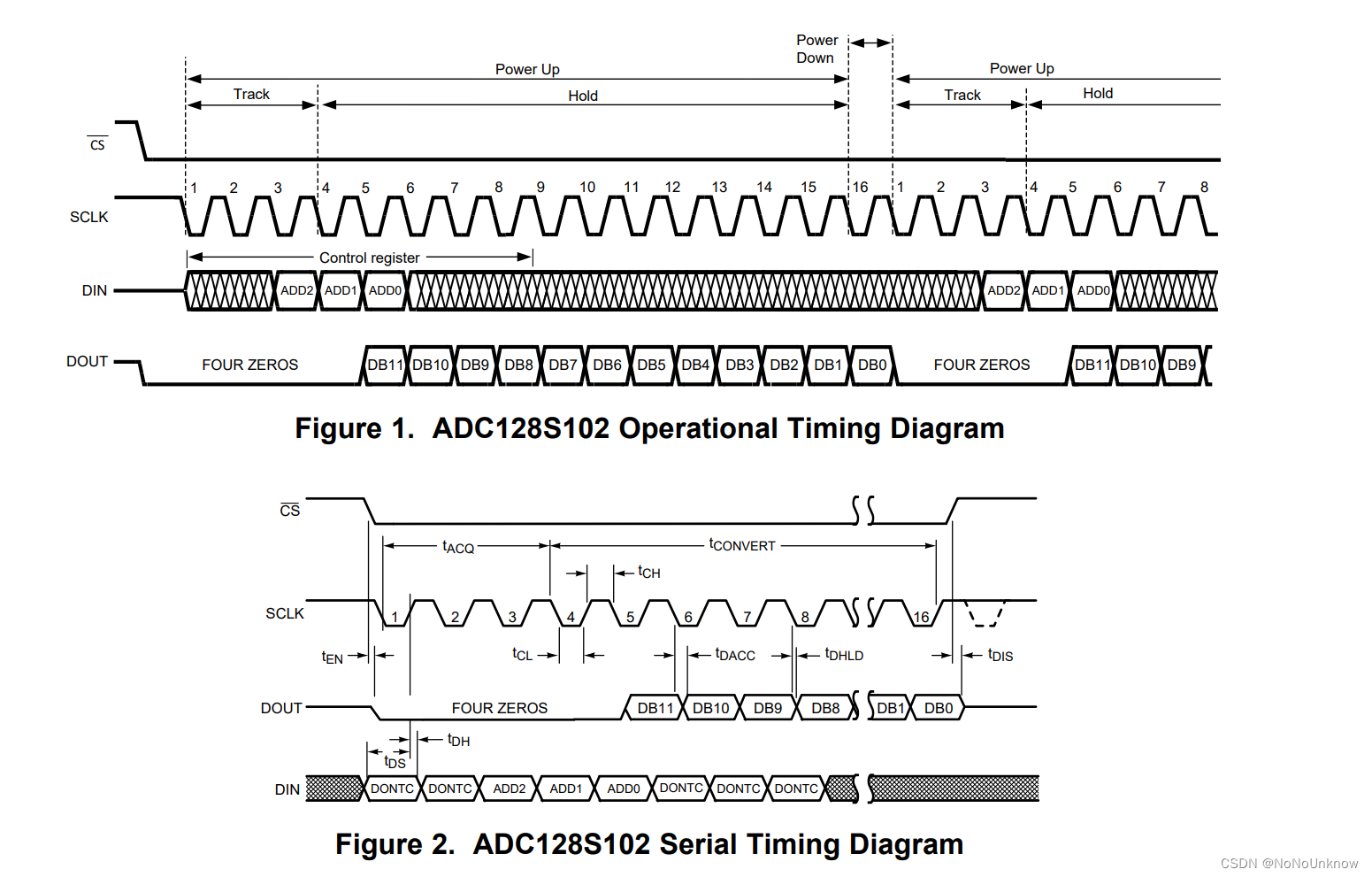

ADC手册:

值得一提:此处的DOUT输出的是上一轮ADDR的输出,毕竟ADDA的转换需要时间。

///

懒得写了,这个做的没意思,总结起来也很没意思,照着手册写完事。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/AllinToyou/article/detail/459314

推荐阅读

相关标签