- 1Dynamic partition strict mode requires at least one static partition column.

- 2python获取当天日期_python获取当前日期

- 3使用easyexcel将csv转为excel

- 4vue3【详解】 vue3 比 vue2 快的原因

- 5目前有哪些好用的测试管理工具?_测试任务管理工具

- 6Git学习_this key is not known by any other names.

- 7Debezium报错处理系列之五十六:common.errors.TimeoutException: Topic not present in metadata after 10000 ms_topic not present in metadata after 10000 ms.

- 8手把手教你玩转bat批处理:BAT文件语法和技巧_bat文件怎么编写

- 9学习C语言的优质网站_c语言学习网站

- 10Reason:NwHdlr: Network Error: chkauth: J_CHECKAUTH FAILED

FPGA/数字IC(芯海科技2022)面试题 2(解析版)_在静态时序分析中计算时钟延迟需要考虑以下哪些因素

赞

踩

以下仅为学习参考(非原创),如有疑惑欢迎评论区指出!

一、单选题(共20题,每题3分,共60分)

1. D触发器:Tsetup=3ns,Thold=1ns,Tck2q=1ns,

该D触发器最大可运行时钟频率是( )

A、1GHZ

B、500MHZ

C、250MHZ

D、200MHZ

解:C

最大可运行时钟频率与保持时间无关, 1/(Tsetup + Tck2q) = 1/4ns = 250Mhz

2.下列电路属于时序电路的是( )

A、编码器

B、译码器

C、数据选择器

D、计数器

解:D,计数一般是对时钟个数进行计数。

3.以下不能提高验证环境的可重用性的是

A、使用宏定义

B、使用绝对路径索引文件

C、使用factory进行重载

D、使用intertface进行连接

解:B

验证环境的可重用性:在项目管理,测试平台架构,验证计划,测试案例创建和脚本编写等方面的不改动或稍加改动就可以重复使用过的能力。

C. 推荐学习UVM当中的factory的重载函数

D. 更简便的接口连接方式

4.组合逻辑电路的冒险现象是由于( )引起的

A、电路存在延时

B、电路有多个输出

C、电路未达到最简

D、逻辑门类型不同

解:A

5.关于Task与Function语句,以下正确的是()

A、在Function中,可以调用Task

B、Function至少有一个输入变量

C、function必须要有返回值

D、Task可以有返回值

解:B

6.数字电路设计中,下列哪些手段无法消除竞争冒险现象( )

A、增加冗余项消除逻辑冒险

B、降低时钟频率

C、增加选通信号,避开毛刺

D、加滤波电容,消除毛刺

解:B

7.关于代码覆盖率,描述正确的是

A、代码覆盖率不包括toggle覆盖率

B、代码覆盖率包括line覆盖率

C、代码覆盖率包括功能覆盖率

D、代码覆盖率达到100%,表示验证足够完备,可以停止验证

解:B

8.关于正则匹配,描述错误的是

A、\w可以匹配a-z、A-Z以及0-9,无法匹配下划线

B、\s可以匹配任意空白符,包括换行符

C、^表示一行的开头

D、\d可以匹配0-9

解:A

. 匹配除换行符以外的任意字符

\w 匹配字母或数字或下划线或汉字 等价于 '[^A-Za-z0-9_]',能不能匹配汉字要视你的操作系统和你的应用环境而定

\s 匹配任意的空白符

\d 匹配数字

\b 匹配单词的开始或结束

^ 匹配字符串的开始 $ 匹配字符串的结束

9. UVM中以下描述正确的是

A、connect_phase的执行是自上而下

B、reset_phase在main_phase之前执行

C、可以在build_phase进行objection的raise

D、build_phase的执行是自下而上

解:B

10.关于异步复位,描述错误的是

A、数字设计经常使用异步复位同步释放

B、异步复位可以节省资源

C、使用异步复位有利于进行时序分析

D、异步复位对毛刺很敏感,抗干扰能力差

解:C 复位信号容易受到毛刺的影响,不利于时序分析。

11. 关于动态数组和队列,描述错误的是

A、动态数组需要调用delete函数释放空间

B、队列在扩大时,sv会自动分配空间

C、动态数组和动态队列实例化使用new[]

D、队列相关函数包括pop_front()、push_back()

解:C,队列不需要new[ ]。

12. 有一个FIFO设计,输入时钟100MHz,输出时钟70MHz,输入数据模式固定,其中1000个时钟中有700个时钟写传输连续数据。为了避免FIFO下溢/上溢,FIFO最小深度是多少(C)

A、360

B、1170

C、420

D、270

解: C ,当读数据的速率小于写数据的速率时,需要先将数据缓存下来,那么需要开多大的空间缓存这些数据就需要确认FIFO最小深度。

FIFO_Depth >= Burst_length -Burst_length* (rd_clk/ wr_clk)*(rd_rate)

此题未涉及rd_rate,为使FIFO_Depth最大,rd_rate = 1

2*700-2*700*(70/100)= 420

13.芯片中有关GPIO的叙述,不正确的是( )

A、GPIO般只具有0态和1态,不具有高阻状态

B、GPIO的引脚般是多功能复用的

C、GPIO作为输入接口时具有缓冲功能

D、GPIO作为输出接口时具有锁存功能

解:A

14.下面关于AHB协议描述错误的是

A、Burst传输不能跨越1KB地址边界

B、HRESP[1:0]有OKAY、ERROR、SPLIT和RETRY

C、Burst传输包括single传输、定长传输和不定长传输

D、读写操作的地址相位只会维持1拍时钟

解:D

15.下面哪个不属于跨时钟域数据传递的基本方法( )

A、信号通路上插入isolation

B、使用FIFO

C、使用多级触发器缓冲

D、使用握手协议

解:A,isolation隔离是为了降低功耗。

16.以下为文件后缀为某代工厂提供的库文件,合法的电压,环境温度范围内,以下哪种情况内部信号速度最快( )

A、SS_-40°C

B、FF_-40°C

C、SS_125°C

D、FF_125°C

解:B,

由于工艺偏差,即使在同一圆片上的芯片,就是不同位置的器件属性会有所不同。单一器件所测的结果为正态分布,均值为tt,最小最大限制值为ss与ff。温度低比温度高信号转递更快。

17.以下Verilog运算符优先级由高到低正确的是( )

A、&,|&&,^,!

B、^,!,&,|,&&

C、!,|,&,&&,^

D、!,&,^,|,&&

解:D,不确定时使用括号决定顺序。

18.下面哪个phase属于task phase(D)

A、connect phase

B、build phase

C、report_phase

D、reset phase

19.以下不能对多bit的数据总线的时钟异步处理的是( )

A、Gray-code

B、寄存器同步

C、FIFO

D、Dmux synchronizer

解:B, 寄存器同步只适用于单bit信号

20.关于’uvm_do_on和’uvm_do_on_with,表述正确的是(B)

A、在使用之前对应的对象需要进行实例化

B、都有三个参数

C、第二个参数可以是virtual sequencer

D、第一个参数必须是transaction指针或者sequence指针

二、多选题(共 10 题, 每题 4 分, 共 40 分)

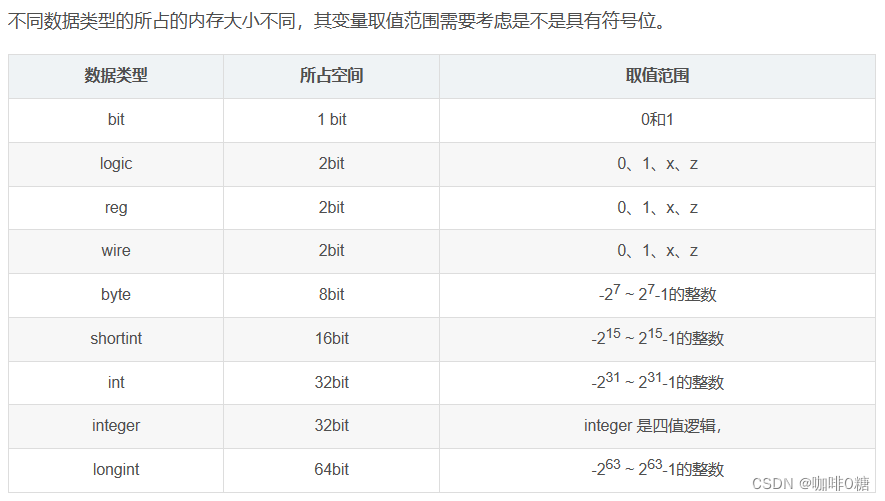

1.下面属于双状态数据类型的是(AC)

A、byte

B、logic

C、bit

D、integer

2.在静态时序分析中计算时钟延迟需要考虑以下哪些因素()

A、时钟源的抖动(jitter)

B、寄存器的建立和保持时间

C、时钟树不平衡引入的偏差(skew)

D、工艺特性造成的on-chip variation

解:ACD,建立时间和保持时间影响的是传输数据的稳定性。

3. 以下逻辑能实现:输入三个1bitA,B,C变量,若其中两个以上变量为1,则输出1:()

A、x=(A&B)|(B&C)|(C&A)

B、x=(~A&B|~B&A)^C

C、x=(~A&B|~B&A)?C:A

D、x=(~A&B|~B&A)?C:B

解:A、B、C、D 归约与(&),归约与非(~&),归约或(|),归约或非(~|),归约异或(^),归约同或(~^)。

4.如下verilog描述中哪个或者哪几个会生成寄存器()

A、always@(clk)

reg_a<=reg_b;

B、always@(negedge clk)

reg_a<= reg_b;

C、always@(posedge clk)

reg_a<=reg_b;

D、assign reg_a=reg_b;

解:BC

5. 在不增加pipeline的情况下,如何解决一条critical path的setup时序不满足的问题?(ABC)

A、将部分组合逻辑电路搬移到前级path上

B、使用更先进工艺的工艺库

C、降低时钟频率

D、在这条path上插入寄存器

6.关于重载,下面描述正确的有()

A、函数、任务可以被重载

B、transaction可以被重载

C、sequence不能被重载

D、UVM factory机制的重载要求重载的类必须派生自被重载的类

解:ABD

7.对改善亚稳态问题有效果的方法是(ABCD)

A、引入同步机制,如加两级触发器

B、降低时钟频率

C、改善时钟质量,用边沿变化快速的时钟信号

D、用反应更快速的DFF

8.有关virtual sequencer描述正确的是(ABC)

A、virtual sequencer并不和任何driver相连

B、virtual sequencer可以控制其他sequencer

C、sequence并不在virtual sequencer里产生和传递

D、virtual sequencer自身可以传递transaction

9.下列哪些class派生来自uvm_component(ABD)

A、Sequencer

B、Monitor

C、Transaction

D、Driver

10.关于线程,以下描述正确的是(AB)

A、disable语句可以提前结束所有线程

B、fork...join、fork... join_none、fork...join_any语句块都是以并发方式执行

C、fork...join_none内部的任意一个语句块执行完成之后,父线程才能继续执行

D、fork...join_any内部的所有语句块执行完成之后,父线程才能继续执行