- 1【力扣(LeetCode)】【C/C++】【21.合并两个有序链表】_力扣 合并两个有序链表c++

- 2LeetCode //C - 31. Next Permutation

- 3机器学习在医疗行业的应用:颠覆传统诊疗模式,开启智慧医疗新时代

- 4ElastchSearch 基本使用姿势_elastsearch 中文查询问题

- 5C语言使用第三方库编译报错错误排查_evp_sm4_gcm

- 6论文解读:(TransH)Knowledge Graph Embedding by Translating on Hyperplanes_transh原文

- 7LLM - 大模型技术报告与训练细节 By Baichuan2_llm 模型训练

- 8Hive安装(超详细)_hive的前置安装有哪些

- 9vivado时序违例相关_vivado 保持时间违例

- 10掌控安全 -- header注入_header存在注入危险,访问已被禁止

【蓝桥杯EDA设计与开发】立创开源社区分享的关于蓝桥被EDA真题与仿真题的项目分析_蓝桥杯eda真题

赞

踩

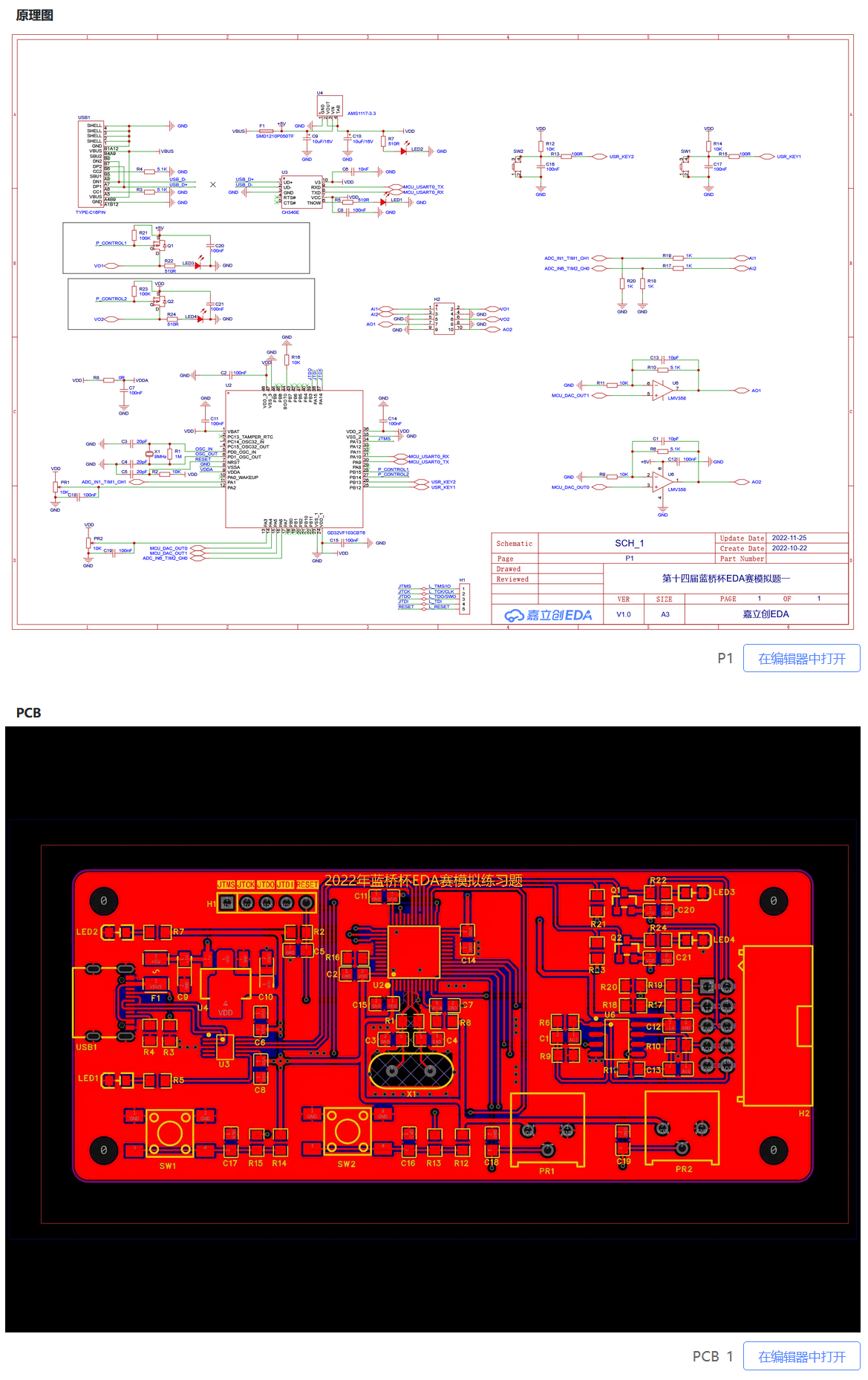

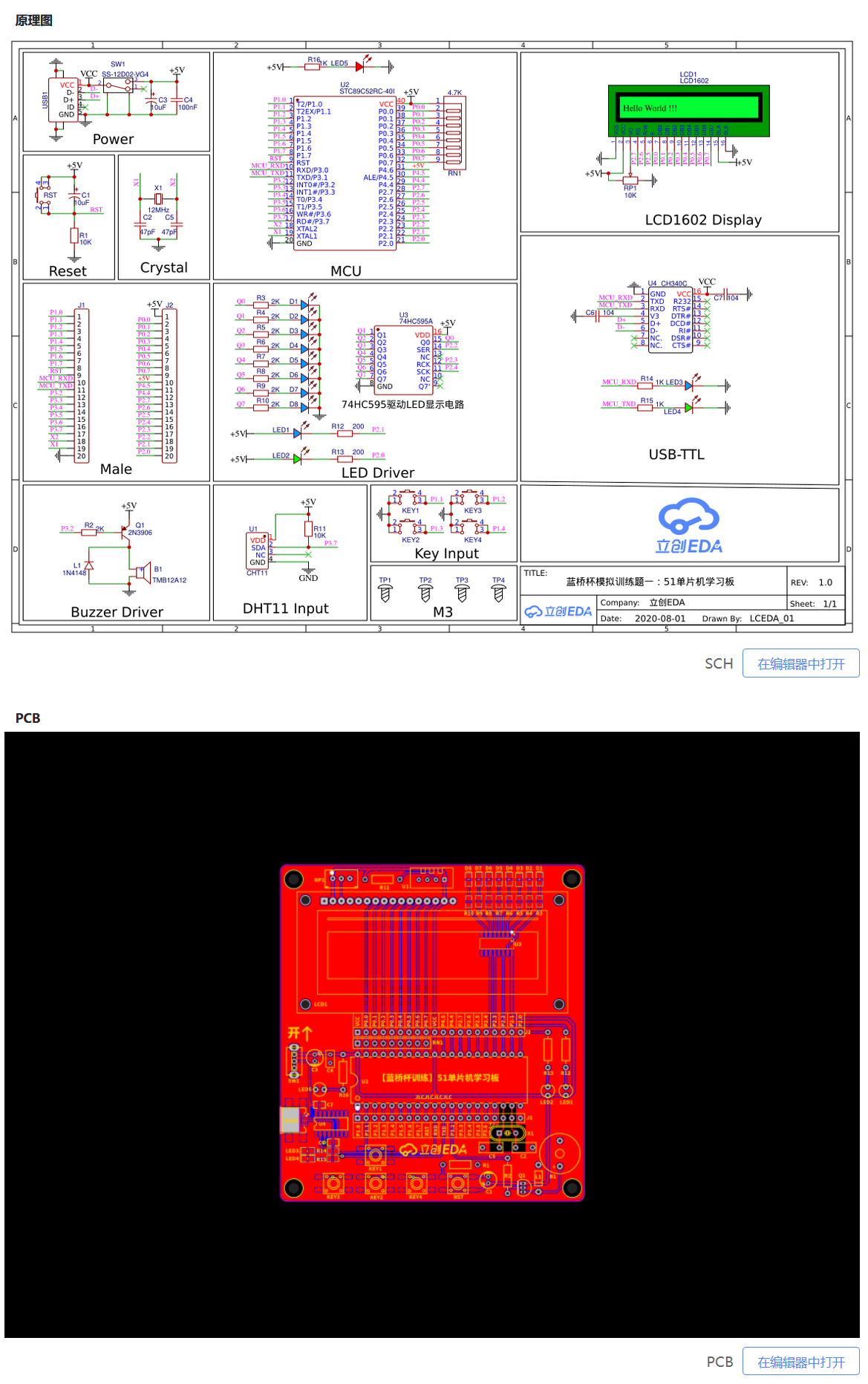

立创开源社区内有几个项目分享了往年 EDA 设计题目与仿真题,对此展开了学习。

【本人非科班出身,以下对项目的学习仅在我的眼界范围内发表意见,如有错误,请指正。】

项目一

来源:第十四届蓝桥杯EDA赛模拟题一 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/di-shi-si-jie-lan-qiao-bei-eda-sai-mo-ni-ti-yi

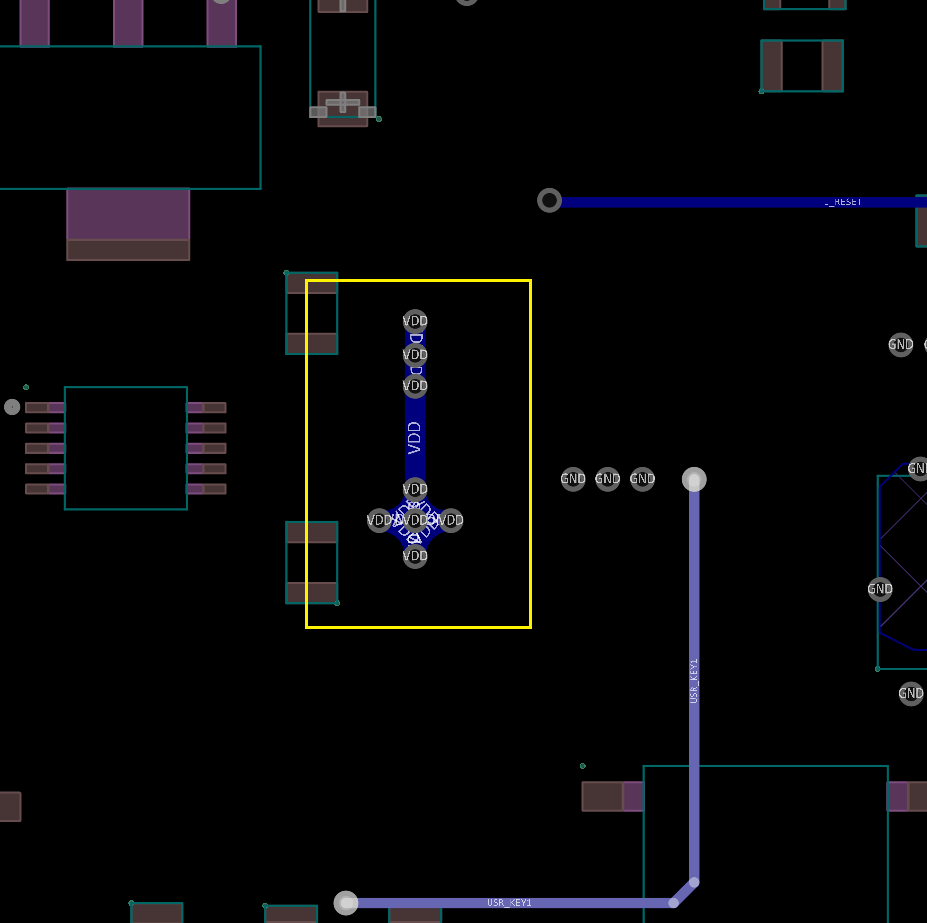

连线交叉点处,应避免出现黄色框中的现象,尽量使用蓝色框中的形式。

图中VDD的形式,在这种情况下,采取小范围铺铜的形式更为恰当,参考 图 1-2 中的 AMS1117 下的铺铜区域。

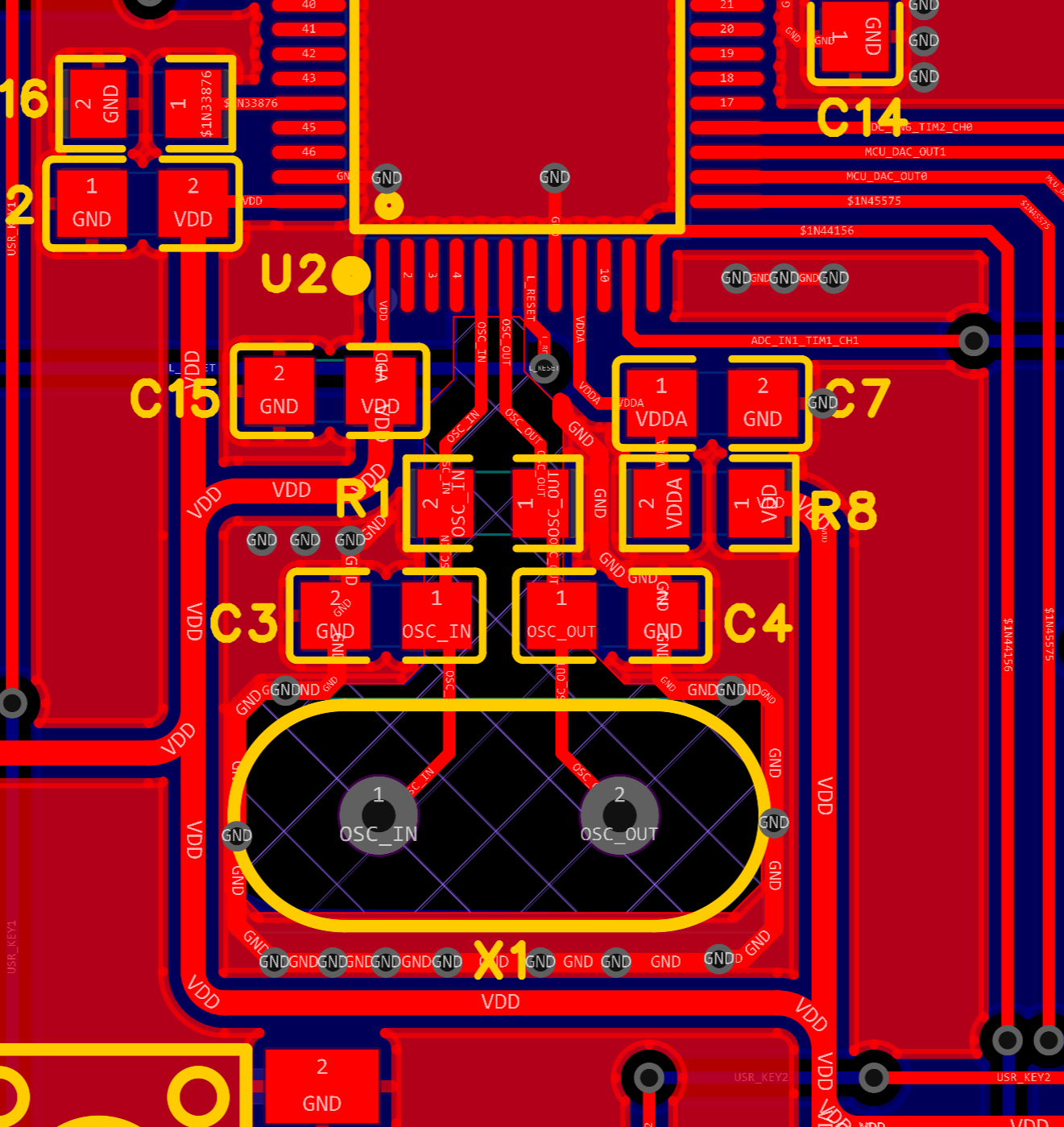

GD32 的晶振附近包铜区域设计不合理,包铜区域应包括晶振、电容、电阻以及晶振到单片机之间的通路,其通路旁的其他元件及走线阻碍了包铜区域的延申。

在项目一中,单从PCB图上来看,问题大致有几点:(1)走线转弯处圆弧与45°走线方式混用。(2)走线线宽不合适当前线径电流情况。(3)布局不合理,出现不必要过孔。(4)走线路径不合理,导致信号线过长占用板上空间。

对此PCB文件来说,整体上还是没什么大问题,算的上是一个还可以的PCB设计。

其余问题可参考其他项目列出需注意问题。

项目二

来源:2022年蓝桥杯EDA设计组-省赛 - 嘉立创EDA开源硬件平台

https://oshwhub.com/aoao_sama/2022nian-lan-qiao-bei-EDAshe-ji-

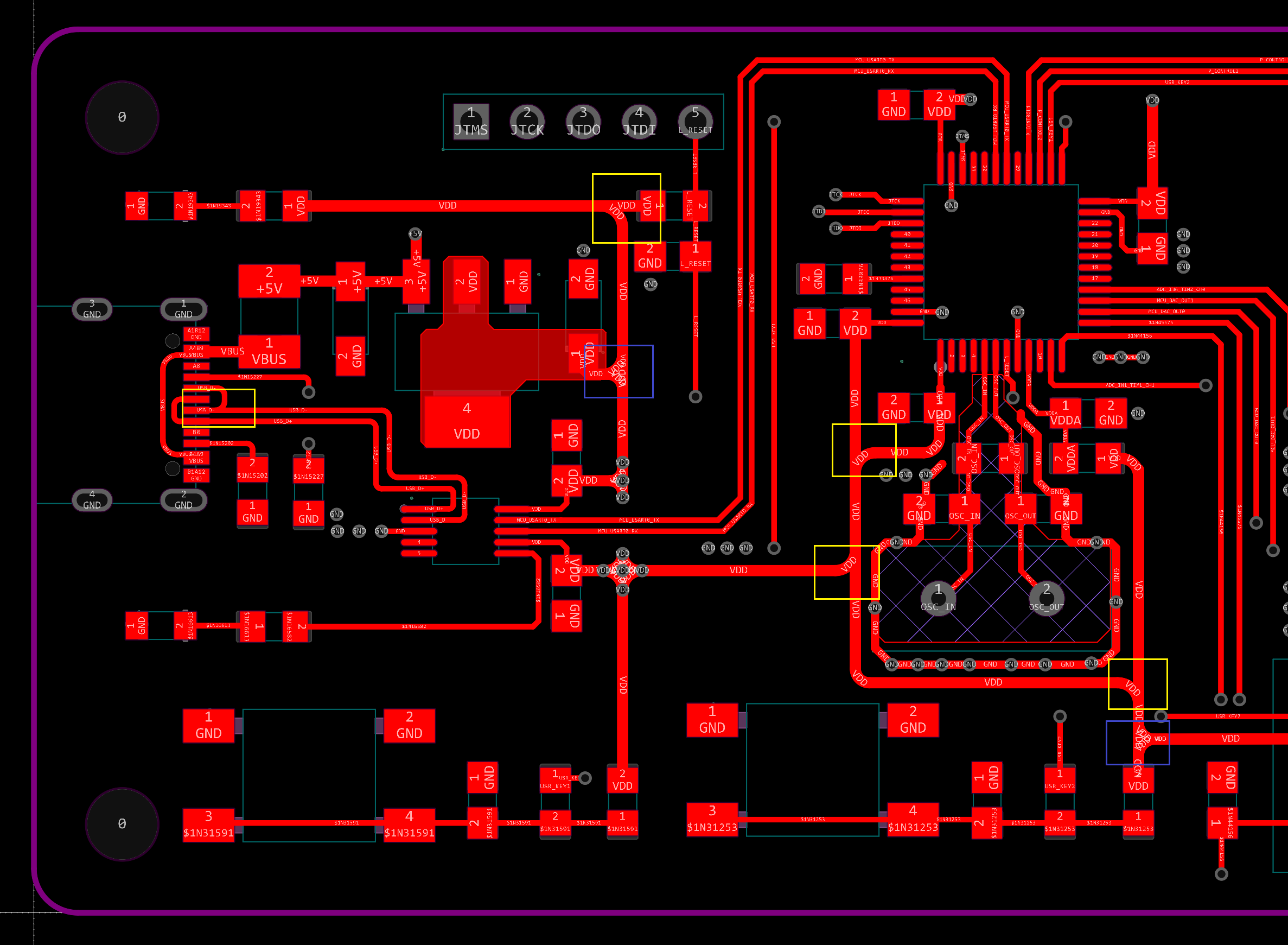

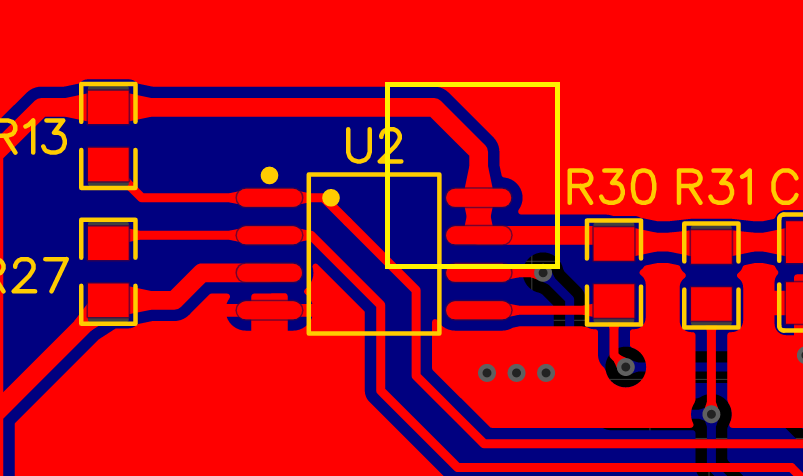

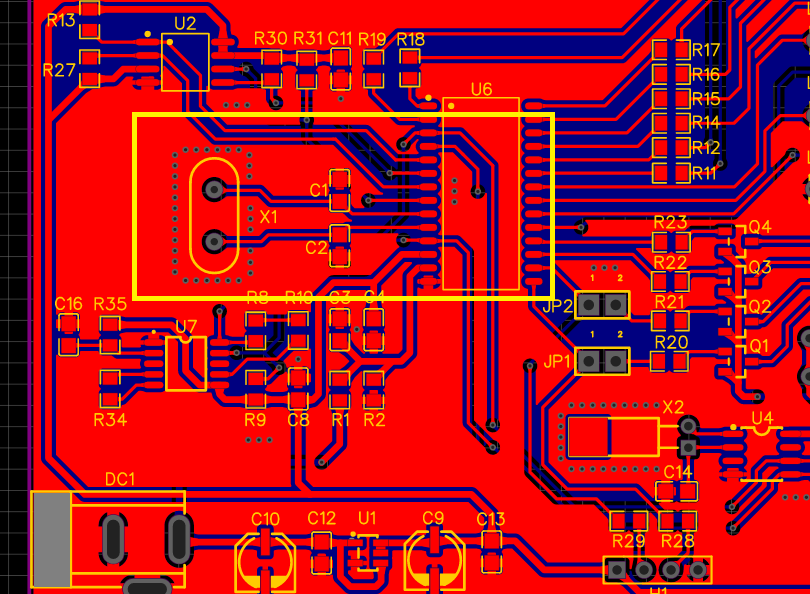

在U2的引脚中,出现芯片引脚侧边出线的状况,一般情况下芯片引脚侧边出线是不可取的,需要谨慎对待,此类情况还出现在U1、U3、U6、U7中。图中黄色方框圈出所示。

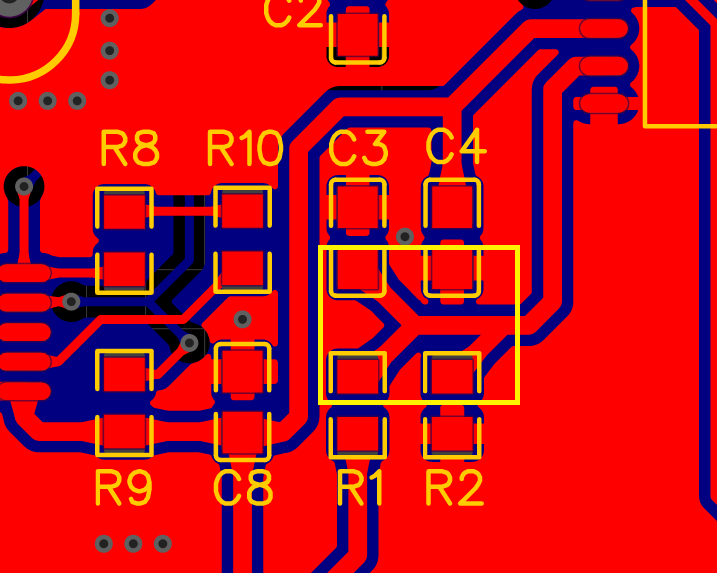

在图中黄色方框圈出所示中,C3、R1、R2在走线连接上有从焊盘脚引出的走线方式、一般有走线空间的情况下,应避免此类情况。还由于斜走线引入了钝角,应避免。

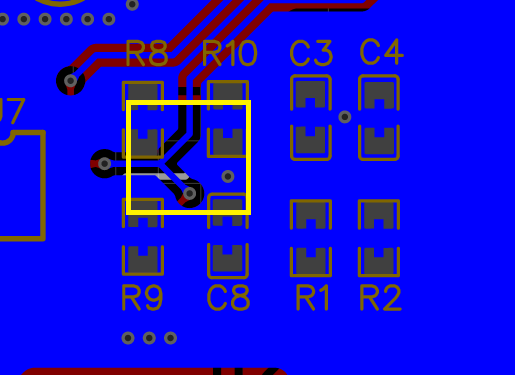

底层走线中,有两引线相连引入不合适角度的问题,此类走线角度问题在本项目中较多,绘制PCB时应注意。

其中还有X1晶振与电容的距离较远,布置不合理的问题,应使得晶振与电容以及芯片之间走线距离尽可能短。另外X1晶振外壳起到防干扰的作用,晶振附近的过孔布置不大合理,而且没有完全包裹由晶振到芯片之间的时钟通路。

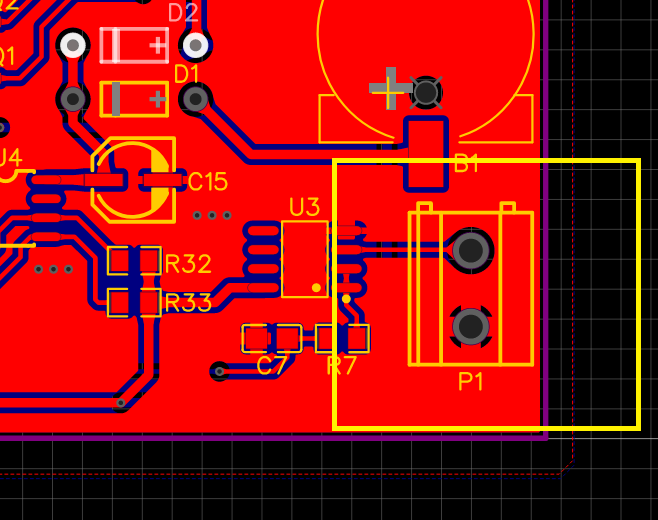

P1端子座放反了你们有没有看见???在3D视图上有体现,接线口应该朝向右面,结果朝向左面了。这种问题在原理图上极易画错,而且不容易注意到!绘制时应该谨慎再谨慎。

尽量避免在走线正中间打过孔,布局方面还可以再做优化,绘制PCB时用上了泪滴,这是一个很好的选择。

其余问题可参考其他项目列出需注意问题。

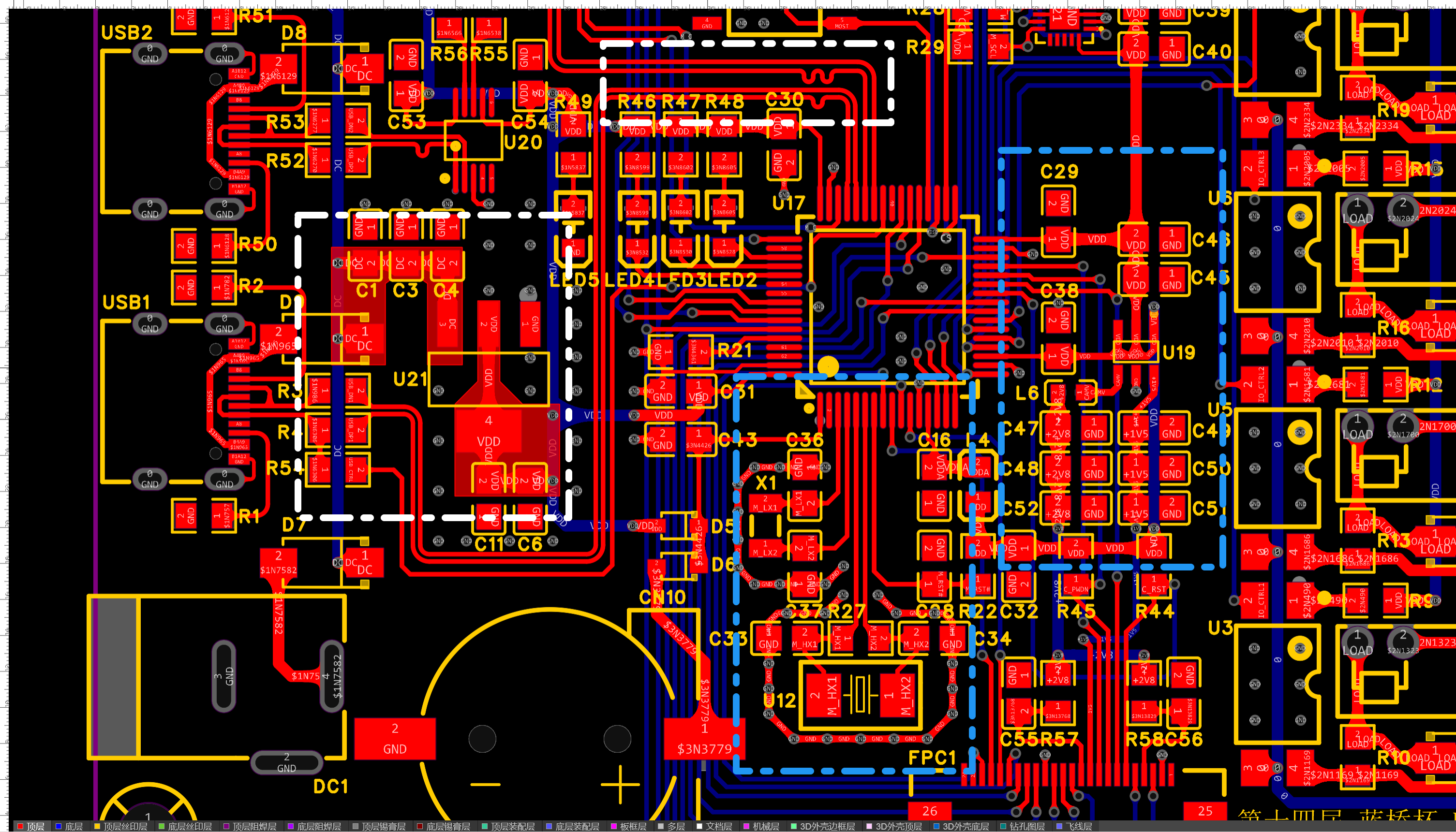

项目三

来源:【蓝桥杯练习题三】智能平衡小车 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/kao-ti-zhi-neng-ping-heng-xiao-ju_transfer

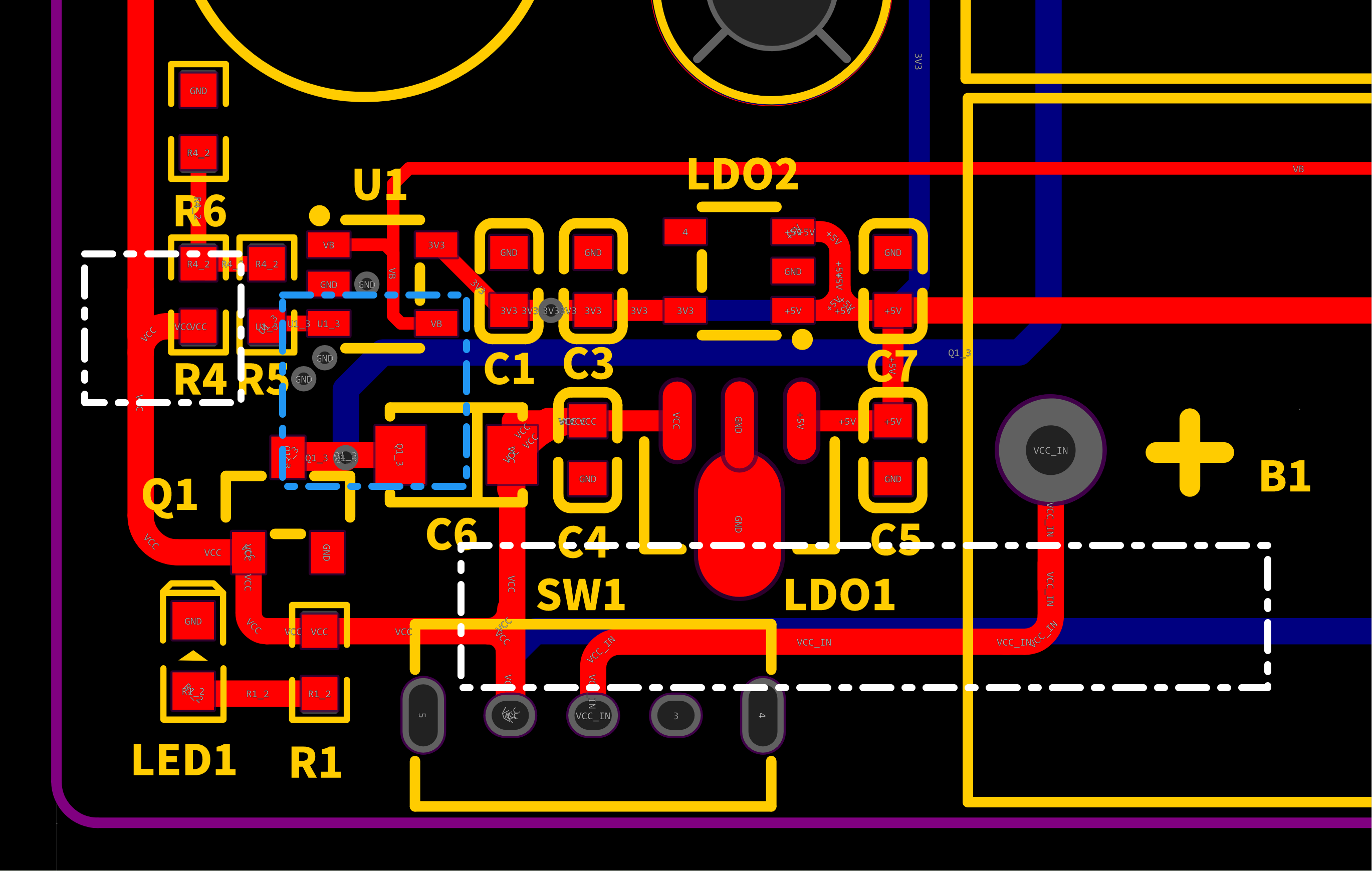

在大电流部位或者是多个相同网络标号的引脚相靠密集时,使用铺铜方式是一种很好的选择,如图3-2的高亮部分。

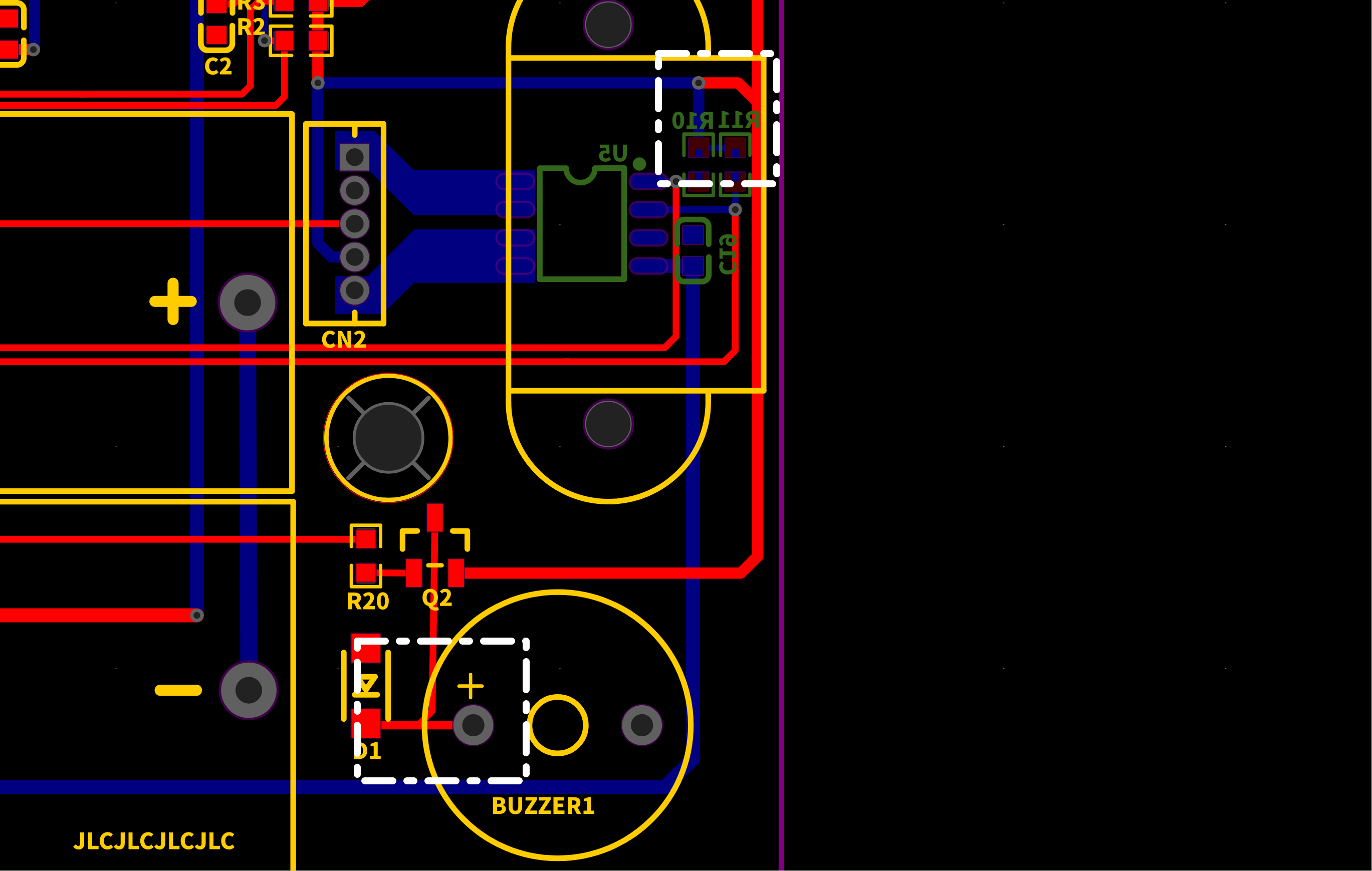

左侧白框:交叉线相连不宜采取这种角度,会产生较大锐角。上述曾说过此连接方式。

蓝色方框:尽量不要圆弧和45°角混用的拐角方案,以追求美观而采用圆弧不太可取且没有必要。

下侧白框:两条线相平行的方式走线,在此处都为电源走线的情况下影响不大,但是在不同信号的信号线情况下,应尽量避免!

白色框:交叉线相连不宜采取这种角度,会产生较大锐角。上述曾说过此连接方式。如此建议后面不再赘述。

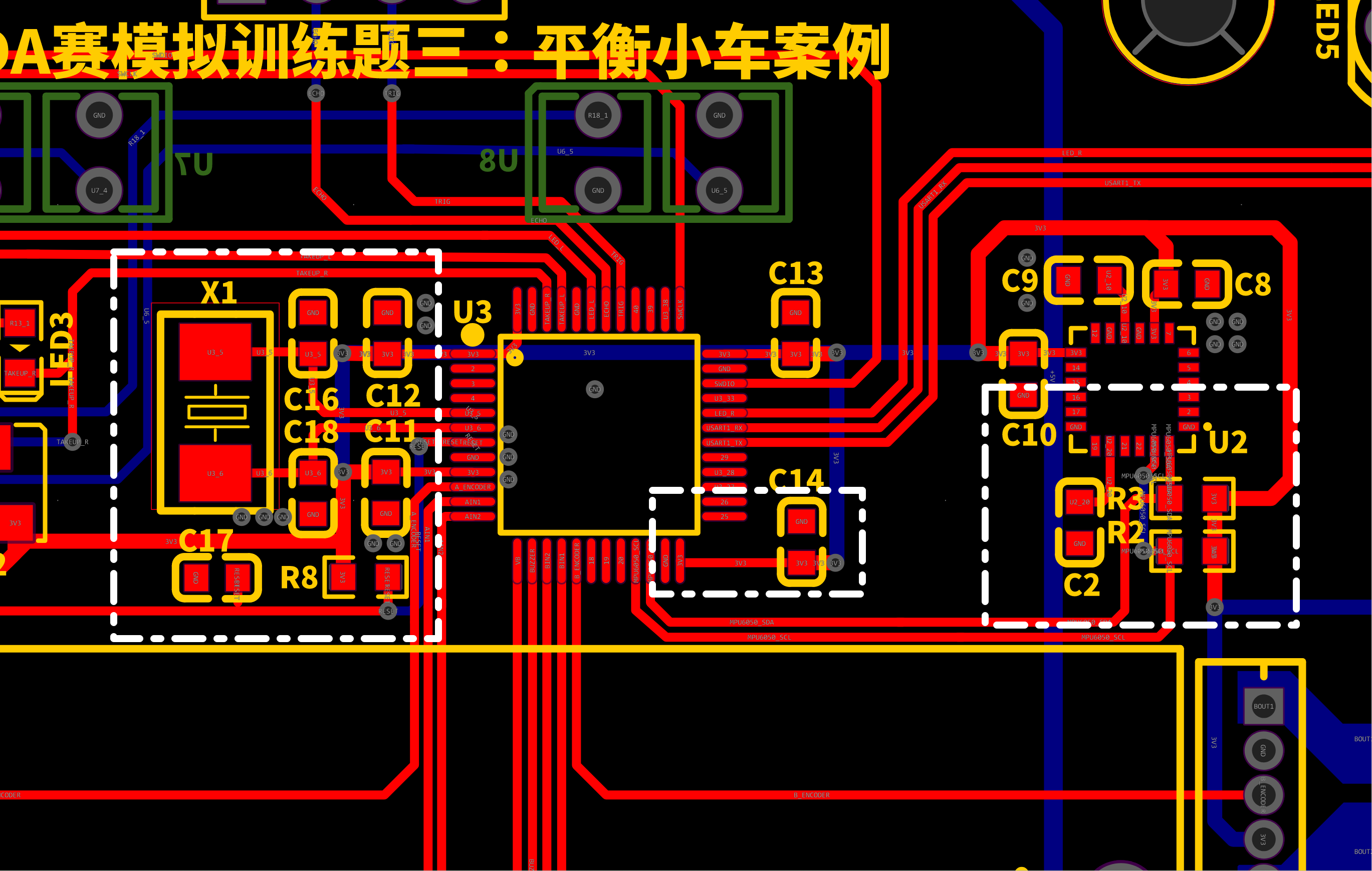

左侧白框:布局不合理,电源滤波电容C11、C12布置不合理,影响晶振电路部分的时钟信号质量。C17、R8为RESET自动复位外围器件,离芯片太近,影响芯片走线,可放远一点,让出走线空间。

中间白框:C14和U3之间的连接不应该在U3的引脚侧边出线,应避免。建议:可用铺铜方式引出。

右侧白框:布局影响走线,导致走线难度加大。布局不合理情况在此项目较多。

另外,有较多处存在同类贴片元件未对齐的情况,应该避免。

项目四

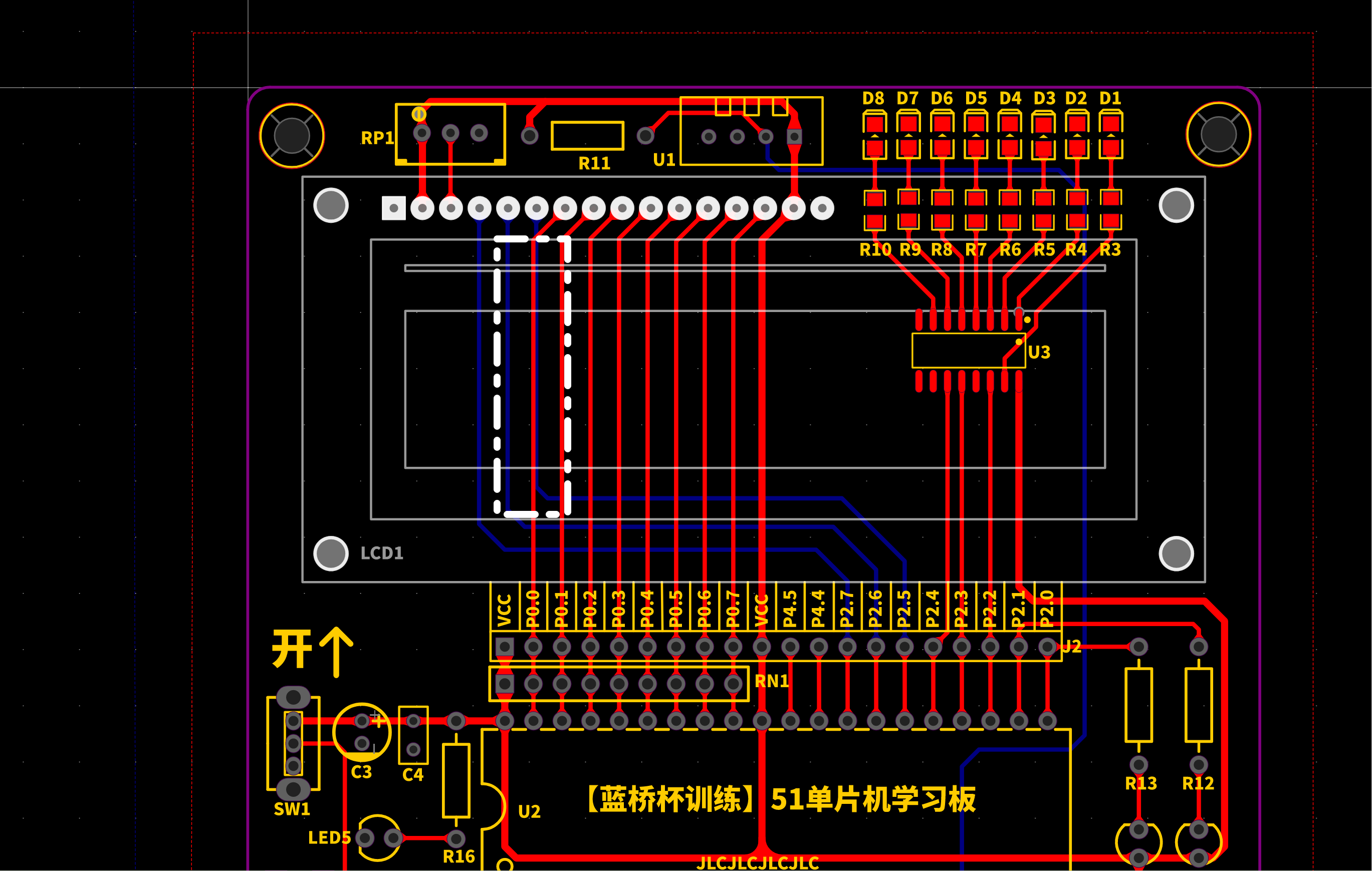

来源:【蓝桥杯练习题一】51单片机开发板 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/kao-ti-51-dan-pian-ji-kai-fa-ban

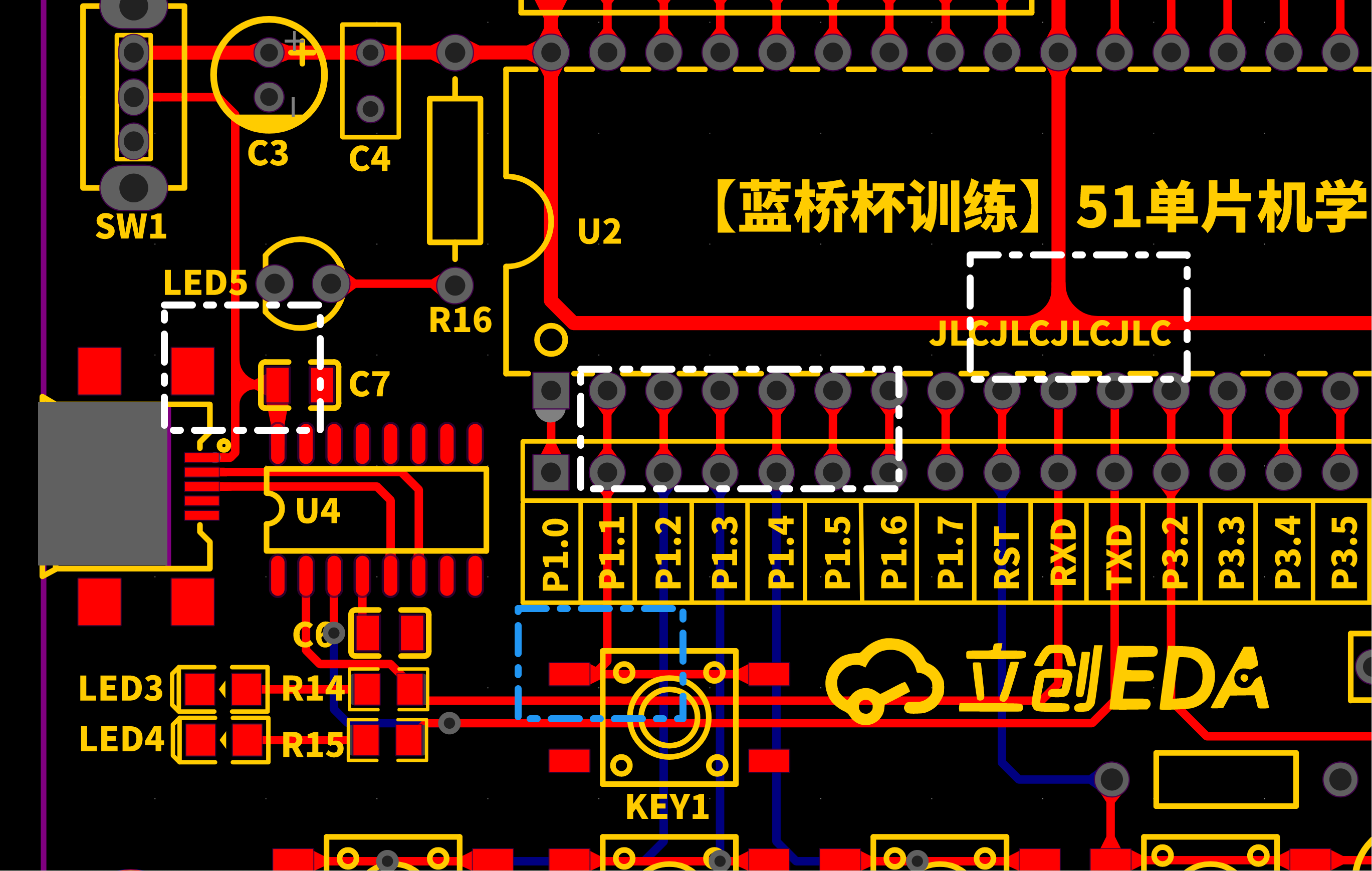

白框:T形交叉线方式值得借鉴,且采用了泪滴。

蓝框:走线方式避免,可采取两根走线在焊盘不同的边引出。

总体来说,此项目无过多需要注意点。比较简单。项目用时建议在两小时内。

电源走线注意线宽,会影响评分。

信号线避免平行&重合。高频信号影响很大,在此类项目中影响较小。

项目五

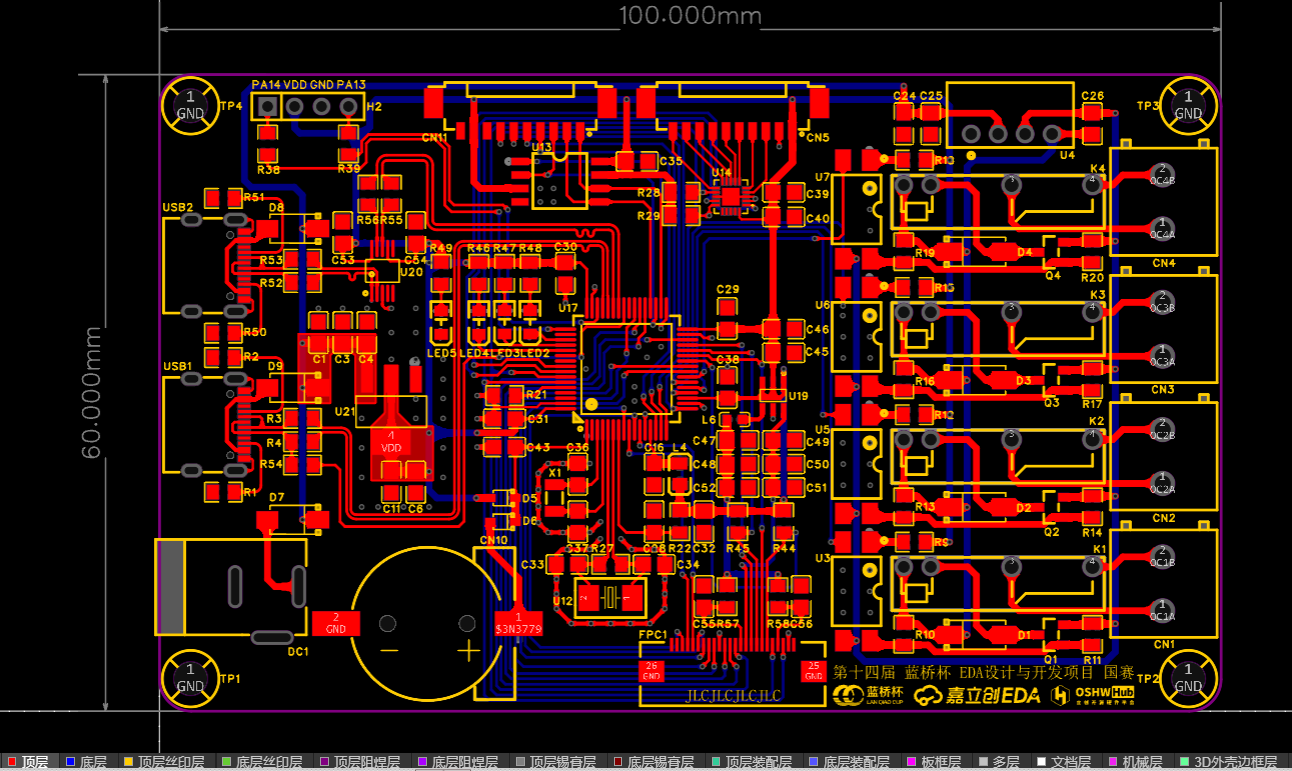

来源:第十四届 蓝桥杯 EDA设计与开发项目 国赛 真题 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/di-shi-si-jie-lan-qiao-bei-eda-sai-guo-sai-zhen-ti

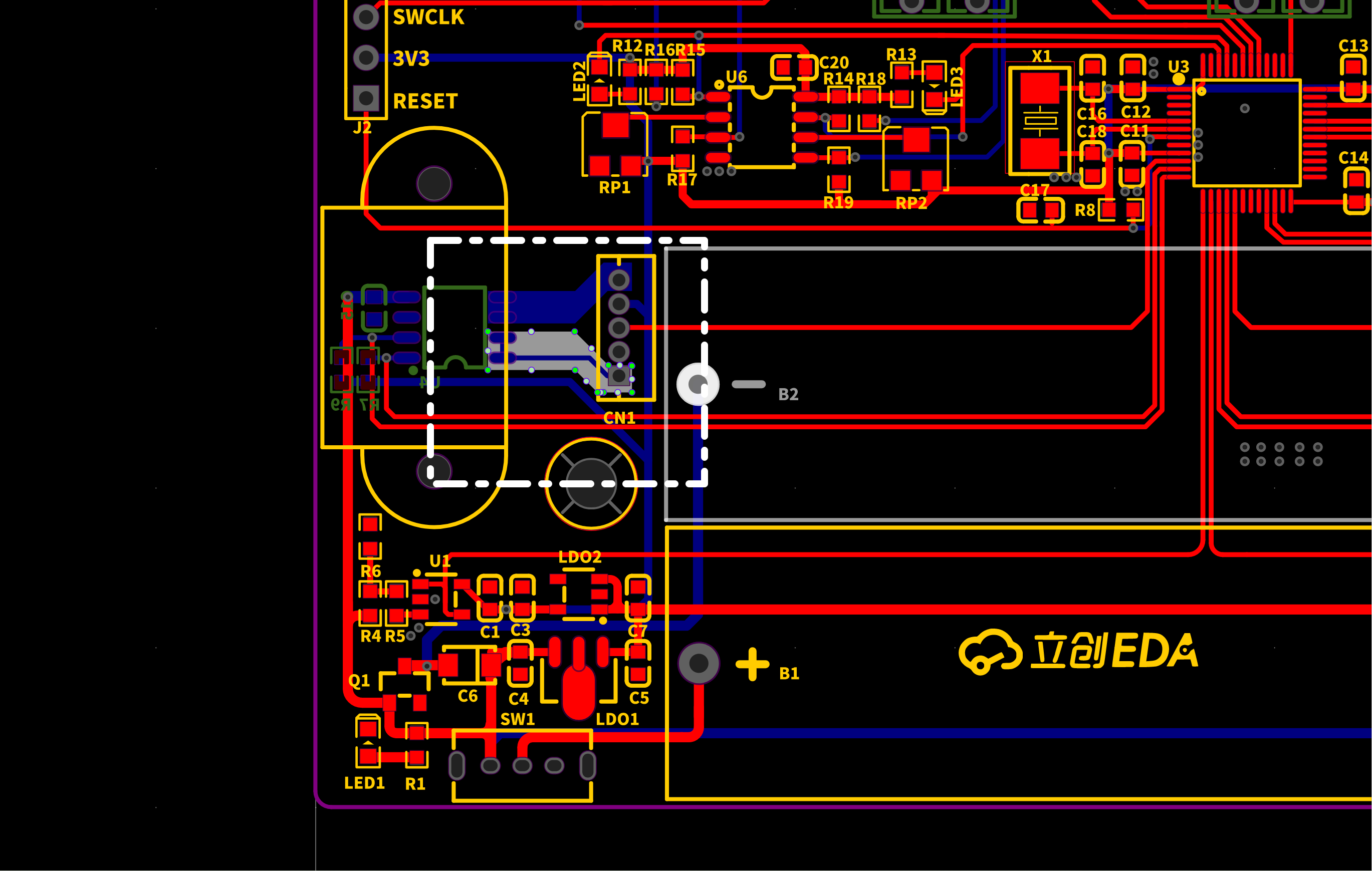

左侧白框:电源以及电源滤波电容之间采用铺铜连接,值得学习

上侧白框:差分信号采用等长处理,绘制PCB时应注意差分信号对的连接线等长处理。

下侧蓝框:时钟晶振的包地处理尽量包括时钟信号线,不要紧紧包括晶振及起振电容。时钟线较长,尽量缩短主晶振时钟的连线距离。

右侧蓝框:多个电源引脚部分可采取铺铜连接,类似左侧白框情形。

多个过孔在一起是,可采取交错排列的形式,如图5-4。

本项目PCB绘制非常好,值得学习!!!

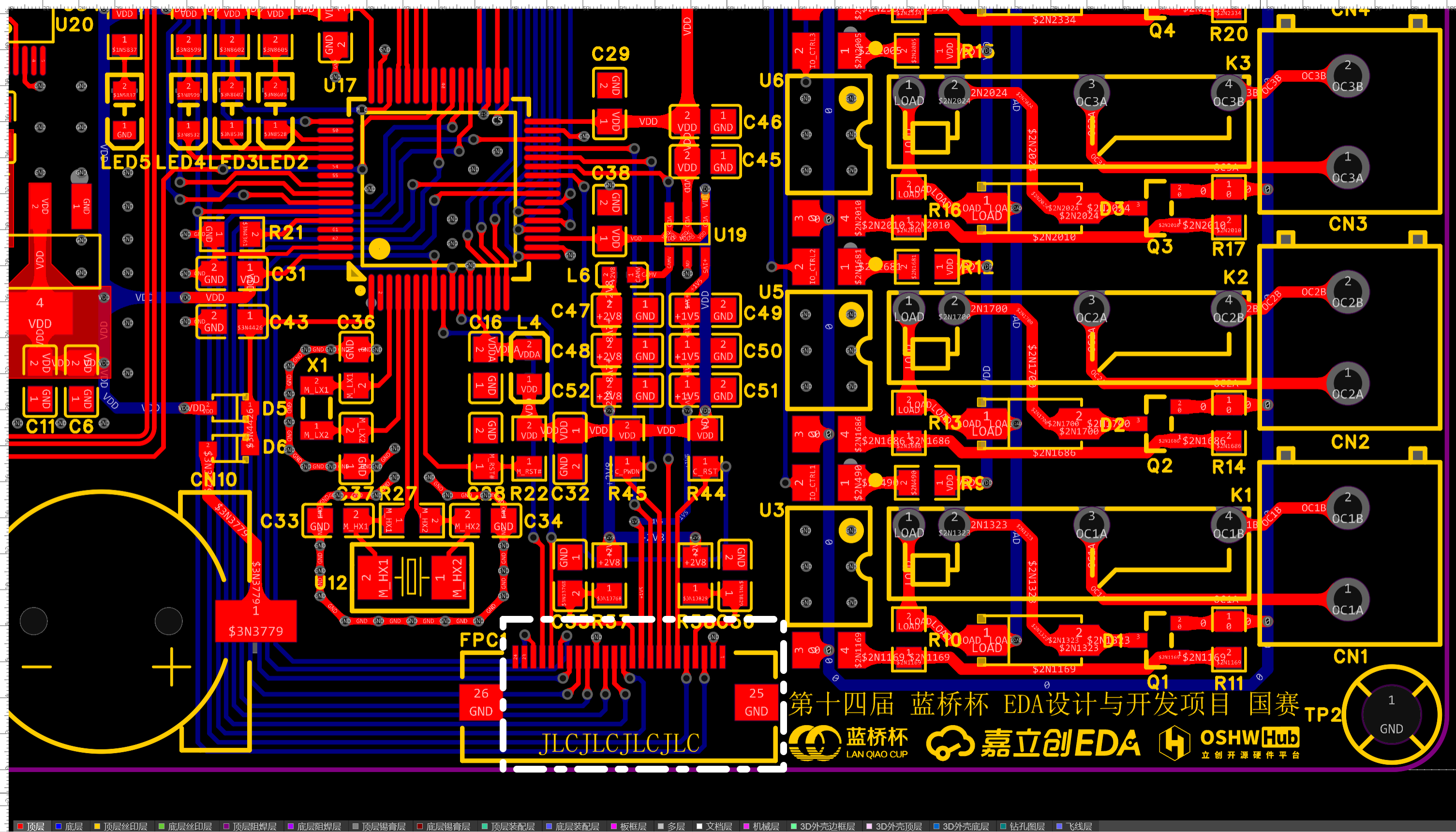

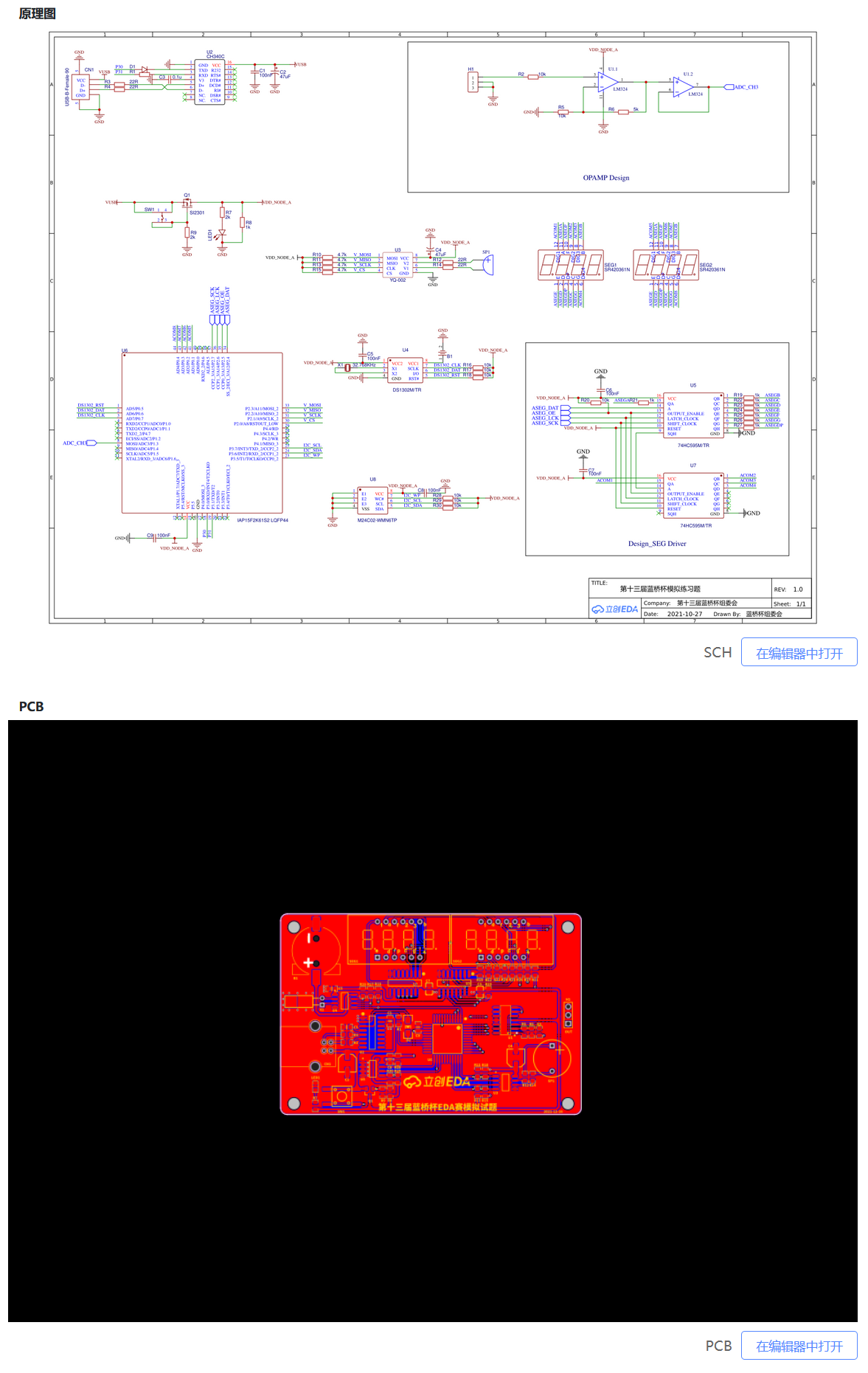

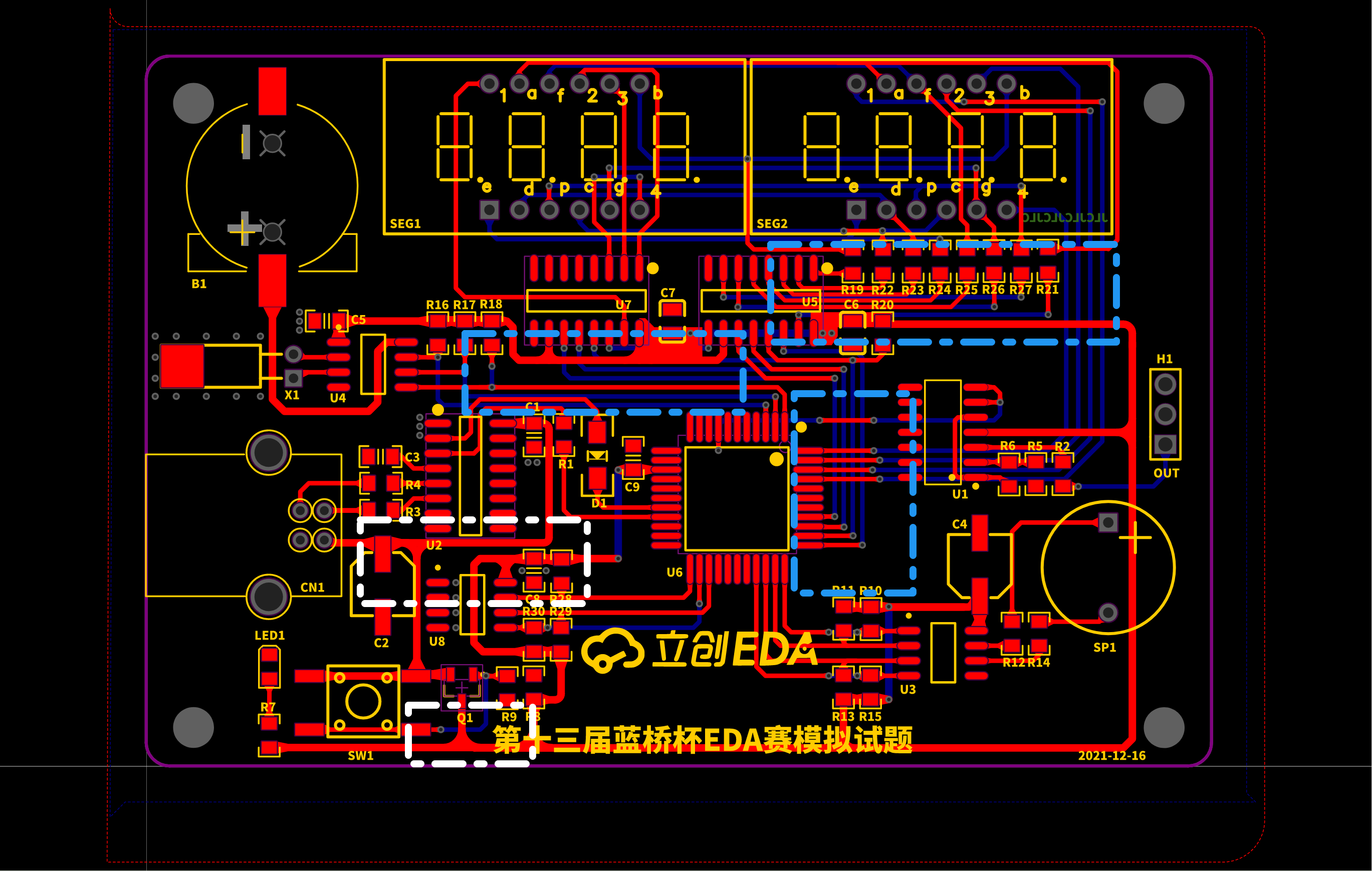

项目六

来源:【蓝桥杯练习题二】第十三届蓝桥杯EDA赛模拟题 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/di-shi-san-jie-lan-qiao-beieda-sai-mu-ni-ti

白框中,T型连接处理值得学习。后续不再赘述。

左侧蓝框中,第一:有非必要的底层连线,可能是修改连线后忘记更改。第二:过孔离焊盘太近,更改下最好。

右侧上方蓝框:连线平行交错情况,后续不再赘述。

下侧蓝框:过孔交错形式为上述提出的连接方式,值得参考。

项目较为简单,无较大的布局布线困难。

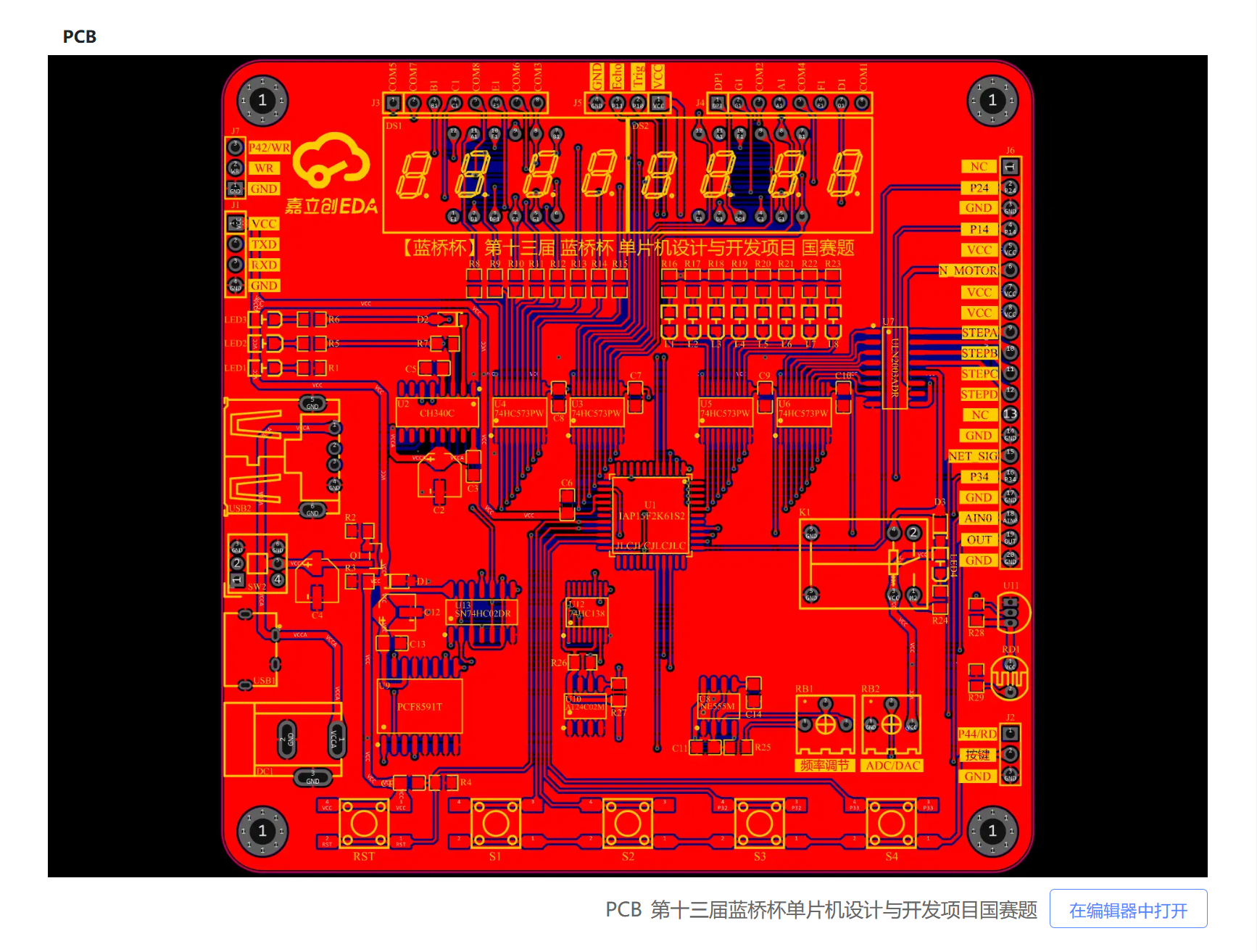

项目七

来源:【蓝桥杯】第十三届 蓝桥杯 单片机设计与开发项目 国赛题 - 嘉立创EDA开源硬件平台

https://oshwhub.com/course-examples/lan-qiao-bei-iap15f2k61s2-dan-pian-ji-kai-fa-ban第十三届蓝桥杯单片机设计与开发项目国赛题,基于组委会提供的四梯/国信长天单片机竞赛实训平台,按照赛题的要求进行修改配置,绘制出符合基本要求的练习训练板。

整体项目值得参考!!

建议多参考此项目中的资料以及PCB绘制!

[28/01/2024]:更新项目二

[10/04/2024]:更新项目三~六

[更完]

PCB设计是一个比较吃经验工作,布局、布线、阻抗匹配、信号完整性等等都比较吃经验。

建议下一些功夫,多绘制一些板子。多看看大厂的设计规范,多看看开源项目学习。

最后,推荐截图工具PixPin,好使!!!