热门标签

热门文章

- 1PCA降维算法(内含PCA可视化迷你案例+PCA人脸识别降维案例+PCA逆转降噪案例)_pca降维实例

- 2基于51单片机智能晾衣架控制系统设计( proteus仿真+程序+设计报告+原理图+讲解视频)

- 3Python-Flask框架之——图书管理系统 , 附详解源码和效果图 !

- 4机器学习/深度学习中的常用损失函数公式、原理与代码实践(持续更新ing...)_sparsemax函数

- 5vue3.0使用axios 解决跨域问题_vue3 axios跨域

- 6基于Vue框架的思源新闻发布平台设计与实现(论文+源码)_kaic_基于vue框架的实时新闻推送平台的设计与实现

- 7C语言实现输入 n 个字符串,将它们按字母由小到大的顺序排列并输出_字符串排序:输入n个字符串,按从小到大的顺序输出

- 8Java-时间复杂度和空间复杂度的概念和计算_java复杂度怎么算

- 9大学荒废4年,毕业后自学3个月软件测试,找到了15K的工作_大学混了四年能找到软件测试工作吗

- 10The TCP/IP connection to the host localhost, port 1433 has failed._verify the connection properties. make sure that a

当前位置: article > 正文

Xilinx FPGA中的BUFFER

作者:Cpp五条 | 2024-06-04 21:06:21

赞

踩

Xilinx FPGA中的BUFFER

FPGA大型设计中推荐使用同步时序电路,同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动有更高的要求。为满足时序的要求,一般采用全局时钟资源驱动设计的主时钟,FPGA的主时钟一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构。

缓冲和驱动

缓冲

输入输出缓冲,主要用于片外输入时钟或者片外差分输入的信号。

差分信号和差分时钟进入片内后如果不经过IBUFGDS、IBUFDS缓冲就无法直接处理

驱动

当信号扇出过大时可以通过加BUFG增加信号稳定性

过一次BUFG有10ns左右的延时,但是通过BUFG后输出到片上所有单元的延时都可以忽略不记

Buffer的类别和作用

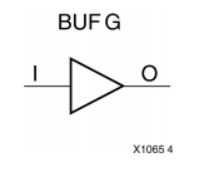

BUFG

BUFG是一个高扇出缓冲器,将信号连接到全局布线资源上,使得信号的延时和抖动最小

通常用于时钟网络以及其他高扇出网络,比如复位和使能信号

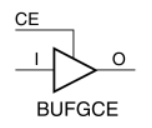

BUFGCE

BUFGCE具有单门控输入的全局时钟缓冲器,CE高电平有效

当CE为低电平时 O 端口输出0

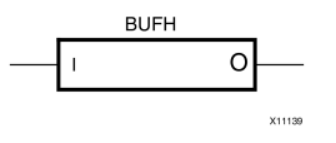

BUFH

BUFH原语允许直接访问BUFG的时钟区域入口,允许访问全局时钟网络中未使用的部分,作为高速低偏移的本地路由资源(单时钟区域)

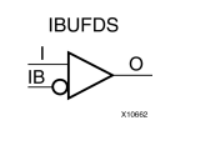

IBUFDS

支持低压差分信号输入的缓冲器,有两个输入的端口,一个为主端口一个为从端口,输入的信号相位相反

IBUFDS_GTE2

7系列器件中的Gbit 收发器输入缓冲,REFCLK应连接到串行收发器的专用参考时钟输入引脚

OBUFDS

差分信号输出缓冲器

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/673503

推荐阅读

相关标签