热门标签

热门文章

- 1oracle做拉链,Datastage实现拉链算法

- 2ShardingSphere读写分离

- 3地理信息系统教程(汤国安)——重点总结_双重独立编码结构

- 4NLP发展简史_nlp的发展阶段

- 5通用与垂直,谁将领跑未来?

- 6 推荐一款高效智能的校园考勤系统:Sistem Absensi Sekolah Berbasis QR Code

- 7python3.7+dlib+face_recognition+tensorflow+keras+scipy+numpy版本(已实现)_scipy对应cpu版本

- 8ARM 上的C语言开发_arm的c语言

- 9【软件工程】——开发模型_软件三大开发方法表格对比

- 10学习笔记Label自右向左滚动和父容器内左右移动方法(含代码)_lvgl文本从右到左滚动

当前位置: article > 正文

16 RTL仿真工具介绍—Modelsim脚本操作(Modelsim仿真 覆盖率测试)_modelsim 辅助设计

作者:Cpp五条 | 2024-06-12 18:03:27

赞

踩

modelsim 辅助设计

深入还是得靠自己学——尤其是脚本代码的编写

目录

windows的dump,看波形容易死机,代码无法运行,或者大的波形出错!

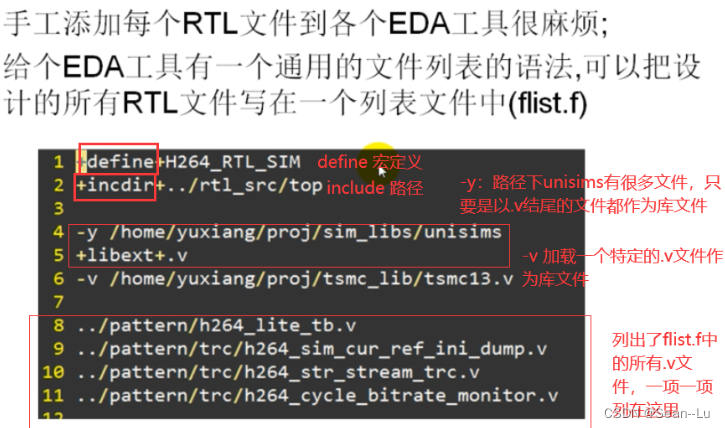

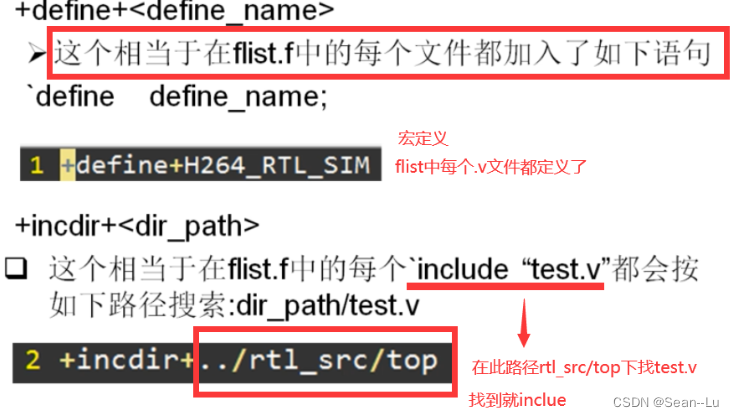

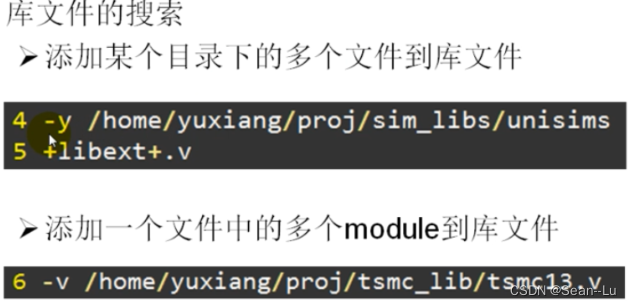

1.Flist常用写法

都可以写多行,如+incdir + 多个路径找,找不到compile会报错

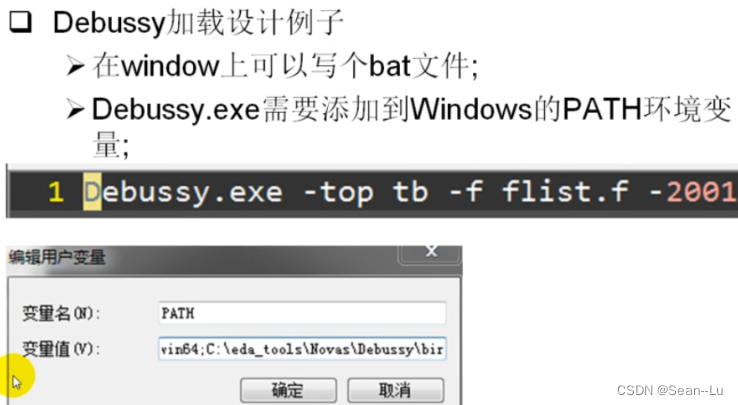

2.Debussy——检查语法错误+debug代码

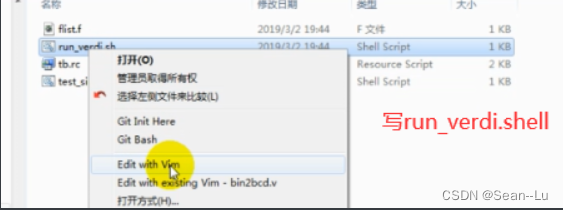

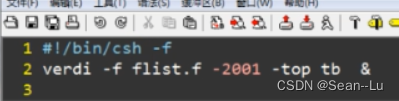

2.Linux版的Debussy——verdi

&——后台执行符号,第一行的:#!——表明是一个cshell的脚本

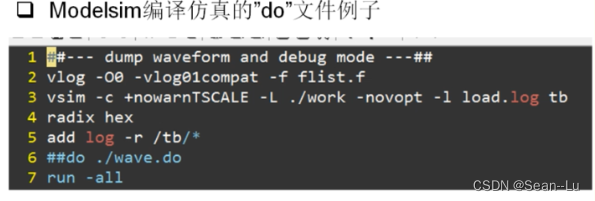

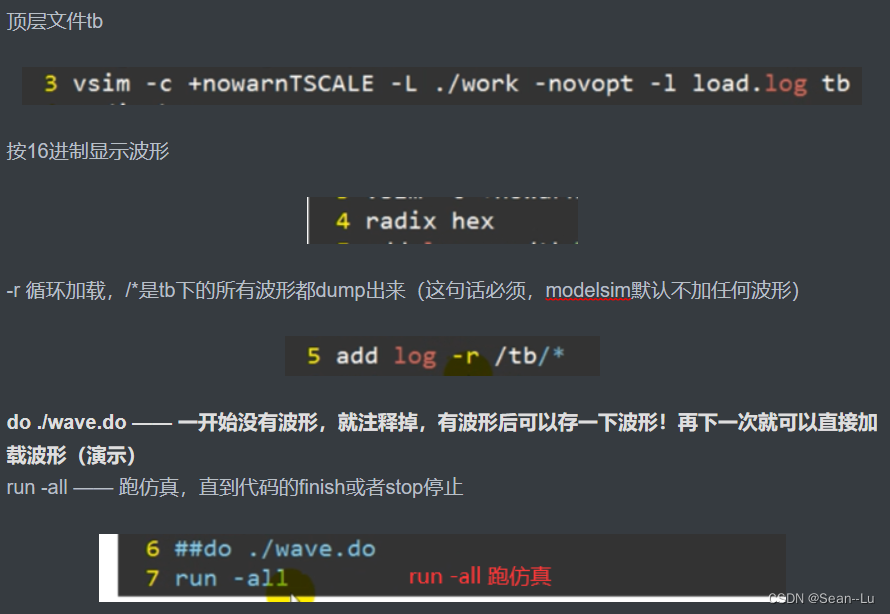

3.Modelsim——do file脚本

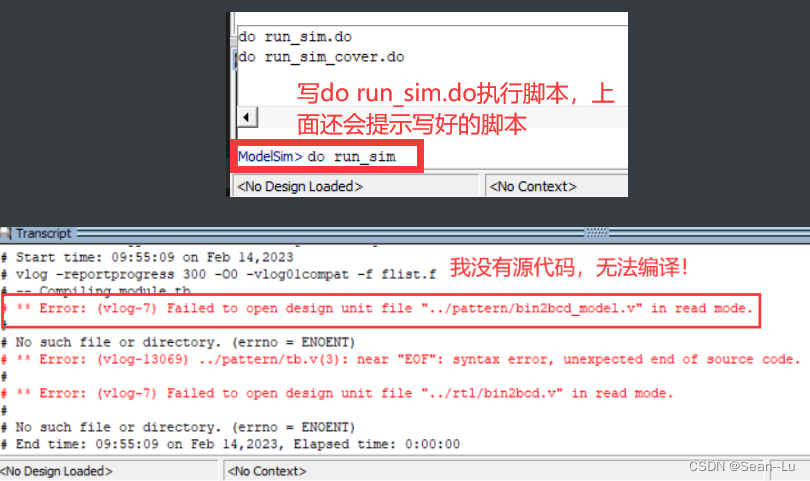

vlog——编译verilog代码。

-o0—— -optimization 0就是不optimization(仿真速度慢一点),optimization有时会把内部信号优化掉,导致在波形里面看不到了。

-vlog01compat——兼容Verilog2001语法 -f ——文件:flist.f

vsim——编译如果没有出错,就告诉modelsim进行仿真 tcl脚本vsim命令的参数列表(纯英文,无注释)

http://t.csdn.cn/evtgZ

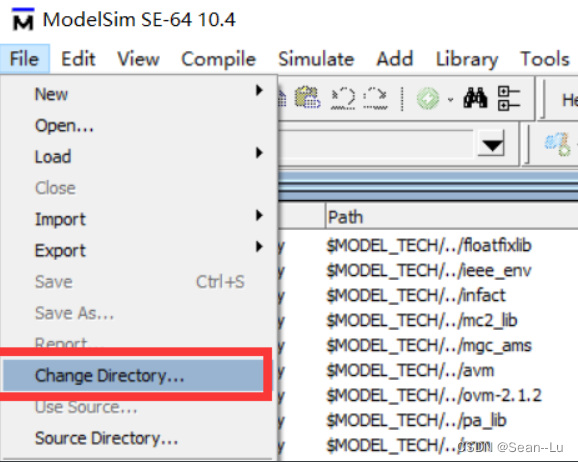

4.按脚本方式操作Modelsim

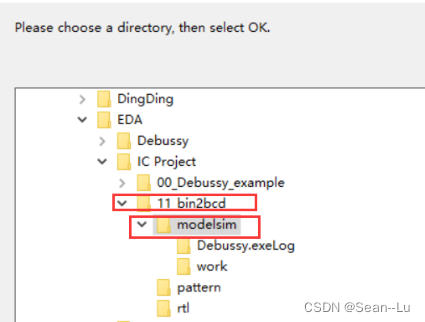

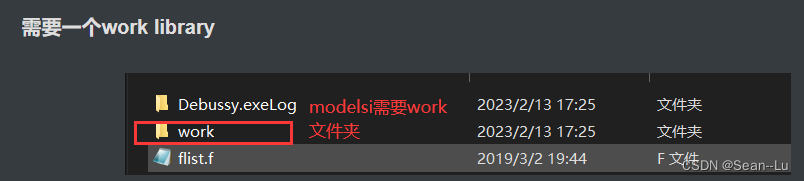

1.首先更改工作目录,到Modelsim文件夹下

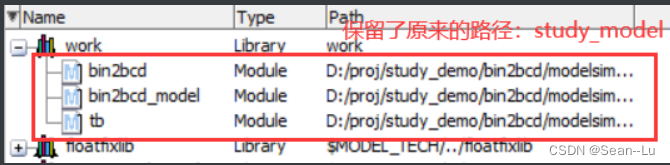

2.写脚本代码

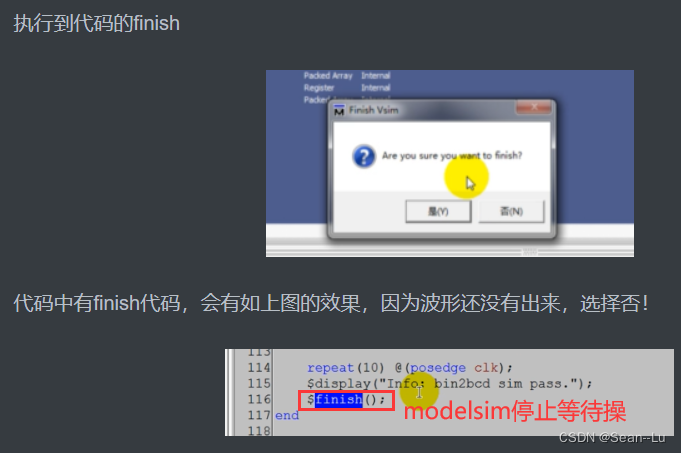

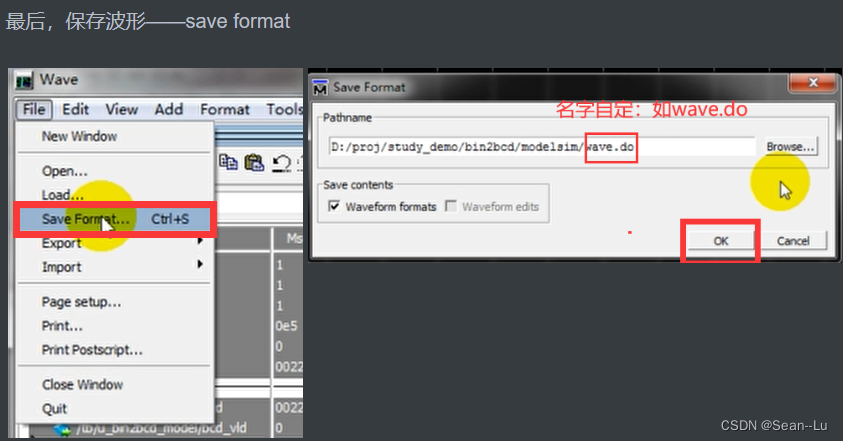

这段代码就是ppt中讲解的代码:do ./wave.do —— 一开始没有波形,就注释掉,有波形后可以存一下波形!再下一次就可以直接加载波形(演示)

3.执行脚本、仿真

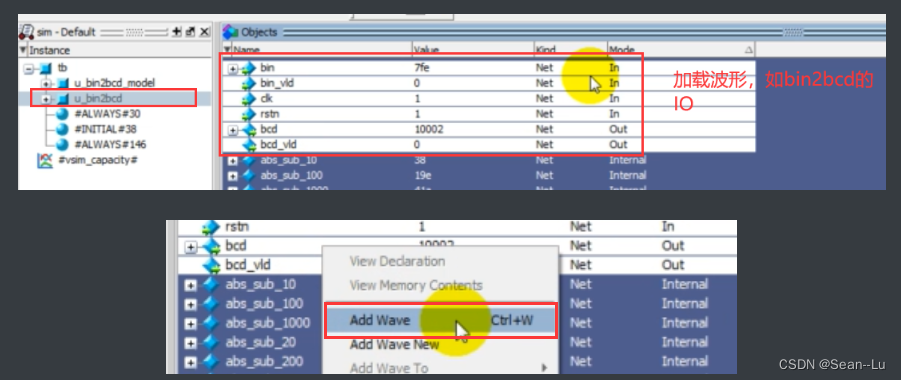

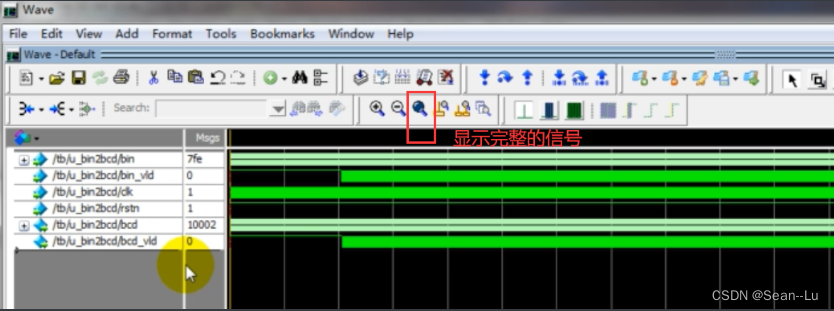

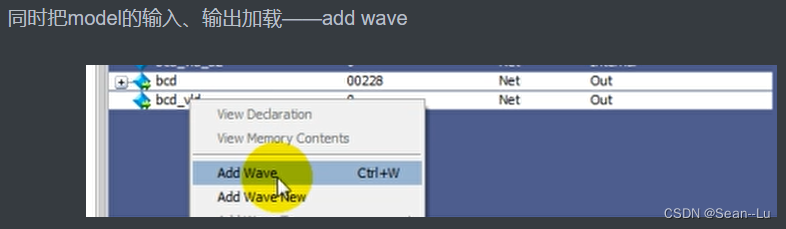

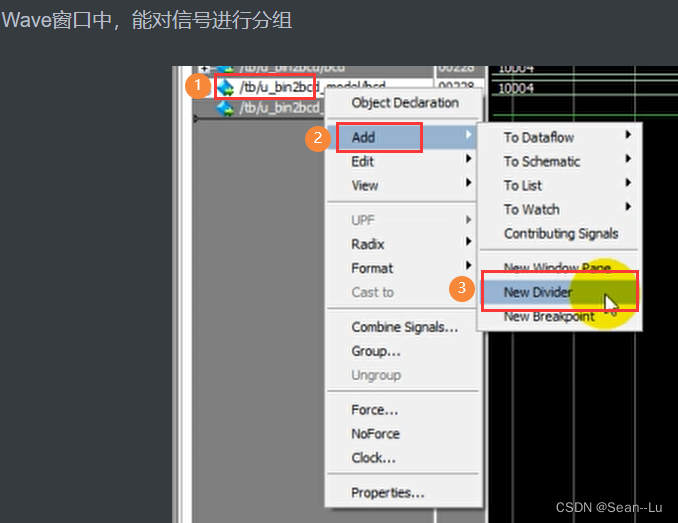

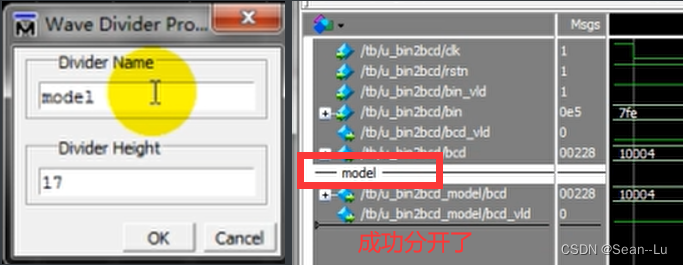

4.加载波形、界面操作、保存波形

选中波形,右键、add wave

加载后,wave窗口就有了信号!

5.修改脚本、退出仿真、加载保存过的波形

因为wave.do已经存在了,再次执行脚本就可以直接调用上面我们修改好格式、保存好的wave.do!!!!!这样省去了多次修改仿真波形的繁琐步骤!!!

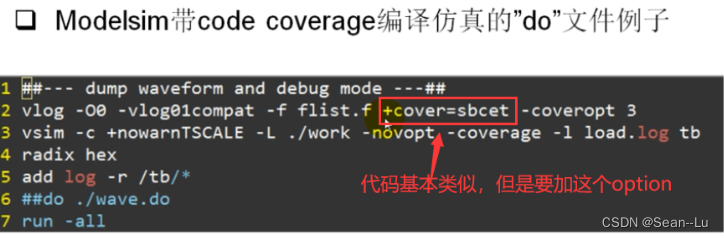

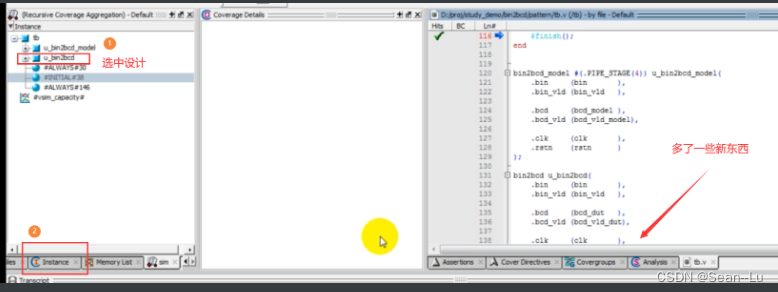

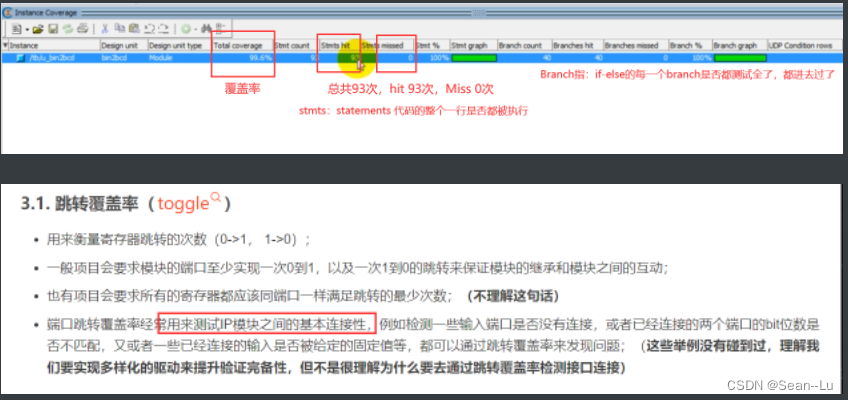

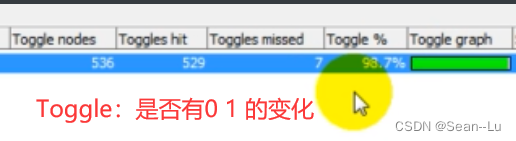

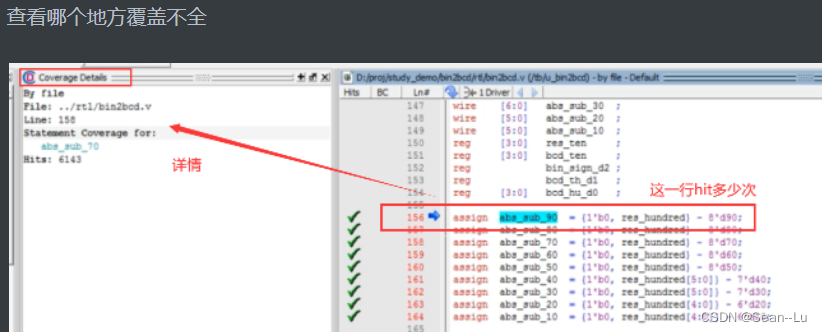

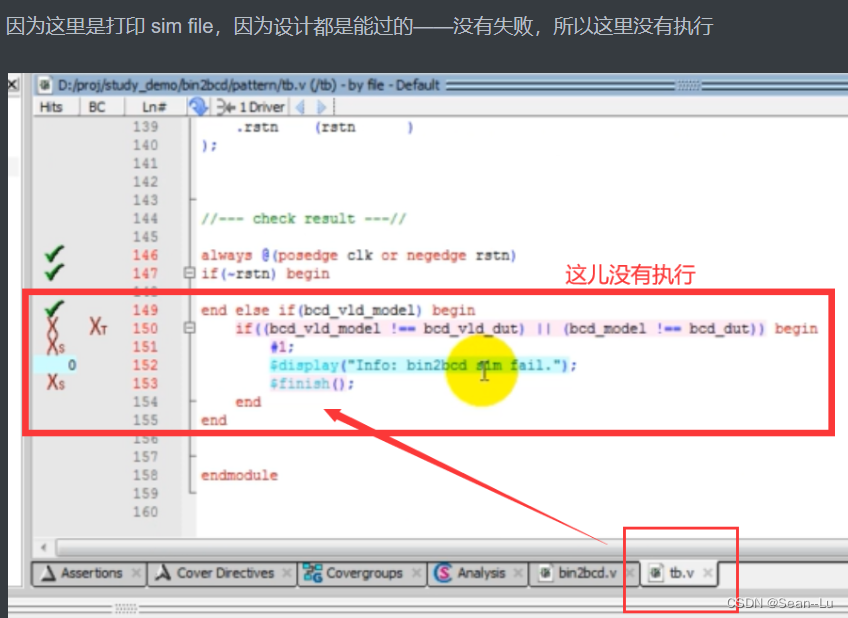

6.进一步,跑代码覆盖率

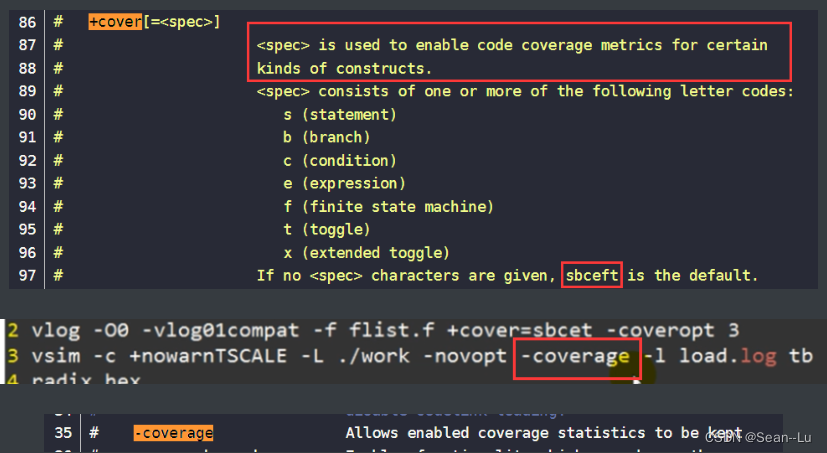

1.代码说明

告诉modelsim要做coverage测试,sbcet是coverrage的类型 http://t.csdn.cn/O1Qgd http://t.csdn.cn/HTAnF

2.执行脚本

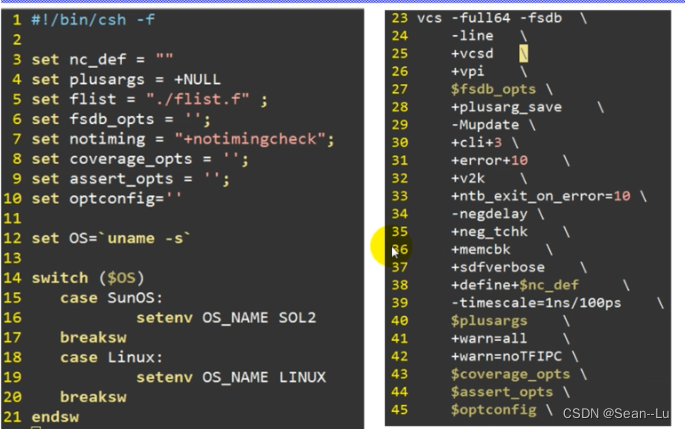

5.VCS仿真(linux下)

编译 full64——64位机器

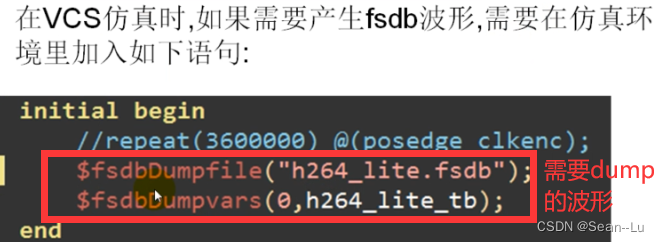

windows的dump,看波形容易死机,代码无法运行,或者大的波形出错!

dump波形的名字,dump波形的顶层文件:即tb下所有波形都做dump

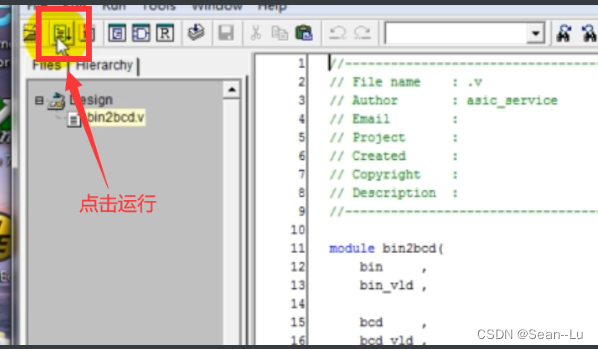

6.Windows下的nLint软件

1.加载文件

2.运行

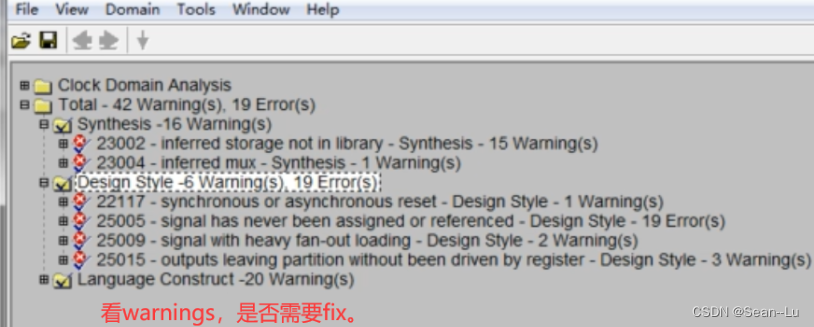

stimulation 没有错误就可以(warning),设计风格的警告和错误没有大问题↓

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/709032

推荐阅读

相关标签