热门标签

热门文章

- 1C#排序算法一 希尔排序_c# 希尔排序

- 2所有集群启动的命令_hadoop集群启动命令

- 3JSON parse error: Cannot deserialize value of type `java.util.Date` from String

- 4微信小程序实现购物车功能,包含完整小程序代码和运行效果截图_微信小程序购物车代码

- 5数据量大的table优化插件(上万+条数据)_table 插件

- 6征集即将截止,《中国AIGC产业全景报告暨AIGC 50》邀你共同参与!

- 7机器学习笔记 - 什么是t-SNE?

- 8机器学习中的XGBoost模型及其优缺点(包含Python代码样例)_xgboost 模型优势

- 9速盾:什么是cdn架构

- 10Deep Learning for 3D Point Clouds: A Survey - 3D点云的深度学习:一项调查 (IEEE TPAMI 2020)_3d object detection in point clouds: a review

当前位置: article > 正文

FPGA学习记录(一)vivado简单仿真全加器_vivado全加器仿真代码

作者:Gausst松鼠会 | 2024-05-07 08:16:05

赞

踩

vivado全加器仿真代码

**

FPGA学习记录(一)vivado简单仿真全加器

**

1.先写一个全加器

`timescale 1ns / 1ps // 时间单位 / 时间精度 module full_adder( input IN1, input IN2, input IN3, output cout, output sum ); assign{cout,sum}=IN1+IN2+IN3; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

**

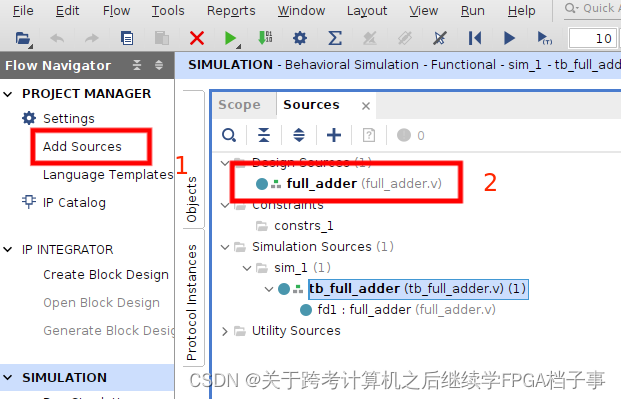

2.在Sources下的Simulation Sources新建一个 .v 文件,文件名为 tb_full_adder, tb表示仿真文件

**

**

3.仿真文件内容.

**

`timescale 1ns / 1ps module tb_full_adder(); //模拟仿真,所以没有输入输出端口 reg in1; reg in2; reg in3; wire cout; wire sum; //例化,有点像C语言 实例化一个类 full_adder fd1( .IN1(in1), .IN2(in2), .IN3(in3), .cout(cout), .sum(sum) ); initial //激励关键字,只执行一次(always则是一直激励),通常用来赋初值 begin //只有在begin-end之间的代码是串行执行 #100 in1<=0;in2<=0;in3<=0; //#100指的是100秒后 #100 in1<=0;in2<=0;in3<=1; //使用非阻塞赋值 #100 in1<=0;in2<=1;in3<=0; //阻塞赋值和非阻塞赋值不要在一个module里出现 #100 in1<=0;in2<=1;in3<=1; #100 in1<=1;in2<=0;in3<=0; #100 in1<=1;in2<=0;in3<=1; #100 in1<=1;in2<=1;in3<=0; #100 in1<=1;in2<=1;in3<=1; #100 $finish; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

**

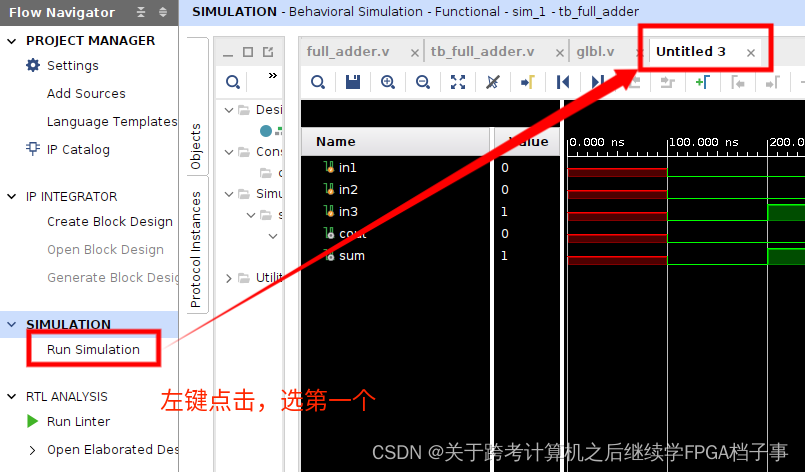

4.开始仿真

**

左键单击Run Simulation->Run Behavioral Simulation, 等待片刻,在写代码的文件旁边会新建仿真结果(第一次运行时差点没找到)

**

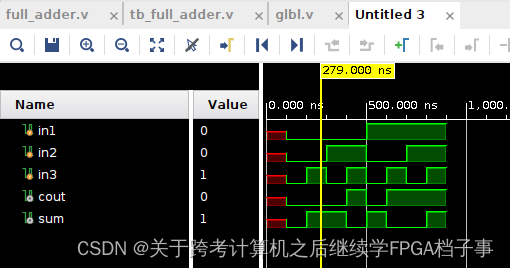

5.仿真结果

**

符合全加器逻辑

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/548212

推荐阅读

相关标签