热门标签

热门文章

- 1AI模型训练推理一定要知道的事情_ai模型 内存

- 2Vivado MIG ip核使用教程(三)_mig状态机

- 3java面试题及答案(基础题122道,代码题19道_java基础题

- 4GAN(生成对抗神经网络)能gan(干)什么?|万字总结20种应用_gan应用

- 5Spring-Boot (二) application.properties配置文件内容_springboot中application配置内容

- 6大数据学习进阶_大数据进阶学习

- 7【目标检测】yolo系列-yolo_v5学习笔记_yolov5m

- 8Python排序,你用对了吗?一文教你sorted和sort的正确姿势!

- 9新手教学系列——MongoDB聚合查询的进阶用法

- 10创建LabwindowsCVI工程_cvi serial number

当前位置: article > 正文

【IC设计】边沿检测电路(上升沿、下降沿、双沿,附带源代码和仿真波形)_下降沿检测电路

作者:Guff_9hys | 2024-07-10 09:20:41

赞

踩

下降沿检测电路

边沿检测电路的概念

边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现了信号的上升沿或下降沿,则给出一个信号指示出来。

边沿检测电路根据检测边沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

上升沿检测电路

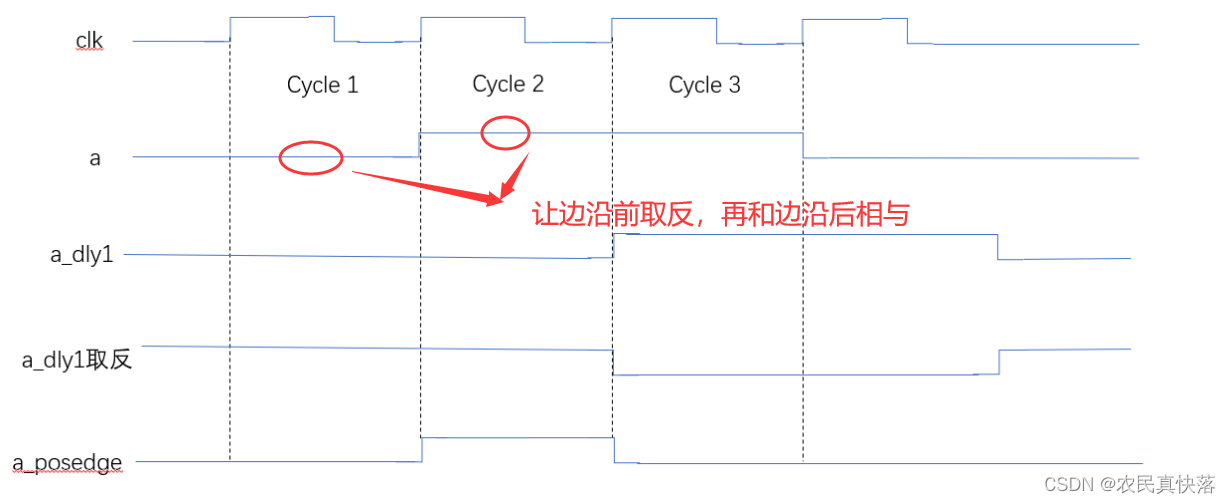

如图所示,我们的目标是当检测到a从0变成1时,令a_posedge为高电平,其余情况a_posedge均为低电平。

要检测a从0变成1,也就是说a的上升沿前是低电平,上升沿后是高电平,那么只需要令边沿前取反,再和边沿后相与,如果结果为1,说明必然是边沿前为0,边沿后为1,确认是上升沿。

实际操作中是让a打一拍并取反,再和a相与,得到a_posedge。

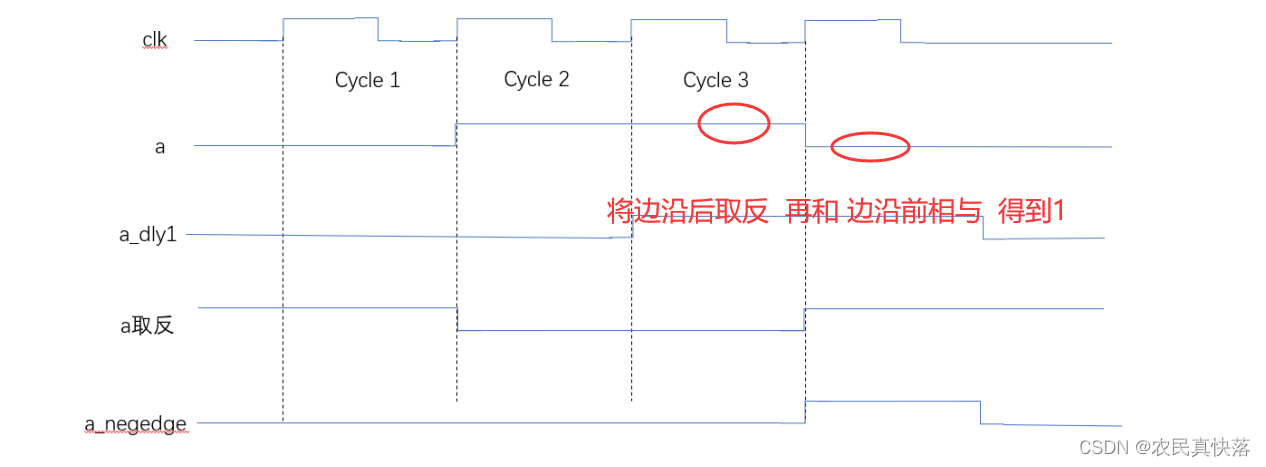

下降沿检测电路

下降沿同理,边沿后取反再和边沿前相与,得到1,说明是下降沿。 边沿前电平可以通过a打一拍得到。

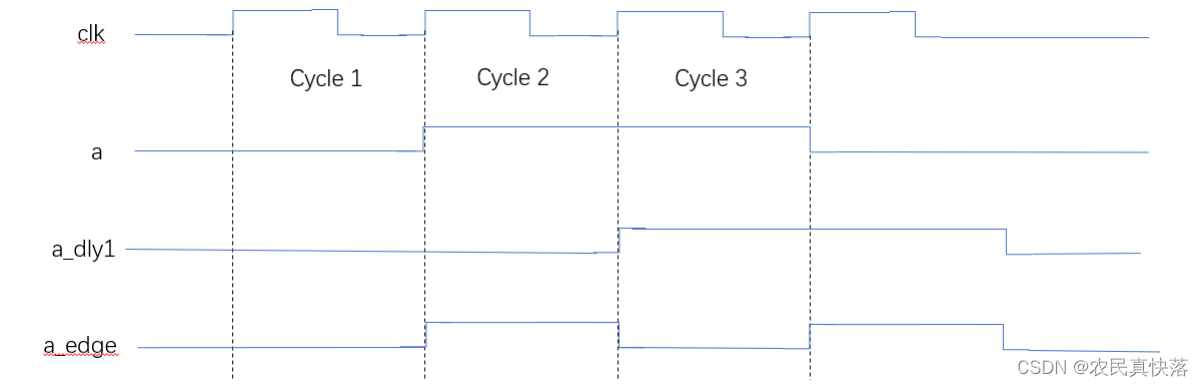

双边沿检测电路

- 方法一:

前面会了上升沿和下降沿检测,双边沿检测也就是上升沿和下降沿都拉高,只需要将前面两者的结果进行或运算即可。 - 方法二:

更为简便的办法是,上升沿和下降沿都是0和1之间的跳变,使用异或运算符,可以直接得到结果。

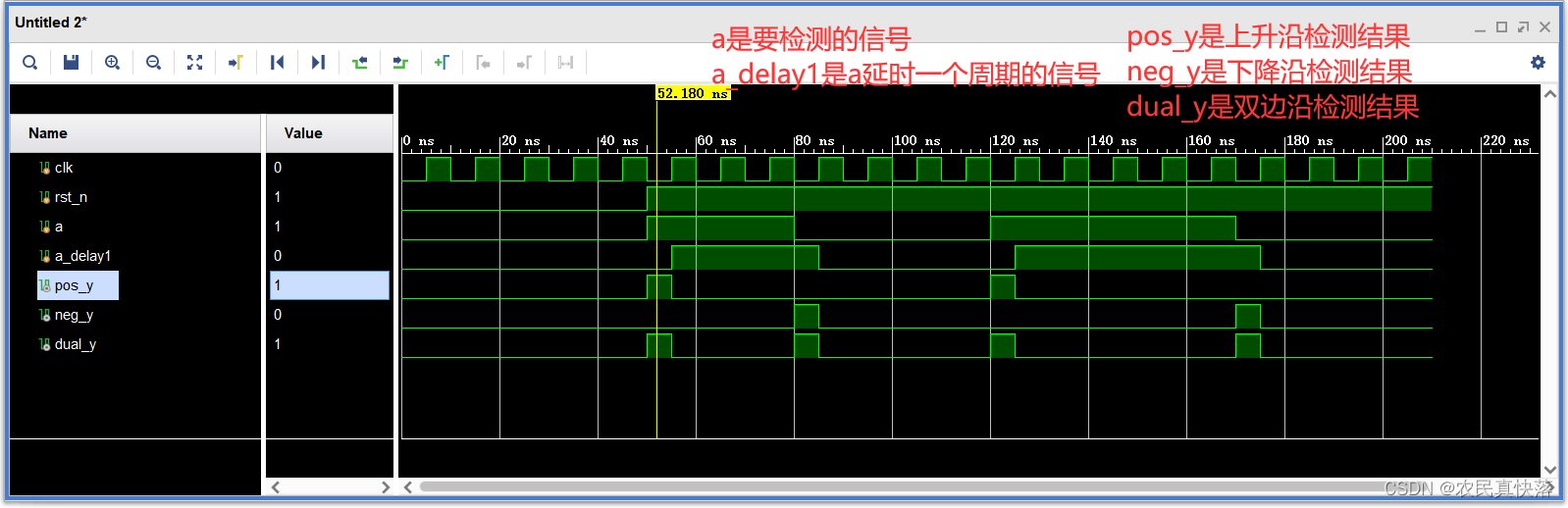

代码和仿真

RTL代码

`timescale 1ns / 1ps module edge_detection ( clk, rst_n, a, pos_y, neg_y, dual_y ); input clk; input rst_n; input a; //需要检测边沿的信号a output pos_y; //上升沿检测 output neg_y; //下降沿检测 output dual_y; //双边沿检测 reg a_delay1; //将信号a打一拍得到a_delay1 always@(posedge clk or negedge rst_n) begin if( ~rst_n ) begin a_delay1 <= 0; end else begin a_delay1 <= a; end end // ~优先级高于& assign pos_y = a & ~a_delay1; assign neg_y = ~a & a_delay1; assign dual_y = a ^ a_delay1; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

Testbench代码

`timescale 1ns / 1ps //tb的基本思路无非就是:制造时钟、复位、例化、构造数据 module tb_edge_detection(); reg clk,rst_n,a; wire pos_y,neg_y,dual_y; initial begin a = 0; clk = 0; rst_n = 0; #50 rst_n = 1; a = 1; #30; a = 0; #40; a = 1; #50; a = 0; #40; $stop; end edge_detection edge_detection_u0 ( .clk(clk), .rst_n(rst_n), .a(a), .pos_y(pos_y), .neg_y(neg_y), .dual_y(dual_y) ); always #5 clk = ~clk; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

仿真波形

参考资料

本文内容由网友自发贡献,转载请注明出处:https://www.wpsshop.cn/w/Guff_9hys/article/detail/805555

推荐阅读

相关标签