- 1分组卷积/转置卷积/空洞卷积/反卷积/可变形卷积/深度可分离卷积/DW卷积/Ghost卷积/

- 22022年软件评测师_2022软件评测师 csdn

- 3全面的软件测试

- 4在 gitee 码云部署预览静态站点项目(国内站点)_gitee部署静态网站

- 513款趣味性不错(炫酷)的前端动画特效及源码(预览获取)分享(附源码)_炫酷的网页特效代码

- 6Android 同时打包debug版 release版_android buildconfig怎么打包debug

- 7香橙派AIpro初体验:搭建无线随身NAS

- 8Flutter 通过 VS code 连接 Android 模拟器(Windows)_vscode 安卓模拟器

- 9【协议】WebSocket协议总结_socket通信是全双工还是半双工

- 10搭建Elasticsearch、Kibana和Logstash环境:构建强大的数据分析平台

8位可控加减法电路设计_FPGA配置外围电路设计冲突与解决方法

赞

踩

如前所述,FPGA是由存放在片内的RAM来设置其工作状态的,因此工作时需要对片内RAM进行编程。用户可根据不同的配置模式,采用不同的编程方式。Xilinx FPGA的常用配置模式有主串模式、从串模式、Select MAP模式等。

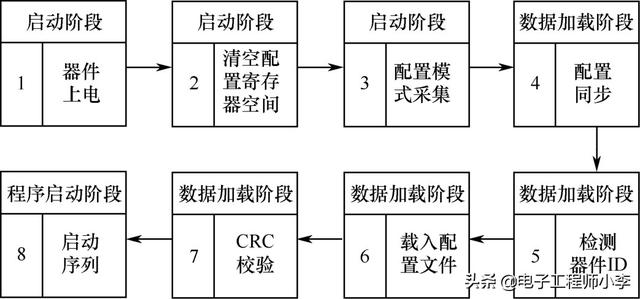

FPGA和CPLD不同,上电后不能直接工作,而是需要一个配置过程。Xilinx FPGA需要经过8个步骤才能正常地运行用户逻辑,整个流程如图1-8所示。

图1-8 FPGA上电配置步骤

1.FPGA上电启动

FPGA工作的第一步就是给器件加电。Xilinx要求VCCINT(核心电压)先动,然后再是VCCO(I/O电压),最坏情况是它们之间不能相差1 s以上。在并行配置模式下,要求VCCO_2参考电压必须和FLASH参考电压相同。

在系统正常上电或者PROG-B是一个低脉冲时,FPGA开始配置寄存器空间。这段时间除定义好的配置引脚外,其他I/O引脚均被设置为高阻态(High-Z)。经多次测试,这个阶段需要30 ms左右的时间。

FPGA启动阶段最后一步就是配置启动模式。在PROG-B变高时,FPGA开始采集配置方式引脚(M3、M2、M1),并同时驱动CCLK输出。在这个阶段,有两种方法可以延迟FPGA的配置时序,一种是拉低INIT-B引脚,这是由于FPGA检测到自身还没有初始化完毕,不会进行接下来的操作步骤,这种状态一直保持到INIT-B引脚变高。另一种就是拉低PROG-B引脚,使FPGA处于等待配置状态。

2.FPGA数据加载

FPGA正常数据加载前,需要做一个器件与FLASH之间的同步检查。其方法是传输一个特殊的32位数值(0xAA995566)到FPGA中,提示FPGA下面开始传输的是配置数据。这个步骤对用户来说是透明的,因为Xilinx ISE Bitstream Generator生成的.bit文件中已经自动加入了这个校验码。

在完成配置前的通信同步后,FPGA与FLASH之间还无法识别对方是什么器件,于是Xilinx就给每一个型号的FPGA设计了一个唯一的器件ID号,这个ID号可以在Xilinx配置手册中查到。如XC4VSX35,其ID号为0x02088093。FPGA需要从FLASH中读出这个器件号和自身比对,如果相同就继续下面的步骤,如果不同则配置失败,并打印出配置故障信息。

所有准备工作正常完成后,FPGA开始载入配置文件。这一步对大多数用户也是透明的,由器件自行完成。这也是配置过程中最耗时的步骤,时间从100 ms到几秒不等。在这个过程中,FPGA的所有可配置I/O根据HSWAPEN引脚的设置变为弱上拉(HSWAPE=1)或者高阻态(HSWAPE=0)。这个阶段的I/O引脚还没有变为用户需要的状态,也最有可能影响到其他外围电路的上电时序和运行。设计硬件电路时要特别注意并采取必要措施,如加入上下拉电阻或改变器件加电顺序来尽量避免或减少FPGA配置时对电路其他器件的影响。

配置文件载入完成后,为了验证数据的正确性,FPGA还自动设置了CRC校验(这个在ISE配置选项中也可以去掉,但是为了保证载入数据的正确性,这个是必须选择的)。如果CRC校验不正确,FPGA会自动把INIT-B拉低,放弃这次配置。用户必须把PROG-B引脚拉低,才能进行重新配置。

3.启动序列

CRC校验正确后,FPGA不会马上执行用户的逻辑,它还要进行一些自身内部电路的配置,如DCM锁定(DCMs to Lock)、全局写信号使能(Global Write Enable)等,这些信号的启动顺序也是在ISE配置选项中设置的。必须启动的序列为:释放DONE引脚;释放GTS信号,激活IO引脚;设置全局读/写使能、使能内部RAM和FIFOAssert,结束上电配置。

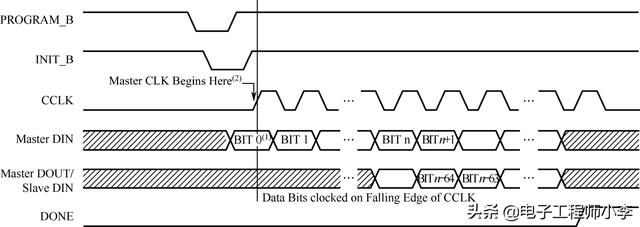

从上面论述可知,整个FPGA的上电配置正常时序如图1-9所示。

4.FPGA配置外围电路设计冲突与解决方法

FPGA上电配置整个过程大约需要200 ms~2 s,这段时间绝大多数其他外围电路器件都已经上电并正常工作了,而FPGA的通用I/O引脚还处于弱上拉(HSWAPEN=0)或者不定态(HSWAPEN=1),设计时就需要考虑这些器件上电初始化和FPGA通用I/O引脚有无时序冲突。例如,上电时,外围器件要求I/O引脚都为低电平,而FPGA默认是弱上拉,初始化电平产生了冲突;外围器件要求在上电复位后马上采集配置引脚进行初始化,而FPGA还处在配置状态,无法正确上拉或下拉I/O引脚,器件初始化错误;外围器件要求上电初始化前需要时钟锁相,FPGA配置时产生不了时钟,导致器件初始化失败等。解决这些冲突大致有3种方法,但前提都是要正确配置HSWAPEN引脚,这是因为在FPGA执行“器件上电”步骤后(5~30 ms内),它输出的I/O引脚状态是可以通过HSWAPEN设定的。

图1-9 FPGA上电配置时序

方法1:在FPGA的I/O引脚外加上下拉电阻,阻值在1~10KΩ之间,根据实际需要确定。FPGA在上电后10 ms内能通过上下拉电阻把I/O引脚拉到用户需要的电平上,这样能满足上电较慢但是又要求固定电平的外围电路的要求,如功放发射开关和保护开关等。

方法2:FPGA可以在配置完成后产生一个全局复位信号,使外围电路硬件复位,再进行一次初始化操作。这样能解决PowrerPC、ARM这种上电初始化很快(在100ms内就能完成)、但由于FPGA没有配置完成而导致PowrerPC初始化错误的问题。而且这种方式不用外接多余的上下拉电阻,减少了电路设计复杂性。

方法3:FPGA可以在配置完成后产生一个Power Good信号,系统根据此标志再给外围其他有时序要求的器件上电,这样能满足DSP或者高速AD这种需要时钟锁定后再进行初始化的器件的要求。

这3种方法也可根据具体情况混合使用,能达到更好的效果。

5.结论

通过上述分析可知,FPGA上电是一个短暂而复杂的过程,设计时需要充分考虑FPGA上电配置时序和该过程中I/O引脚的各种状态对外围电路的影响。根据系统设计的具体情况,通过选用最合理的配置方式以及外围电路连接,达到了既不影响其他器件性能和整个系统功能,又简化和改善了整个电路设计的效果。