热门标签

热门文章

- 1探索数据转化为文本的神奇:data2text 开源项目

- 2大数据实验 实验五:MapReduce 初级编程实践_对于两个输入文件,即文件a和文件b,请编写mapreduce程序,对两个文件进行合并,并剔

- 3Doris 如何基于自增列满足高效字典编码等典型场景需求_jpa doris 自增表

- 4【通俗易懂】手把手带你实现DeepFM!

- 5轮播图切换(html+css+JavaScript)_css轮播图并点击切换

- 6淘宝客公众号京东淘宝拼多多三合一源码三级代理系统网站源码_拼多多耐克三级代理

- 7计算机网络——子网划分 笔记

- 8Android异常篇 Manifest merger failed : Attribute application@label value=() from AndroidM_manifest merger failed : attribute application@sup

- 9Python文件操作 - 写入文件:Python中的文件写入操作用于将数据写入到文件中_python将内容写入文件

- 10Python实现——带你纯纯手工做双线性曲面插值_曲面插值python

当前位置: article > 正文

FPGA Verilog 单芯片控制双AD7606芯片_ad7606 verilog

作者:寸_铁 | 2024-07-15 12:50:28

赞

踩

ad7606 verilog

前言

控制双ad7606的目的是因为所需要的通道数12,单个ad7606只有8个通道,因此需要控制2个ad7606满足12个通道的采样需求。

一、模式选择

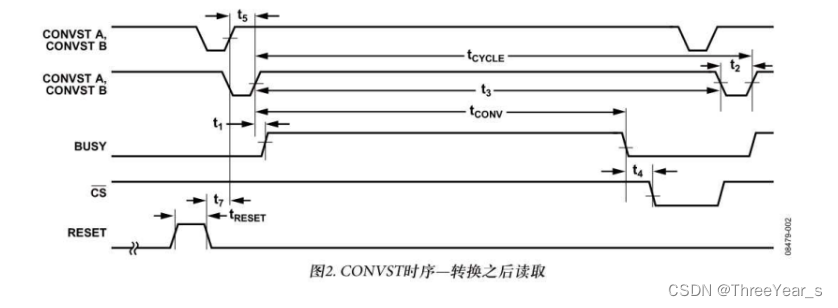

1 转换之后进行读取:由这个图片可以确定ca cb 以及cs 信号的工作状态

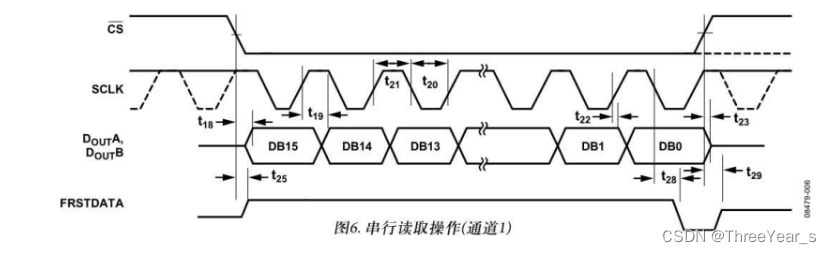

2 串行读取模式:由这个图片可以确定sclk 与 数据读取的工作状态

3 数据存储以及发送:使用一个16位的寄存器对16个通道的数据进行依次保存,保存完之后立即发送出去,具体就是保存完ad通道1的数据后,里面发送出去,发送需要的时间比较长,因此发送结束之前就能够进行下一通道的采集。因此我的sclk是受控的,不是完全连续的。

二、AD7606 FPGA实现

1.ad7606部分

代码如下:

module ad7606( input clk, input res, input dout_a, //ad7606通道a输入串行读取数据 input dout_b, //ad7606通道b输入串行读取数据 input ad_busy, //ad7606输入busy信号 input caiji_flag, //外界输入开始数据采集的标志 // output wire caiji_over, output reg ad_ch_over, //ad8个通道采集over标志 output reg [3:0] stata, output reg [4:0] cnt_bite, output reg [5:0] cnt, // output wire [15:0] crc_real, output wire data_tx, output wire start_ad_one, output wire start_ad_two, output wire crc_flag, output reg crc_realflag, output wire data_overflag, output wire data_code, output dis_clk , output dis_cs , output dis_miso , output dis_ca , output dis_busy , output reg [15:0]databuffa, // output reg [15:0]data_ch, output wire [15:0] datatx, // output reg [15:0]databuffb, output reg ad_cs, //读ad7606的使能信号 output reg ad_cs2, //读ad7606的使能信号 output reg ad_rd, //读ad7606的时钟信号 output reg ad_convstab //ad7606开始转换信号,低电平有效 ); /**----------------------ad工作ca cs rd信号 -------------------------------------**/ //输出信号 always@(posedge clk or negedge res) if(!res) ad_convstab <= 1'b1; else if(stata == AD_CONV) ad_convstab <= 1'b0; else ad_convstab <= 1'b1; always@(posedge clk or negedge res) if(!res) ad_cs <= 1'b1; else if(stata == WAIT_1 && ad_busy == 1'b0 && start_ad_one == 1'b1) ad_cs <= 1'b0; else if(stata == READ_STOP) ad_cs <= 1'b1; else ad_cs <= ad_cs; always@(posedge clk or negedge res) if(!res) ad_cs2 <= 1'b1; else if(stata == WAIT_1 && ad_busy == 1'b0 && start_ad_two == 1'b1) ad_cs2 <= 1'b0; else if(stata == READ_STOP) ad_cs2 <= 1'b1; else ad_cs2 <= ad_cs2; always@(posedge clk or negedge res) if(!res) ad_rd <= 1'b1; else if(stata == READ_CH1 || stata == READ_CH2 || stata == READ_CH3 || stata == READ_CH4 || stata == READ_CH5 || stata == READ_CH6 || stata == READ_CH7 || stata == READ_CH8) if(cnt == (FIV_CLK-1) && cnt_bite < 16) ad_rd <= 1'b0; else if(cnt == 2*FIV_CLK-1 && cnt_bite < 16) ad_rd <= 1'b1; else ad_rd <= ad_rd; else ad_rd <= 1'b1; /**-----------------------------------------------------------------------------**/ /**----------------------缓存串行数据 -------------------------------------------**/ //处理输入的串行数据 always@(posedge clk or negedge res) if(!res)begin databuffa <= 16'd0; end else if(stata == READ_CH1 || stata == READ_CH2 || stata == READ_CH3 || stata == READ_CH4 || stata == READ_CH5 || stata == READ_CH6 || stata == READ_CH7 || stata == READ_CH8)begin if(cnt == FIV_CLK && ad_rd == 1'b0 && ad_cs == 1'b0)begin databuffa <= {databuffa[14:0],dout_a}; end else if(cnt == FIV_CLK && ad_rd == 1'b0 && ad_cs2 == 1'b0)begin databuffa <= {databuffa[14:0],dout_b}; end else begin databuffa <= databuffa; end end else begin databuffa <= 16'd0; end //将采集到的数据存储到data_ch中 always@(posedge clk or negedge res) if(!res)begin data_ch <= 16'd0; end else if(stata == READ_CH1 && cnt_bite == (CNT_CLK) )begin data_ch <= databuffa ; end else if((stata == READ_CH2 || stata == READ_CH3 || stata == READ_CH4 || stata == READ_CH5 || stata == READ_CH6 || stata == READ_CH7 ||stata == READ_CH8 ) && cnt_bite == (CNT_CLK -1))begin data_ch <= databuffa ; end else begin data_ch <= data_ch ; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

2.数据发送

该部分就是一个简单的并行转串行模块

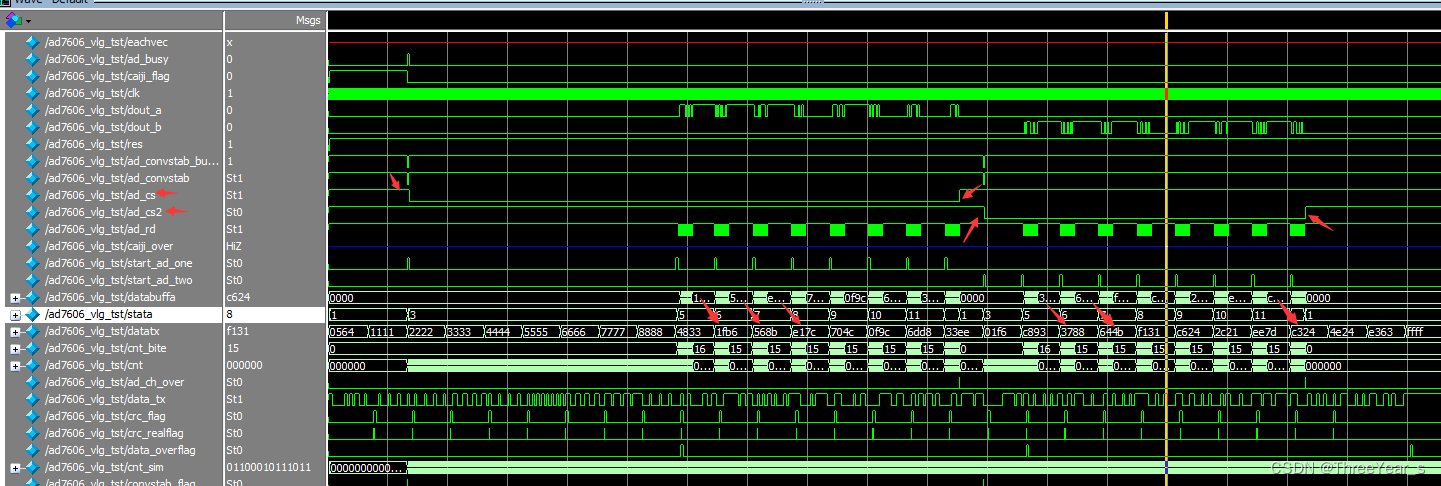

3.实际仿真图(上板验证后也正确)

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/寸_铁/article/detail/829434

推荐阅读

相关标签