- 1css实现两列布局,一列固定宽度,一列宽度自适应方法_css表格宽度怎么自动适应

- 2安装torch-geometric_torch-geometric 2.1.0.post1安装

- 33102. 最小化曼哈顿距离——leetcode

- 4【微信小程序】小程序群分享获取分享信息_小程序分享聊天群获取信息

- 5《基于 Kafka + Flink + ES 实现危急值处理措施推荐和范围校准》_基于 kafka + flink+es 实现危急值处理措施推荐和范围校准

- 6java前端开发jquery_web前端开发JQuery常用实例代码片段(50个)

- 7在vue中webSocket通信_vue websocket header

- 8为什么不建议在 MySQL 中使用 UTF-8?_mysql问什么不建议使用utf8

- 9深度学习:自然语言处理与Finetuning

- 10德州仪器2024届校招 FAE&;AE&;TSE_芯片tse fae ae

【FPGA】FPGA对AD7606进行串行数据采集_ad7606 fpga 串行

赞

踩

个人笔记。这段时间在用FPGA对AD7606进行数据采集,现在把检测过程和遇到的问题记录一下,方便以后避坑。文章最后有相关资料链接。

1、AD7606概述

AD7606是16位,8通道同步采集模数数据采集系统。各器件均内置模拟输入钳位保护、二阶抗混叠滤波器、跟踪保持放大器、16位电荷再分配逐次逼近型模数转换器、灵活的数字滤波器、2.5V基准电压源、基准电压缓冲以及高速串行和并行接口。AD7606采用5V单电源供电,可以处理正负10V和正负5V真双极性输入信号,同时所有通道均能以高达200kSPS的吞吐速率采样。输入钳位保护电路可以耐受最高达正负16.5V的电压。无论以何种采样频率工作, AD7606的模拟输入阻抗均为1MΩ。它采用单电源工作方式,具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源。AD7606抗混叠滤波器的3dB截止频率22kHz;当采样率为200kSPS时,它具有40dB抗混叠抑制特性。灵活的数字滤波器采用引脚驱动,可以改善信噪比(SNR),并降低3dB带宽

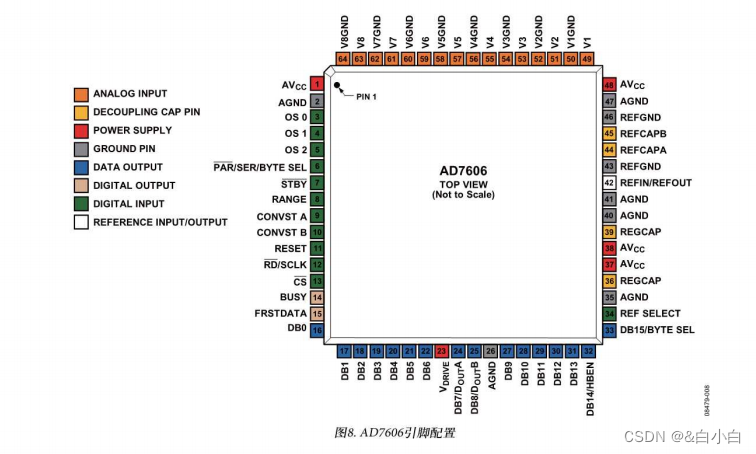

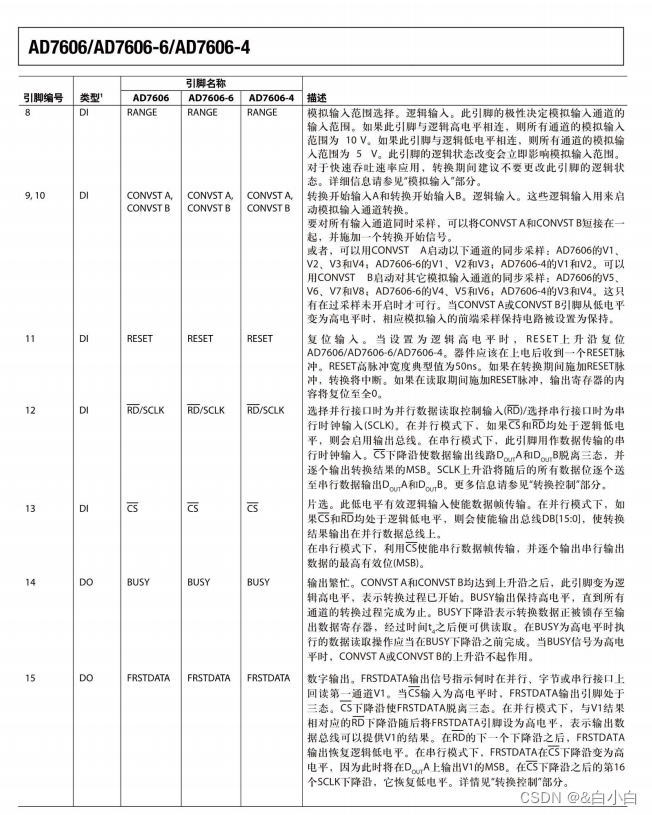

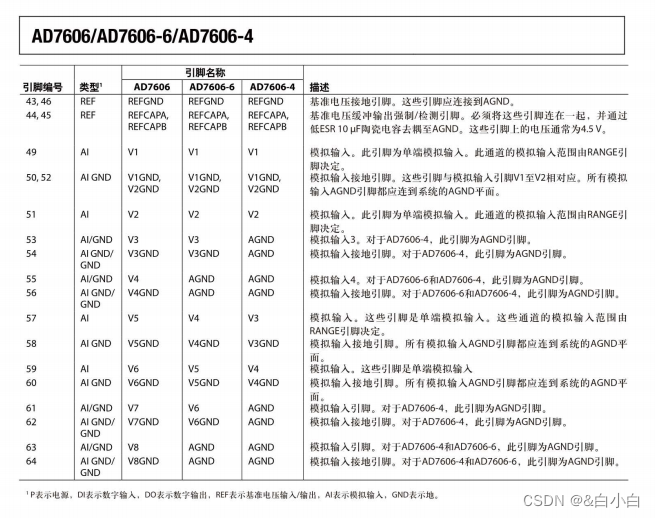

2、引脚配置和功能描述

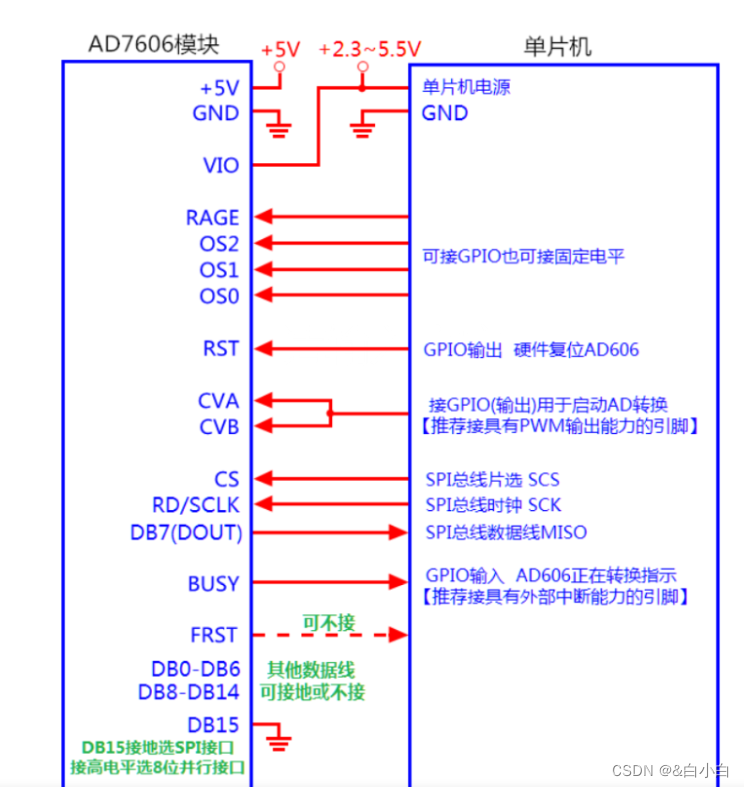

3、AD7606与FPGA相连

其中DB7(DOUT)、BUSY作为FPGA的输入接口,将DB0-DB6、DB9-DB14悬空。

4、时序图

图二是选择等待AD转换后读取,要等BUSY信号拉低后再进行数据读取;图三选择在AD转换期间读取,不需要等待BUSY信号。本实验采用的是图二转换后读取,下面开始对该时序图进行分析。

首先RESET复位由低→高→低,CONVSTACONVSTB转换命令由高→低→高,等待BUSY信号由低→高→低,等BUSY拉低后等待片选信号cs拉低并对数据进行读取,读取完成后对片选信号cs拉高。

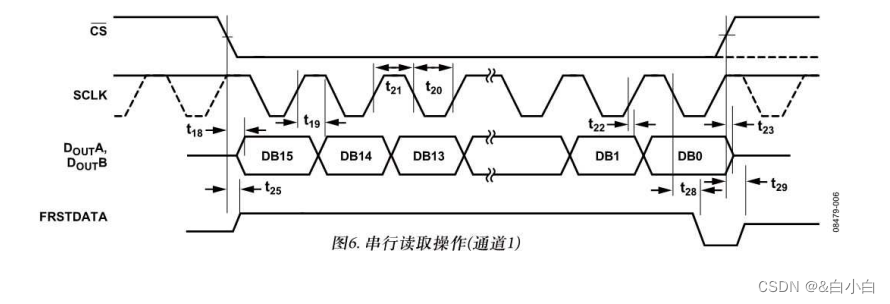

本实验使用的是串行读取方式,下面对串行读取时序图进行分析。

CS拉低后使数据输出线路DoutA和DoutB脱离三态,并逐个输出转换结果的MSB。在CS拉低后给出SCLK,根据数据手册可知在SCLK上升沿将所有数据位逐个送至串行数据输出DoutA和DoutB,但是FPGA需要在SCLK下降沿进行采集,而且每个通道每次输出16位采集数据。

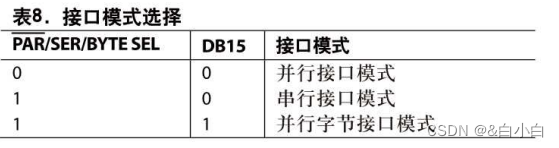

5、串行接口(PAR/SER/BYTE SEL=1)

通过串行接口从AD7606回读数据需要PAR/SER/BYTE SEL引脚接高电平,AD7606的两个串行数据输出引脚DoutA和DoutB。可通过单或双Dout线路从AD7606回读数据。本实验采用的是一路Dout线路输出数据,因为通道数据以升序输出所以用DoutA访问所有转换数据,通过DoutA访问八个转换结果时,总共需要128个SCLK周期,通道结果将以V1、V2、V3、V4、V5、V6、V7、V8的顺序输出。

6、实验结果

根据实验结果我们得知得到的仿真结果与时序图一致。

这是对八个通道进行数据采集的实验结果,其中对data_1、data_3接地,data_2接5V,data_4~data_8接3v,都得到了比较稳定的数据。

7、注意事项

- 写程序时对高低电平变化要有延时程序,具体延多少时间要根据时序图里的时间要求来取。

- FPGA是在SCLK下降沿读取数据。

- 当数据采集结果与理想结果差距较大时,不仅要检查程序问题,还要检查是不是硬件中哪个引脚虚焊、漏焊或电容电阻虚焊漏焊。

AD7606中英文数据手册:AD7606中英文数据手册-嵌入式文档类资源-CSDN下载