热门标签

热门文章

- 1来聊聊 OpenJDK 和 JVM 虚拟机_temurin jdk

- 2【Windows】Win11右键恢复完整右键菜单_windows 11 classic context menu

- 3ThinkPHP5客户关系管理系统(CRM)_thinkphp crm

- 4Flutter学习记录——28.Flutter 调试及 Android 和 iOS 打包_flutter sharedpreferences 调试

- 5公司新来的阿里p8,看了我做的APP和接口测试,甩给了我这份文档

- 6【C++】1020 月饼_1020 月饼c++

- 7Scipy 高级教程——高级插值和拟合_scipy bspline

- 8Python OpenCV 教学取得视频资讯

- 9【Mysql】Mysql开启ssl协议及Java客户端配置搭建教程_基于 ca.pem证书生成java客户端可识别的证书密码

- 10Hash 索引和 B+树索引的区别_hash和b+树的区别

当前位置: article > 正文

FPGA Verilog AD7606驱动代码:包含SPI模式读取和并行模式读取两种模式_ad7606c18驱动verilog

作者:爱喝兽奶帝天荒 | 2024-07-15 12:57:58

赞

踩

ad7606c18驱动verilog

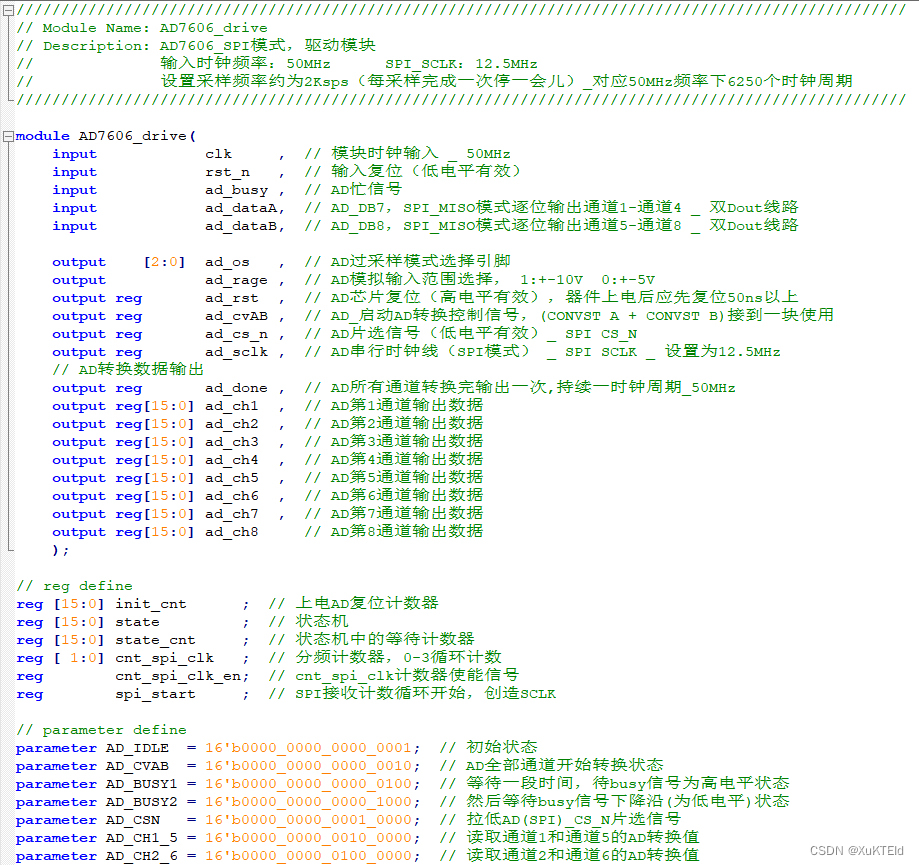

FPGA Verilog AD7606驱动代码,包含SPI模式读取和并行模式读取两种,代码注释详细

题目:FPGA Verilog AD7606驱动代码:包含SPI模式读取和并行模式读取两种模式

摘要:

本文介绍了一种基于FPGA的Verilog AD7606驱动代码,实现了对AD7606的SPI模式读取和并行模式读取。代码注释详细,易于理解和修改。通过本文的介绍,读者可以更好地了解AD7606的工作原理和驱动方式,从而在实际应用中更好地应用AD7606。

正文:

- AD7606介绍

AD7606是一款16位、6通道、同步采样ADC,具有高速、高精度的特点。它支持SPI和并行两种接口模式,可以广泛应用于各种数据采集领域。

- SPI模式读取

SPI(Serial Peripheral Interface)是一种串行外设接口,常用于微控制器和其他外设之间的通信。在SPI模式下,AD7606可以通过3线(CLK、CS、DIN/DOUT)与FPGA进行通信。

在SPI模式下,我们需要配置AD7606的寄存器来控制其工作方式和参数。下面是一个简单的SPI模式读取代码示例:

verilog复制代码

module ad7606_spi( |

|

input wire CLK |

推荐阅读

相关标签