- 1管理后台低代码PaaS平台源码:点击鼠标,就能编程_低代码控制后端程序

- 2如何抓取图片php,PHP如何获取图片?(图文+视频)

- 3数据库实用的基础知识_操作数据库用到哪些公式

- 4给你的 Discord 接入一个既能联网又能画画的 AI 机器人_leonardo discord 加机器人

- 5TransE算法原理与代码解析(2021-06-22)_transe loss

- 6AI换装 | 零基础免费AI换装保姆级教程(一)

- 7【视频采集方案】_192.168.1.35.8554

- 8【自然语言处理】:实验1布置,Word2Vec&TranE的实现

- 9利用ffmpeg截图工具截取视频关键帧

- 10人工智能在模拟空战中击落人类飞行员

FPGA-DFPGL22学习2-开发平台学习_pango design suite怎么编译

赞

踩

前言

@和原子哥一起学习FPGA

开发环境:正点原子 ATK-DFPGL22G 开发板

参考书籍:

《ATK-DFPGL22G之FPGA开发指南_V1.1.pdf》

个人学习笔记,欢迎讨论

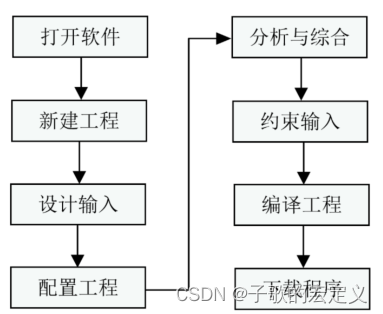

一、Pango Design Suite软件的使用流程

二、使用步骤

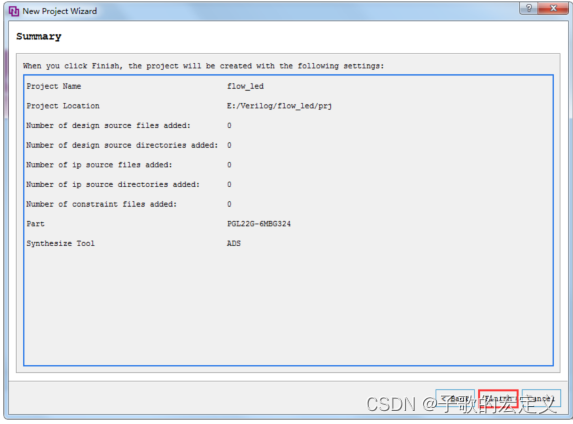

1.新建一个工程

新建一个文件夹用于存放自己的 PDS 工程

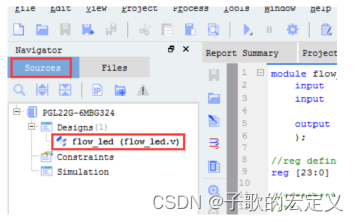

2.设计输入

新建一个 Verilog 顶层文件,然后将设计的代码输入到新建的 Verilog 顶层文件中

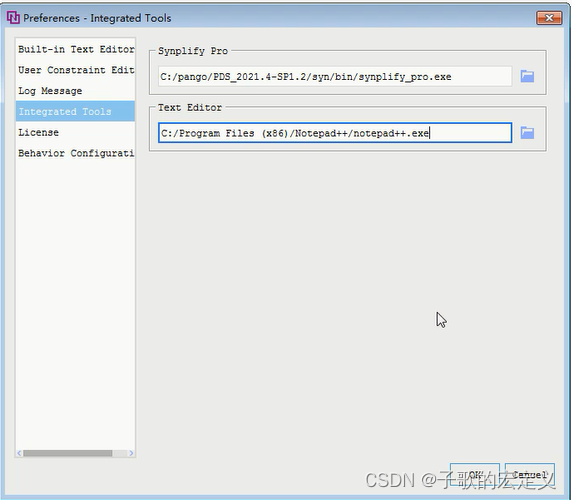

3.配置工程

关联了一下打开Verilog文件的软件为notepade++,可以不用。

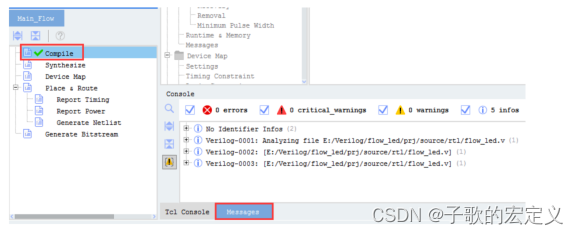

4.分析与综合(编译检查)

检查代码,如果代码出现语法错误

5.约束输入

约束表达了设计者期望满足的时序要求,规范了设计的时序行为,并在综合、实现阶段来指导工具进行布局、布线,工具会按照你的约束尽量去努力实现以满足时序要求,并在时序报告中给出结果。常用的约束包括时序约束、引脚约束等等。

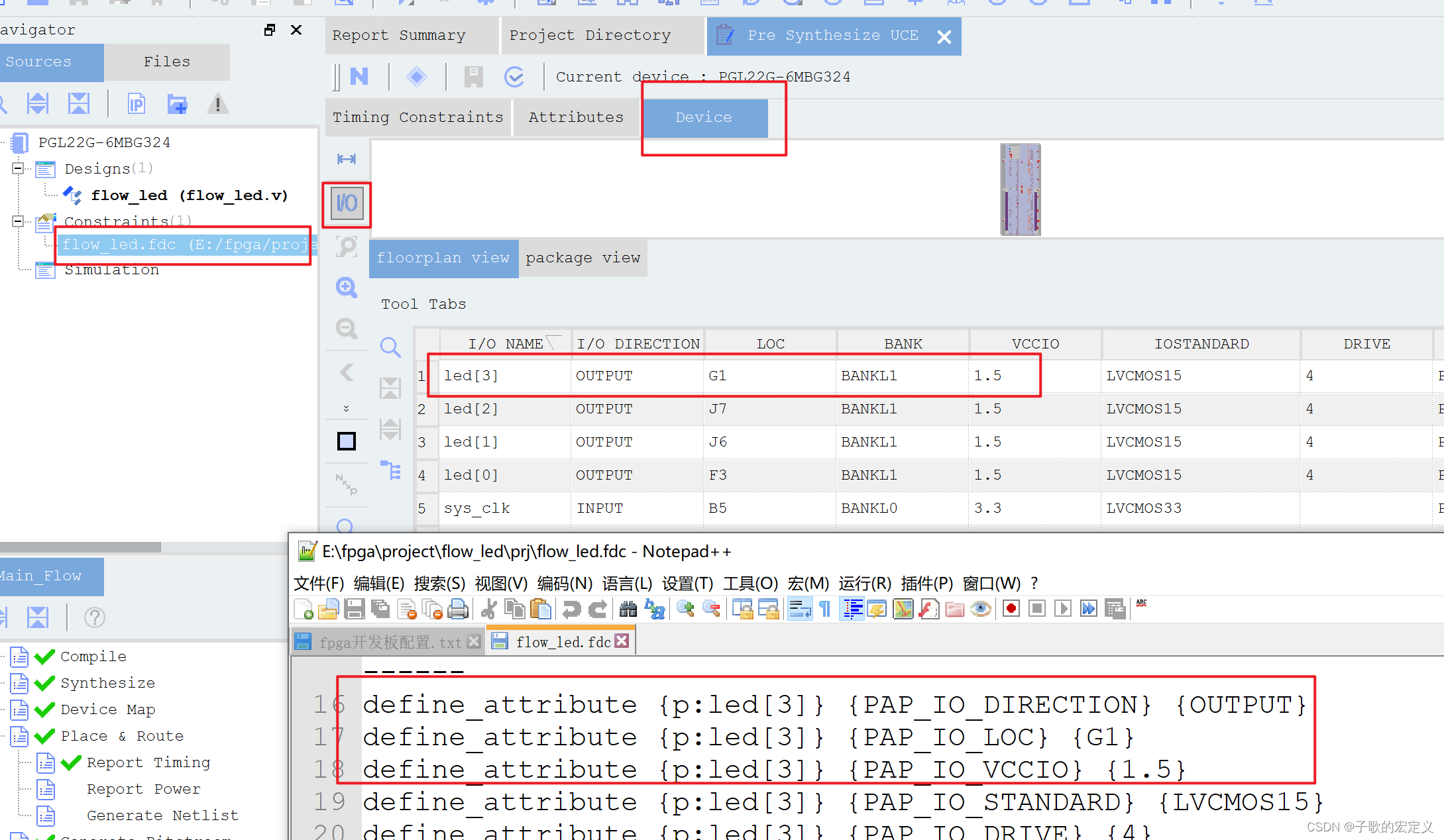

引脚约束

此处有点像UI设计单片机的管脚,选择管脚使用类型、上下拉电平等,生成对应的代码,虽然没有这样用过,但是既视感很强。

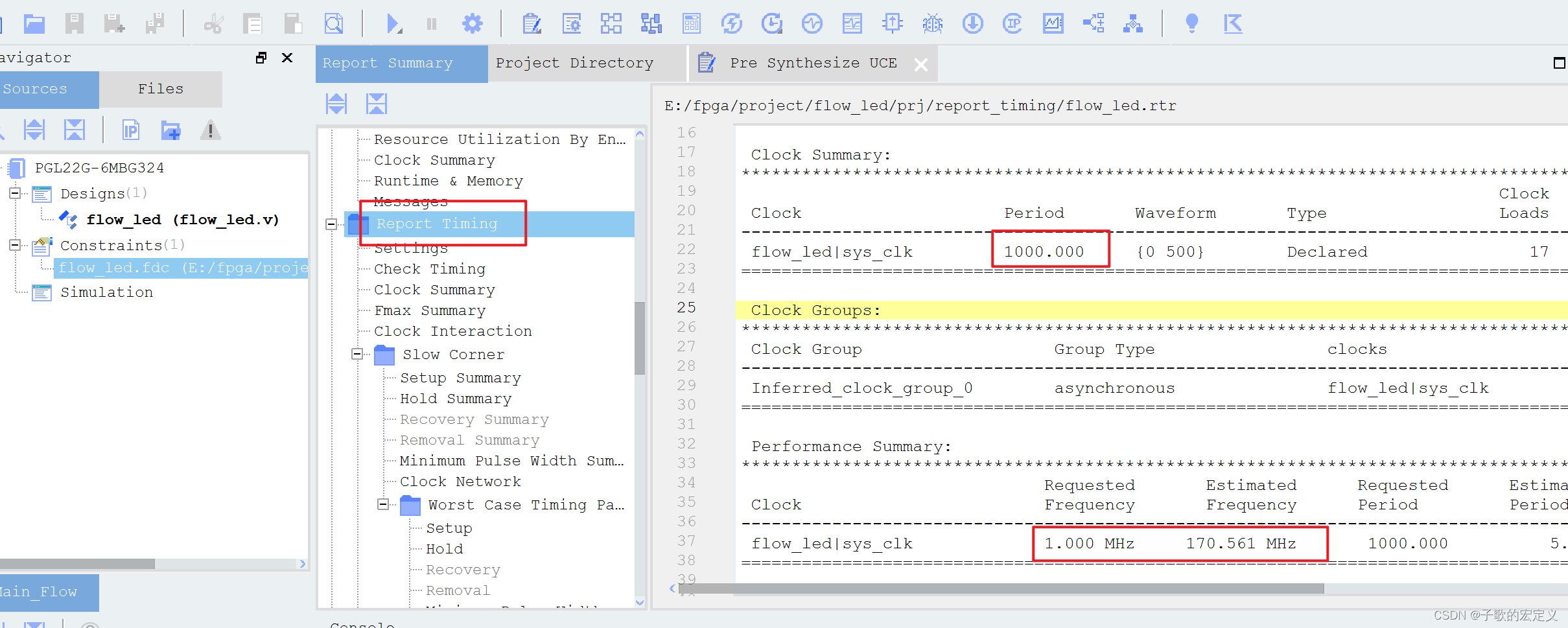

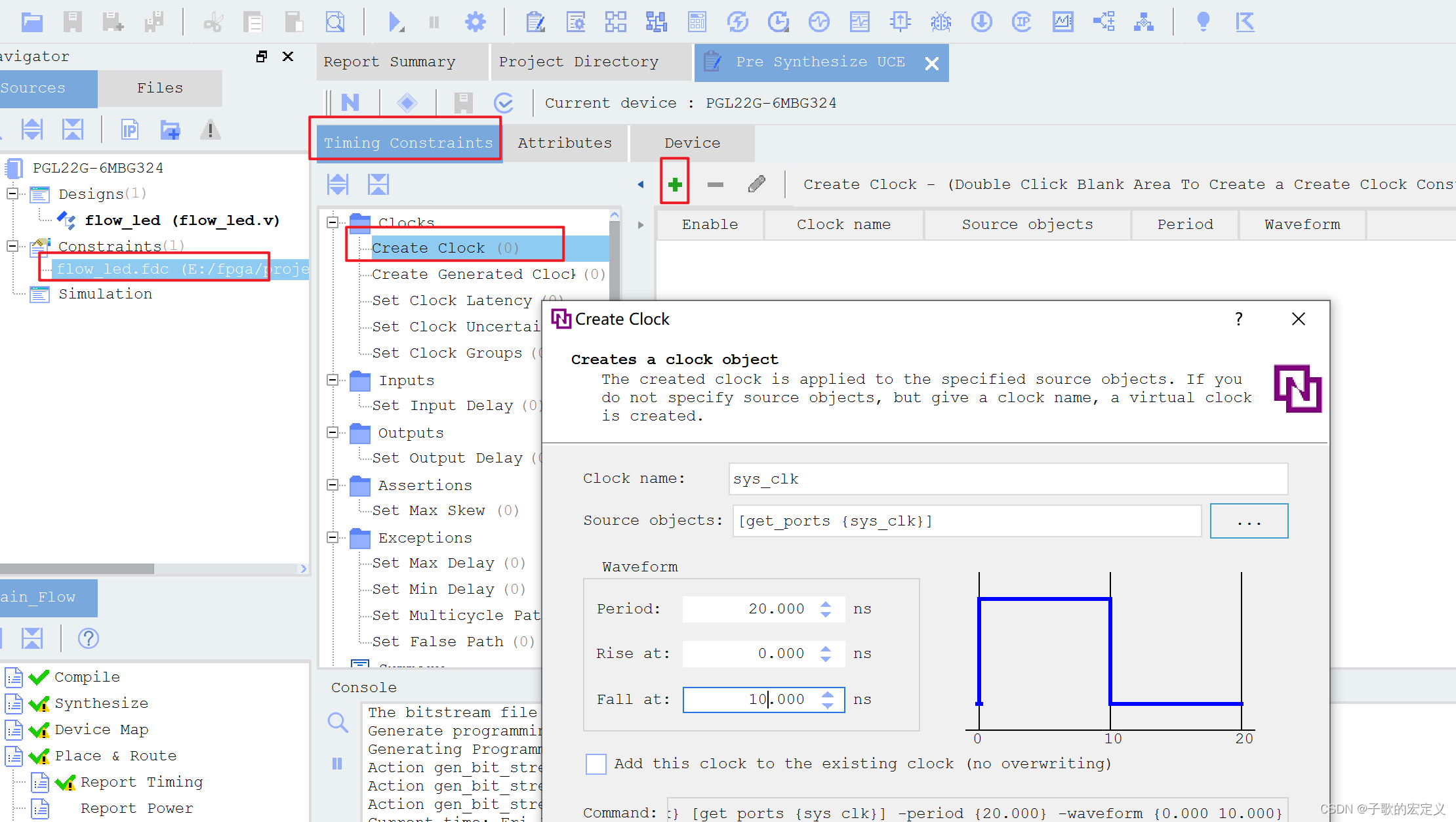

时序约束

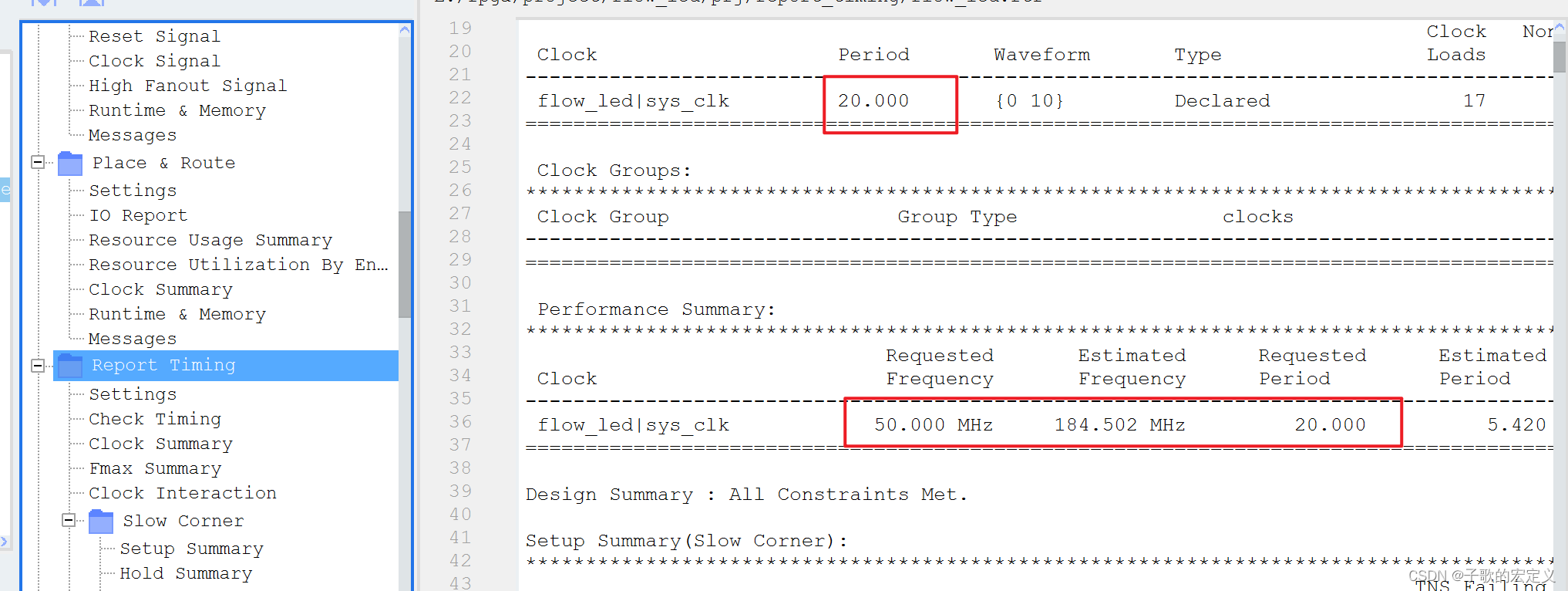

查看要求频率和性能能达到的频率。

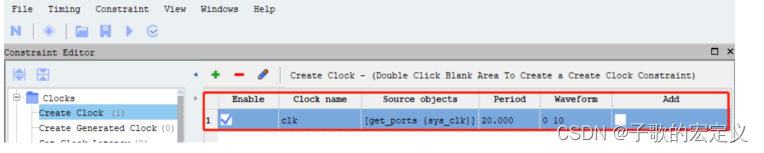

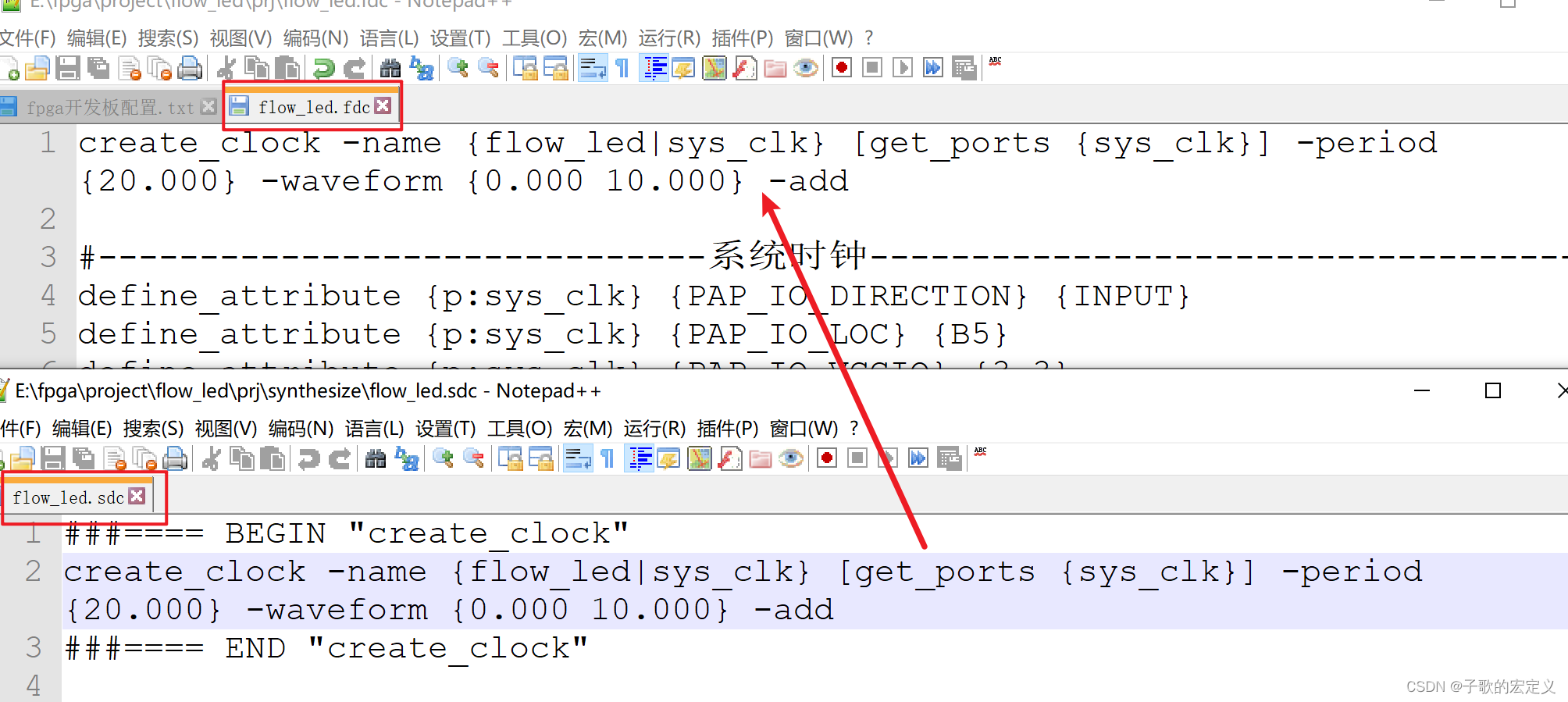

获取时序约束文件,打开ui配置后保存

将配置生成的语句,复制到fdc的约束文件中

再次编译后,就形成了新的时钟频率

也可以直接配置:

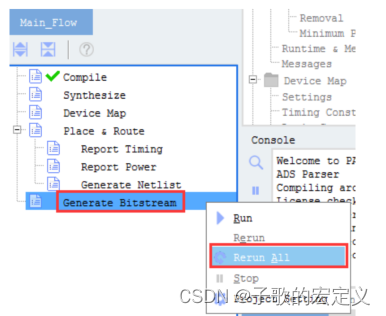

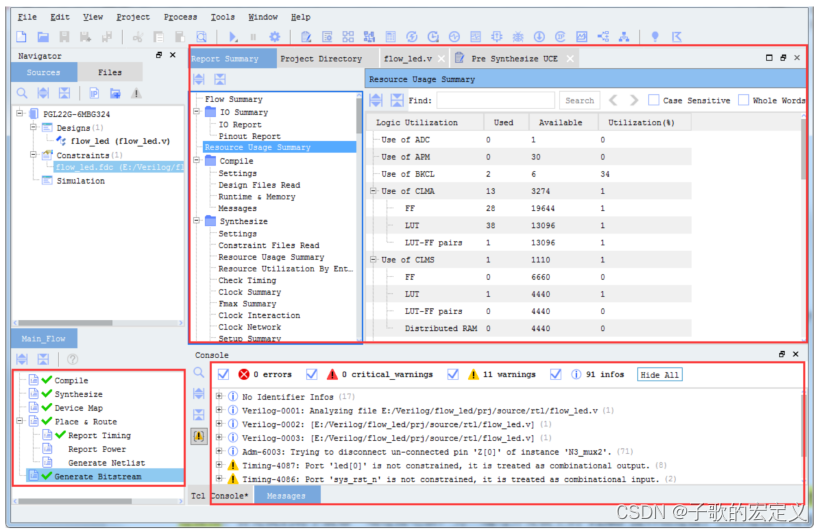

6.编译工程

在编译过程中,PDS 软件会重新检查代码,如果代码及其它配置都正确后,PDS 软件会生成一个用于下载至 FPGA 芯片的.sbit 文件。

全编辑

工程报告,查看代码使用的资源,可以对应的优化

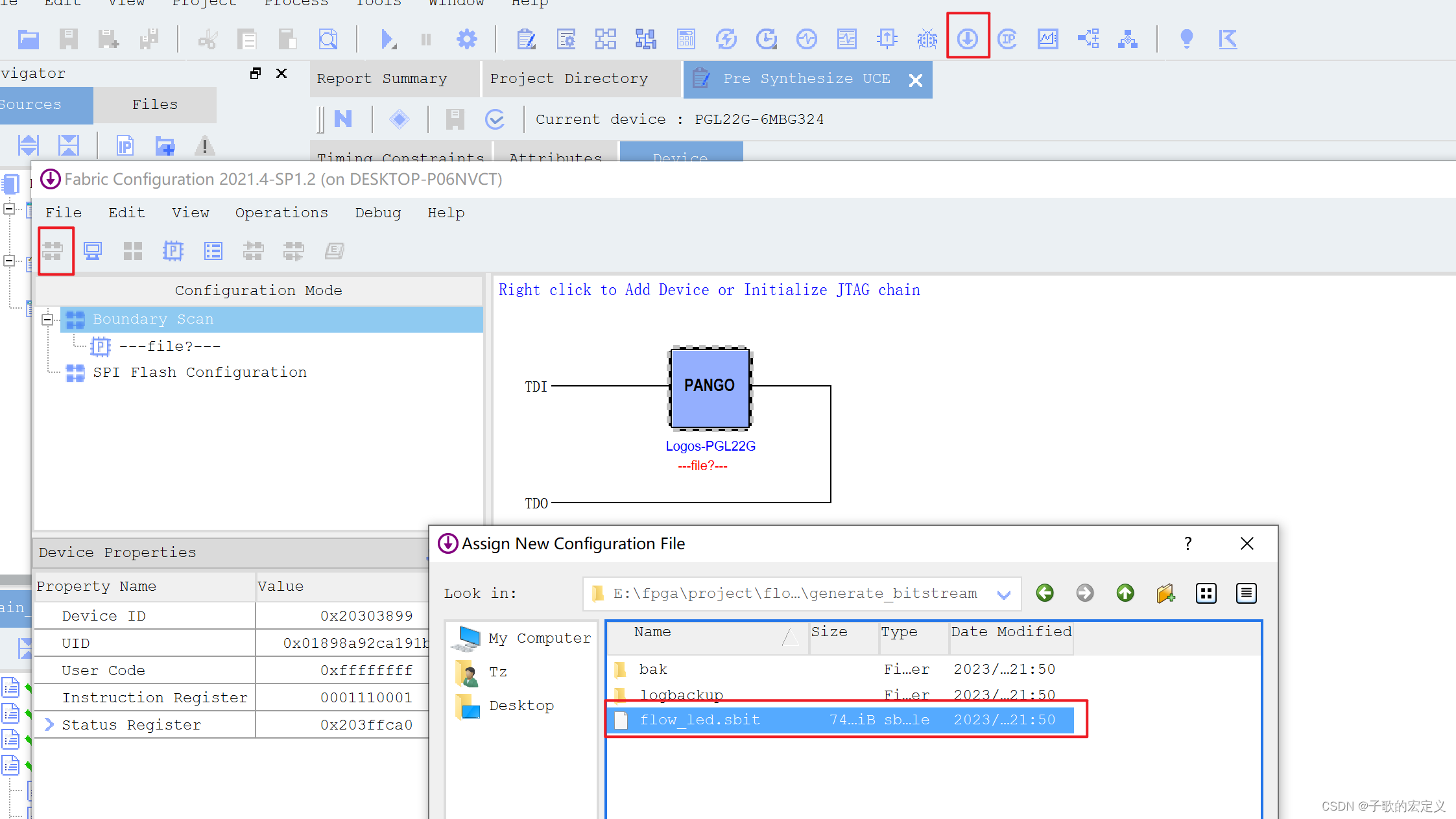

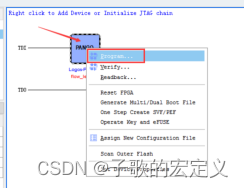

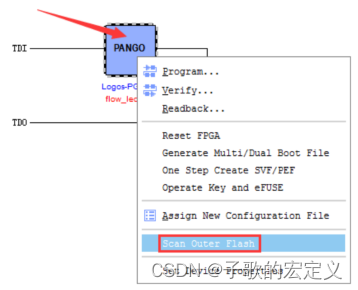

7.下载程序

下面的方法是下载到FPGA里面,掉电易失。

下载的文件是.sbit

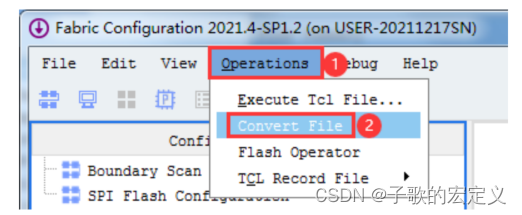

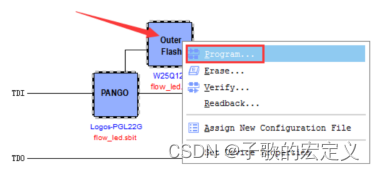

下面的方法固化程序

下载的文件是.sbit转换出来的sfc文件

硬件设备中 JTAG 口没有直连到 flash 芯片上,只能通过 FPGA 芯片将程序固化到 flash 芯片中

总结

我一直相信“磨刀不误砍柴工”,之前开发EFM32,也有专门的开发平台,虽然是英文的,但是看了一些,发现确实有一些小技巧可以使用,有时候会发现新天地。