- 1Kafka最全知识总结(建议收藏)_kafka知识介绍

- 22024工作效率提升指南:免费AI工具助你轻松工作_pearocr

- 3大模型遇上心理健康咨询:MeChat、QiaoBan、SoulChat、MindChat四大心理健康领域微调模型总结

- 4【AIGC调研系列】通义千问、文心一言、抖音云雀、智谱清言、讯飞星火的特点分析_通义千问和文心一言哪个更好用

- 5React组件化_react 引用组件化

- 6pyspark的使用和操作(基础整理)_pyspark使用

- 7车载AIGC的内容创作解决方案,拓展无限可能

- 8CSS两种盒子模型_css和模型content和width区别

- 9高速固态存储卡学习资料第701篇:基于6U VPX XC7V690T的阵列M.2高速固态存储卡_vpx 板卡 复旦微690t方案

- 10Node.js 是什么以及gulp 构建Node.js 应用

Verilog语法之if-else语句学习_verilog中else if的用法

赞

踩

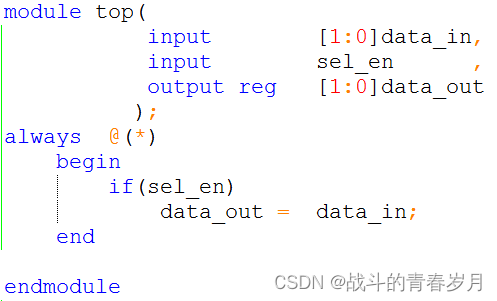

if_else 条件分支语句的作用是根据指定的判断条件是否满足来确定下一步要执行的操作。它在使用时可以采用如下三种形式:

if(<条件表达式>)

语句或语句块:

在 if_else 条件语句的这种使用形式中没有出现else 项,这种情况下条件分支语句的执行过程是:

A 如果指定的<条件表达式>成立(也就是这个条件表达式的逻辑值为“1”),则执行条件分支语句内给出的“语句或语句块”,然后退出条件分支语句的执行。

B 如果<条件表达式>不成立(也就是条件表达式的逻辑值为“0”),则不执行条件分支语句内给出的“语句或语句块”,而是直接退出条件语句的执行。

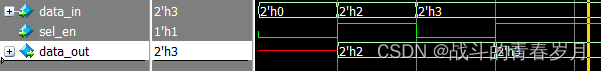

这段程序在运行时,就会根据条件表达式“sel_en”的逻辑值决定是否执行赋值语句“data_out=data_in”。如仿真结果所示,当sel_en==1时,则赋值语句就会执行,那么data_out就得到了data_in的值2;当sel_en==0时,则不执行赋值语句,data_out就保持原有的值不变。

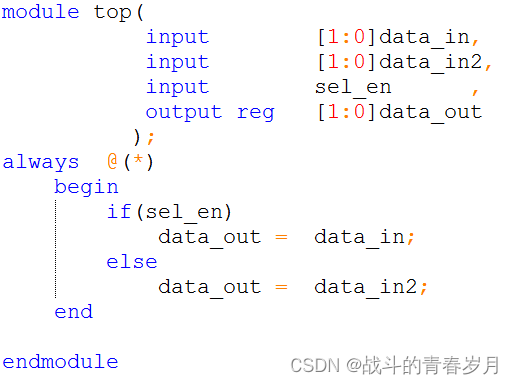

- if(<条件表达式>)

语句或语句块1

else

语句或语句块2

这种形式的条件分支语句将以如下方式得到执行:

A 如果指定的<条件表达式>成立,(也就是这个条件表达式的逻辑值为“1”),则执行条件分支语句第一行所指定的语句或语句块,然后结束条件分支语句的执行。

B 如果<条件表达式>不成立,则执行由条件分支语句内第二行的else项指定的语句或语句块2,然后结束条件分支语句的执行。

举例说明:

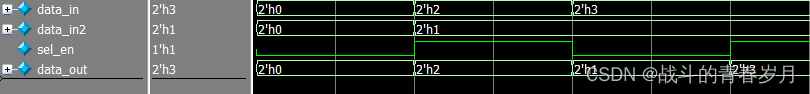

在运行这段程序时,会根据条件表达式“sel_en”的逻辑值来决定执行两条赋值语句中的哪一条。

如果sel_en==1,则执行if下的赋值语句data_out=data_in;如果sel_en==0,则执行else下赋值语句data_out=data_in2。

- if(<条件表达式>)

语句或语句块1

else if(<条件表达式2>)

语句或语句块2

..........

else

语句或语句块N

在执行这种形式if-else条件分支语句时,将按照各分支项的排列顺序对各个条件表达式是否成立做出判断,当遇到某一项的条件表达式成立时,就执行一项所指定的语句或语句块。

如果所有的条件表达式都不成立,则执行最后的else项。

这种形式的if-else条件分支语句实现了一种多路分支选择控制。

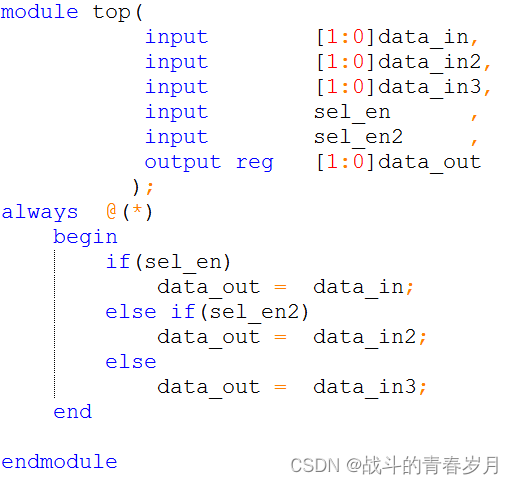

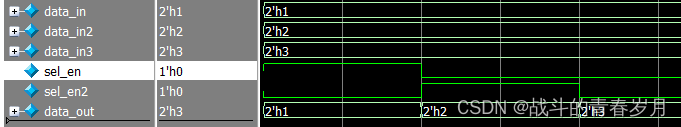

举例说明:

如果 sel_en==1时,则执行if下的赋值语句,data_out=data_in。

如果sel_en2==1与sel_en==0,时,则执行else if下的赋值语句,data_out=data_in2。

如果 sel_en和sel_en2都是0时,则执行else下的赋值语句,data_out=data_in3。