- 1postgresql如何查询物化视图脚本内容_pgsql 查看物化视图语句

- 2语义分析基础知识_语义规则

- 3史上最强Excel模板 (680个文档)_680个excel模板

- 4计算机专业春招笔试+面试题(个人总结)_计算机专业应届生招聘技术面试题

- 5大数据技术之Hadoop(HDFS)_大数据hadoop

- 6解决Flask项目无法使用公网IP访问的问题_flask小demo放到阿里云无法访问

- 7VueX_映射的计算属性的名称与 state 的子节点名称相同是怎么样的

- 8Linux(Centos7)下配置Hadoop的环境以及启动其HDFS的详细教程_centos打开hadoop显示什么才是成功

- 9创建Github Pages 仓库

- 10git pull指令报错 error: You have not concluded your merge (MERGE_HEAD exists)._> git pull --tags origin master error: you have no

Spartan6 IODELAY2 简介及应用

赞

踩

最近在做一个CMOS的项目,用的是长光的CMOS,需要对利用IODELAY对CMOS输出的信号进行校准,避免在时钟边缘发生数据跳变。在查询一堆资料后发现Spartan6 系列的IODELAY2资料很少,故只有靠自己摸索,以此记录,可为同样还在用Spartan6的同仁们提供些许帮助。

此文章以UG381手册及ISE原语库为参考。

一.IODELAY用处

器件进行通讯时,需要通过传输线进行传输,像UART、SPI、IIC等传输频率并不高,布线的传输延时可忽略不计,只要满足相应的协议就可实现数据的传输,但在高速传输时,虽然在硬件上通过差分传输来降低外界的干扰信号,但仍然由于温度、湿度影响以及芯片内部路径和外部硬件电路可能存在不匹配等问题,使信号到达FPGA的内部时间不一致。如果我们希望在时钟上升沿上采集数据,但由于线的延时,可能在时钟上升沿时数据处于变化状态,这将会导致采集的数据错误。通过IDELAYE2原语可将某根信号线进行延时操作,以达到在时钟上升沿数据处于稳定的操作。

二.IODELAY原语overview

该设计元件可用于为Spartan@-6 FPGA的输入路径提供固定延迟或可调延迟,并为输出路径提供固定延迟。这种延迟可以用于芯片的输入或输出数据的数据对齐。

IODELAY常用三种模式,FIXED、VARIABLE_FROM_ZERO、VARIABLE_FROM_HALF_MAX,当在可变模式下使用时,输入路径可以根据延迟量的增加和减少进行调整。输出延迟路径只在FIXED中可用。IODELAY还可以用于向内部路径(在FPGA结构内)添加额外的静态或可变延迟。然而,当以这种方式使用IODELAY时,该设备将不再对相关的I/O提供输入或输出路径延迟。

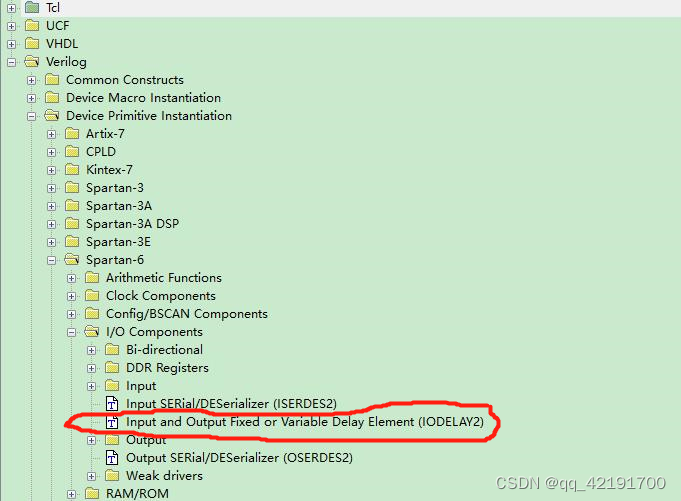

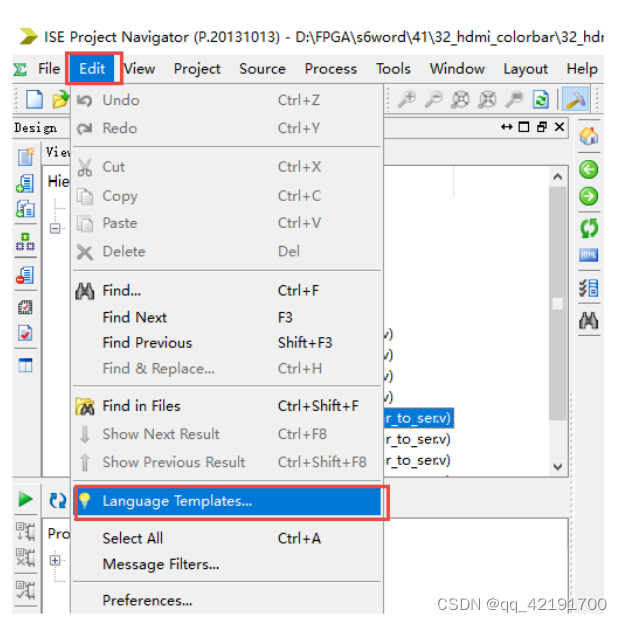

2.1原语调用

IODELAY2为用户提供精准的延时控制,在UG381中对spartan6的SelectIO有讲解。IODELAY2的例化原语可通过ISE内查看

- IODELAY2 #(

- .COUNTER_WRAPAROUND("WRAPAROUND"), // "STAY_AT_LIMIT" or "WRAPAROUND"

- .DATA_RATE("SDR"), // "SDR" or "DDR"

- .DELAY_SRC("IO"), // "IO", "ODATAIN" or "IDATAIN"

- .IDELAY2_VALUE(0), // Delay value when IDELAY_MODE="PCI" (0-255)

- .IDELAY_MODE("NORMAL"), // "NORMAL" or "PCI"

- .IDELAY_TYPE("DEFAULT"), // "FIXED", "DEFAULT", "VARIABLE_FROM_ZERO", "VARIABLE_FROM_HALF_MAX"

- // or "DIFF_PHASE_DETECTOR"

- .IDELAY_VALUE(0), // Amount of taps for fixed input delay (0-255)

- .ODELAY_VALUE(0), // Amount of taps fixed output delay (0-255)

- .SERDES_MODE("NONE"), // "NONE", "MASTER" or "SLAVE"

- .SIM_TAPDELAY_VALUE(75) // Per tap delay used for simulation in ps

- )

- IODELAY2_inst (

- .BUSY(BUSY), // 1-bit output: Busy output after CAL

- .DATAOUT(DATAOUT), // 1-bit output: Delayed data output to ISERDES/input register

- .DATAOUT2(DATAOUT2), // 1-bit output: Delayed data output to general FPGA fabric

- .DOUT(DOUT), // 1-bit output: Delayed data output

- .TOUT(TOUT), // 1-bit output: Delayed 3-state output

- .CAL(CAL), // 1-bit input: Initiate calibration input

- .CE(CE), // 1-bit input: Enable INC input

- .CLK(CLK), // 1-bit input: Clock input

- .IDATAIN(IDATAIN), // 1-bit input: Data input (connect to top-level port or I/O buffer)

- .INC(INC), // 1-bit input: Increment / decrement input

- .IOCLK0(IOCLK0), // 1-bit input: Input from the I/O clock network

- .IOCLK1(IOCLK1), // 1-bit input: Input from the I/O clock network

- .ODATAIN(ODATAIN), // 1-bit input: Output data input from output register or OSERDES2.

- .RST(RST), // 1-bit input: Reset to zero or 1/2 of total delay period

- .T(T) // 1-bit input: 3-state input signal

- );

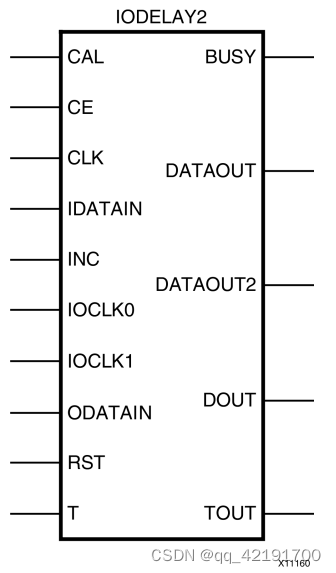

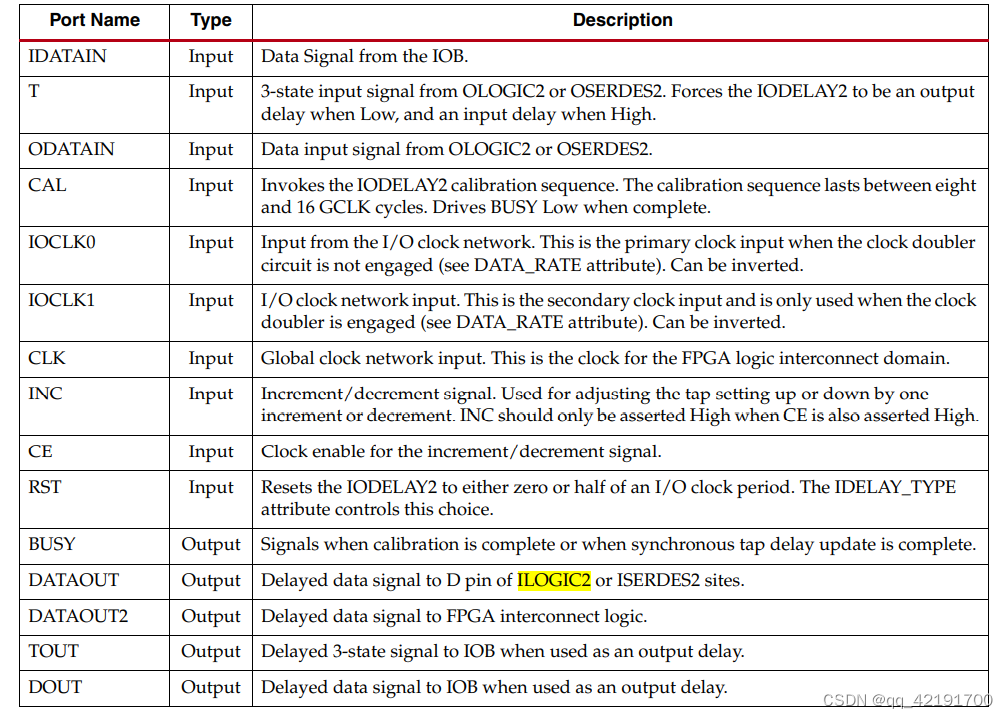

2.2端口说明

IODELAYE2端口说明

IDELAYE2属性说明

| Attribute Name | Value | Default Value | Description |

|---|---|---|---|

| IDELAY_VALUE | Integer: 0–255 | 0 | Defines the delay tap value for input delay mode. |

| IDELAY2_VALUE | Integer: 0–255 | 0 | Defines the delay tap value for secondary input delay mode. Active only when IDELAY_MODE is set to PCI |

| IDELAY_MODE | NORMAL or PCI | NORMAL | Chooses the delay mode setting. PCI is for handling PCI applications. Affects input delays only. Do not specify or modify this attribute |

| ODELAY_VALUE | Integer: 0–255 | 0 | Defines the delay tap value for output delay mode |

| IDELAY_TYPE | String: FIXED, DEFAULT, VARIABLE_FROM_ZERO, VARIABLE_FROM_HALF_MAX, DIFF_PHASE_DETECTOR | DEFAULT | Chooses the type of delay. FIXED enables a fixed input delay, and requires no clocks applied to the block. DEFAULT sets the input delay to tap 0. VARIABLE enables the increment/decrement delay mode and permits calibration. VARIABLE_FROM_ZERO and VARIABLE_FROM_HALF_MAX enables the type of reset behavior when the RST pin is asserted. DIFF_PHASE_DETECTOR enables a mode where the master and slave IODELAY2s and ISERDES2s are cascaded for use with an optional phase detector. In this mode, the master is set to half MAX and the slave is set to zero when the RST pin is asserted. |

| COUNTER_WRAP AROUND | String: STAY_AT_LIMIT, WRAPAROUND | STAY_AT_ LIMIT | Chooses the behavior when maximum or minimum tap count is exceeded. Depends on whether tap setting is being incremented or decremented. Ensures that tap count always stays in the correct operating range. |

| DELAY_SRC | String: IO, ODATAIN, IDATAIN | IDATAIN | Indicates where the IODELAY2 input is coming from. ODATAIN indicates delay source is the ODATAIN pin from the OSERDES2 or OLOGIC2. IDATAIN indicates the delay source is from an input pin. IO indicates that the signal source switches between IDATAIN and ODATAIN depending on the sense of the T (3-state) input. |

| SERDES_MODE | String: NONE, MASTER, SLAVE | NONE | When IODELAY2 is used in conjunction with ISERDES2, the attribute defines whether ISERDES2 stands alone or is a cascaded master or slave |

| SIM_TAP_DELAY | Integer: 20–100 | 50 | A simulation only attribute. Allows setting the nominal tap delay to test different values for simulation. |

| DATA_RATE | SDR, DDR | SDR | Data rate settings. An SDR clock can be supplied by a BUFIO2 clock, a BUFPLL clock, or a global clock. A DDR clock can be supplied by two separate BUFIO2 clocks or by one or two global clocks. |

其中说明几个较为重要的属性和端口,其余的可看介绍设置。

属性:

①IDELAY_VALUE:在FIXED模式下可用,值为0-255,延时时间为IDELAY_VALUE*TAP的值。

②IDELAY_TYPE:FIXED为延时固定IDELAY_VALUE的值,输出模式下只能选择FIXED;VARIABLE_FROM_ZERO为可变模式,从TAP=0开始延时;VARIABLE_FROM_HALF_MAX为直接延时一般时间,此延时的一半时间为端口IOCLK0周期的一半,列如IOCLK0为100M,则直接延时1/100M/2=5Kps。但是DATA_RATE选择DDR时,则再减少一半!!

端口:

①T:CAL,校准信号,在CAL后RST拉高,则进行校准,CAL拉高一个周期即可,注意此周期为CLK不是IOCLK0。

②IOCLK0:直接决定了延时时间,即TAP的最大值为1/IOCLK0。

③IDATAIN:数据输入信号,必须接最顶层信号或者IOBUFF,用内部信号连接则布线不通过。

④DELAY_SRC:决定了延时是输入延时还是输出延时。在DELAY_SRC=ODATAIN时,带延时的输入需要接ODATAIN,此时的输入数据可以为内部信号,输出可接DATAOUT2直接接最外层的output,此时只能用FIXED模式进行输出;在DELAY_SRC=IDATAIN时,带延时的输入需要接IDATAIN,此时可用可变模式进行可变的延时调整。注意若要使延时输出FPGA的最顶层output,则需连接DATAOUT2。

三.延时计算

延时的计算主要其实比较简单

1.首先是FIXED模式,在FIXED模式下,延时

Delaytime = (IDELAYVALUE or ODELAYVALUE) * SIMTAPDELAYVALUE(0-100)+ 110ps

此110ps为自带的延时,即在IDELAYVALUE取0时也会存在(此110ps是在modelsim上给出的延时,但是在示波器采样时发现不知110ps,甚至达到2ns,这个之后再仔细测测看)

2.VARIABLE_FROM_ZERO模式就是可变模式,通过INC和CE的拉高可增加一个TAP的延时,此延时最大时间为IOCLK0的周期(DDR时则为IOCLK0周期的一半)。

剩下的仿真什么的没啥意思我就不放了,希望对大家有帮助吧。