热门标签

热门文章

- 1Kerberos安全认证-连载10-Hive Kerberos 安全配置及访问_idea连接 kerberos 认证的hiveserver2_hive kerberos认证

- 2Jupyter 安装 nbextensions 插件_jupyter-contrib-nbextensions

- 3机器学习之支持向量机算法

- 4100 行代码实现用户登录注册与 RESTful 接口 - 手把手教程附 Python 源码_restful api注册

- 530岁转行测试工程师_从客服转行游戏测试工程师,我完成月薪8.5k小目标

- 6【MySQL的存储过程】_mysql存储过程创建

- 7go整合es_go es

- 8【大模型实战案例】手把手教大家微调大模型 Llama 3_llama3微调

- 9经典文献阅读之--lris(优于Scan Context的回环检测)_lidar iris for loop-closure detection

- 10区块链和人工智能的关系以及经典案例_区块链与人工智能

当前位置: article > 正文

DDS信号发生器Verilog波形发生器FPGA_dds信号发生器quartus ii 仿真软件编写

作者:IT小白 | 2024-06-15 23:07:40

赞

踩

dds信号发生器quartus ii 仿真软件编写

名称:DDS信号发生器Verilog波形发生器

软件:Quartus

语言:Verilog

要求:

1.可产生正弦波,锯齿波,三角波,方波4种波形,频率可调

2.具有波形选择、起动、停止功能。

代码下载:DDS信号发生器Verilog波形发生器_Verilog/VHDL资源下载

代码网:hdlcode.com

![]()

部分代码展示

`timescale 1ns / 1ps //输出频率f=clk_50M*frequency/2^10 module DDS_top( input clk_50M,//时钟输入 input wave_en,//波形起的停止开关 input [1:0] wave_select,//波形选择开关:00输出锯齿波,01输出sin,10输出方波,11输出三角波 input [7:0] frequency,//频率控制字,控制输出波形频率 output [7:0] wave//输出波形 ); wire [9:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; wire [7:0] douta_juchi; //锯齿ROM juchi_ROM i_juchi_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_juchi) // output wire [7 : 0] douta ); //方波ROM fangbo_ROM i_fangbo_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_fangbo) // output wire [7 : 0] douta ); //三角波ROM sanjiao_ROM i_sanjiao_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sin) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_50M(clk_50M), . frequency(frequency),//频率控制字 . addra(addra)//输出地址 ); //波形选择控制 wave_sel i_wave_sel( . clk_50M(clk_50M), . wave_en(wave_en), . wave_select(wave_select),//00输出锯齿波,01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_sin(douta_sin), //正弦 . douta_juchi(douta_juchi), . wave(wave)//输出波形 ); endmodule

设计文档(文档点击可下载):

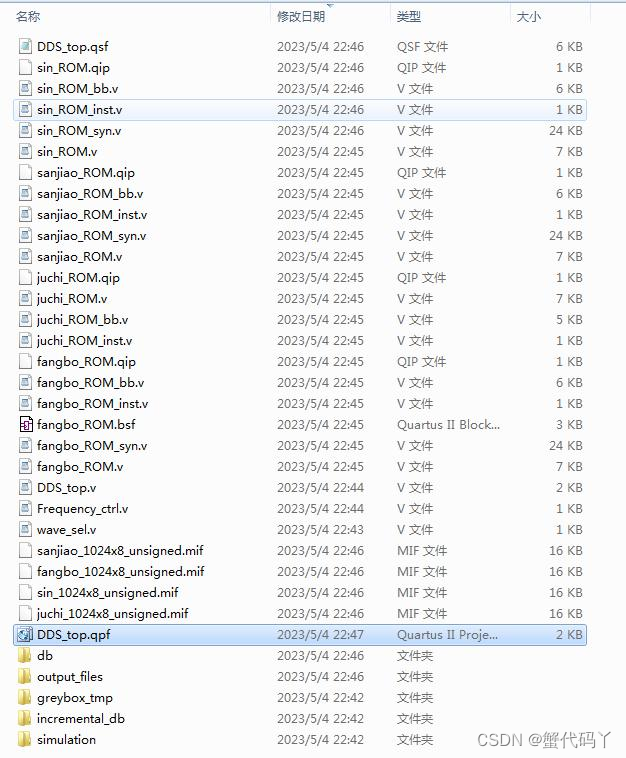

1. 工程文件

2. 程序文件

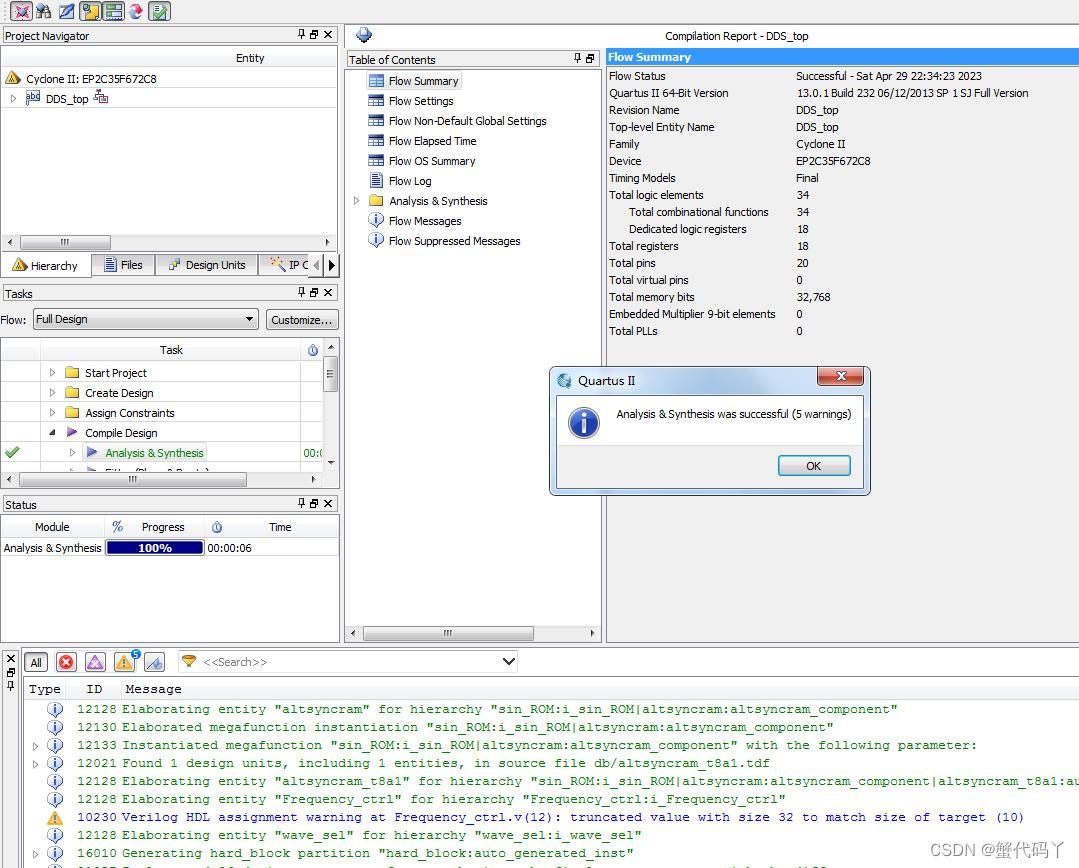

3. 程序编译

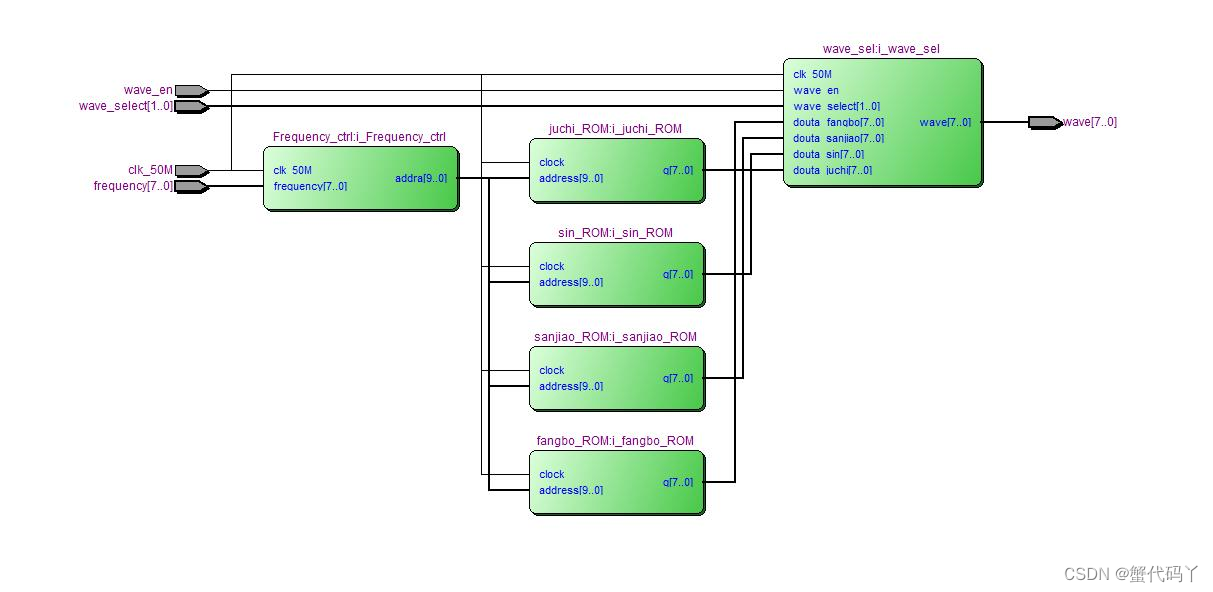

4. RTL 图

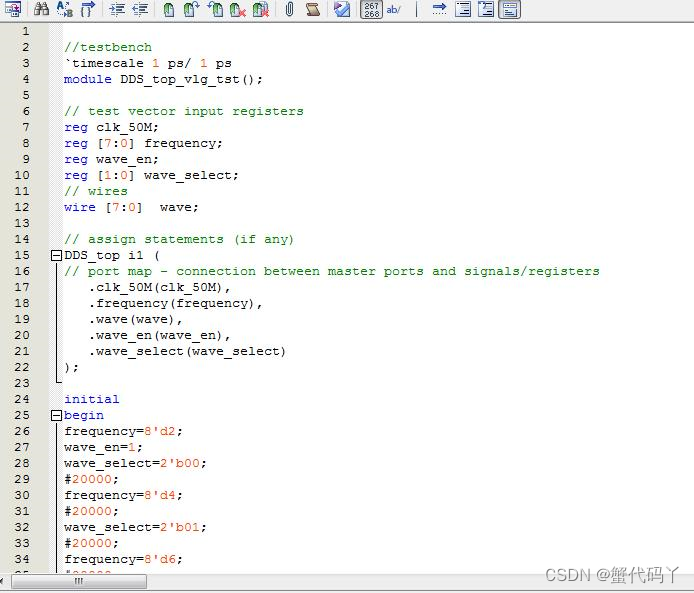

5. Testbench

6. 仿真图

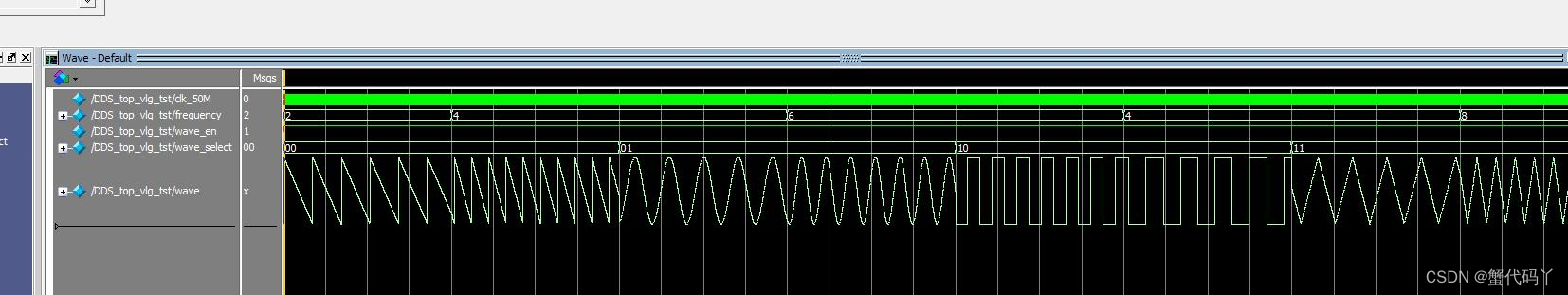

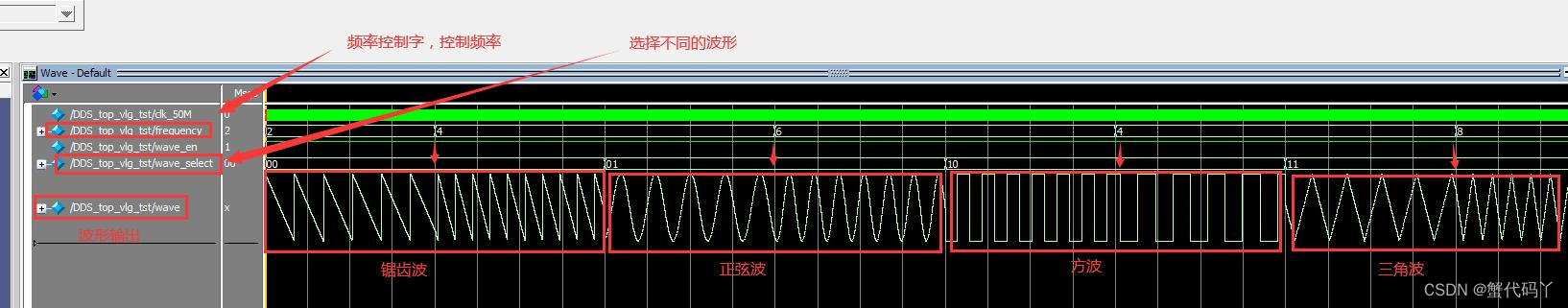

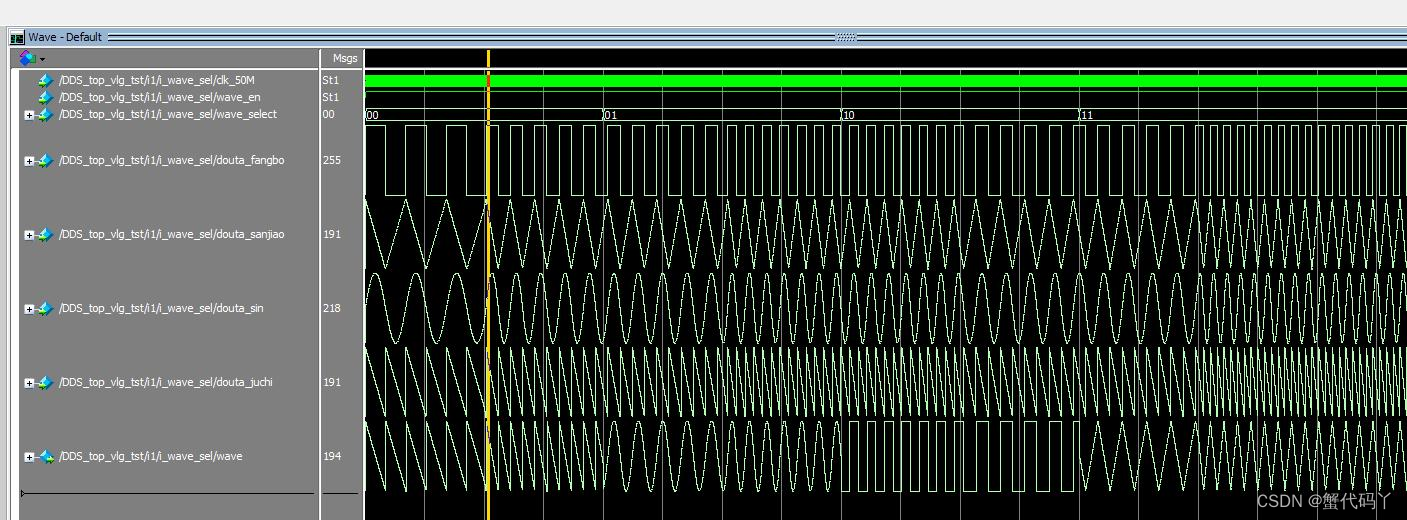

整体仿真图

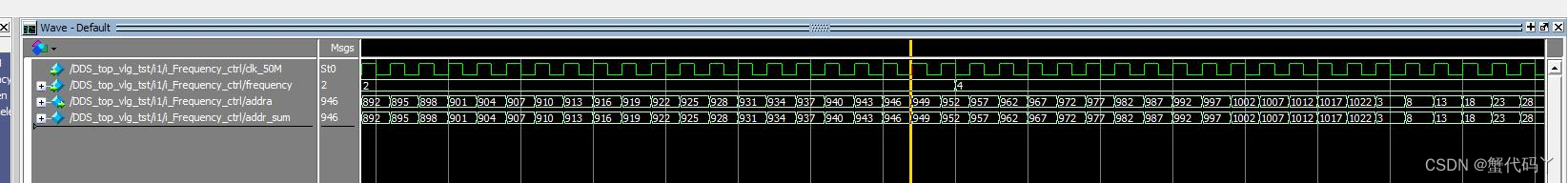

相位累加器模块

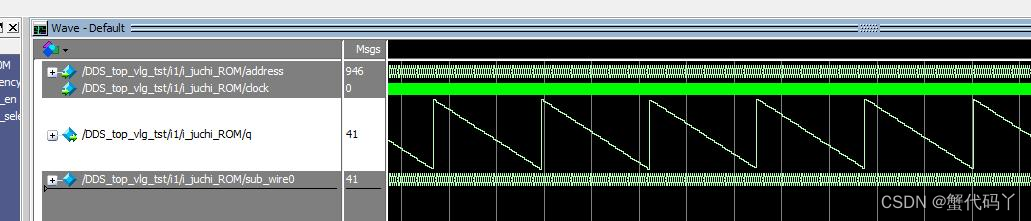

锯齿波 ROM

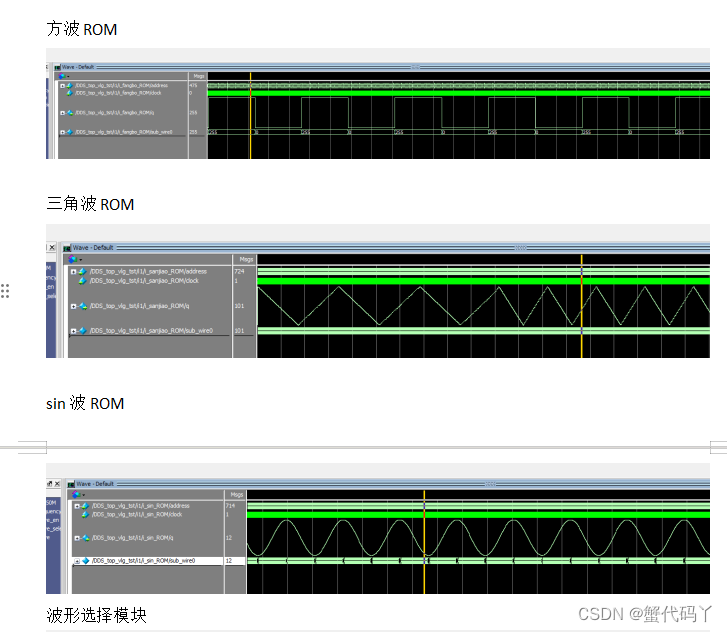

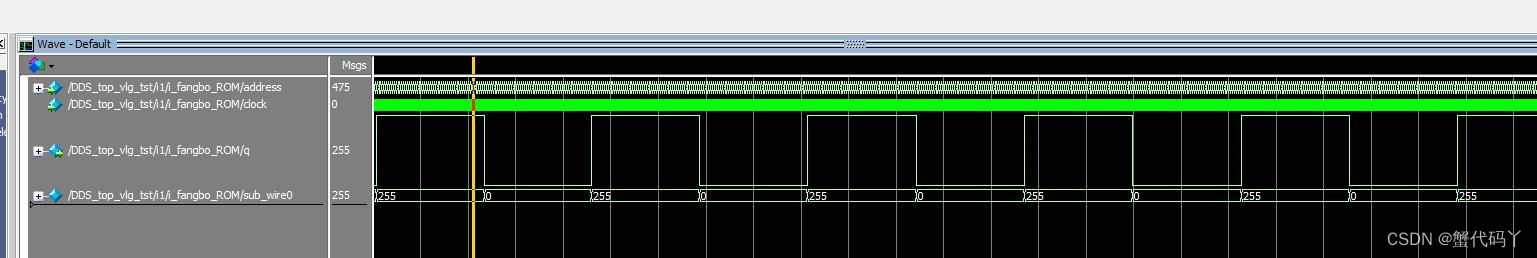

方波 ROM

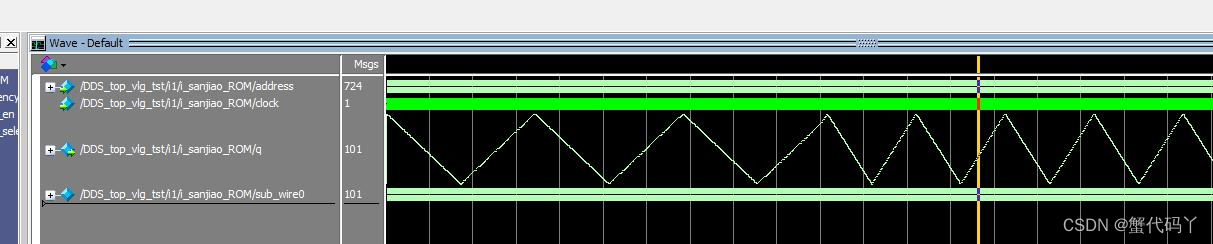

三角波 ROM

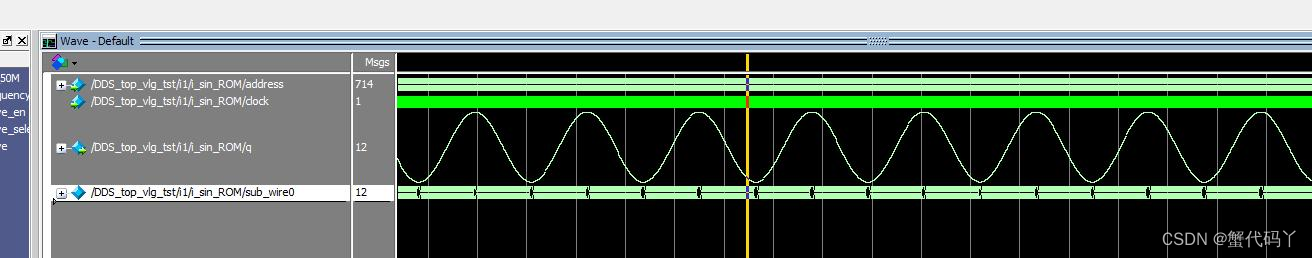

sin 波 ROM

波形选择模块

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/IT小白/article/detail/724181

推荐阅读

相关标签