- 1Seata事务管理---Seata简介

- 2C语言强化-1.数据结构概述

- 3lora训练调参

- 4百度智能云千帆 ModelBuilder 技术实践系列:通过 SDK 快速构建并发布垂域模型_百度智能云千帆modelbuilder 最丰富的大模型,全流程工具链

- 5Qt(C++) | QPropertyAnimation动画(移动、缩放、透明)篇_qt 动画放大

- 6windows的svn_windows svn

- 7YOLOv8的代码如何升级到YOLOv10_yolov10 attributeerror: can't get attribute 'scdow

- 8分布式锁3: zk实现分布式锁3 使用临时顺序节点+watch监听实现阻塞锁_zk watch 与监听事件

- 9(五)阿里云ECS服务器的基本管理与磁盘扩容_阿里云ecs磁盘扩容

- 10【饭谈】面试官让你来个“自我介绍”,你准备怎么说?_自我介绍 需要说 技术栈

ZYNQ通过AXI DMA实现PL发送连续大量数据到PS DDR_zynq axidma

赞

踩

硬件:ZYNQ7100

软件:Vivado 2017.4、Xilinx SDK 2017.4

ZYNQ PL 和 PS 的通信方式有 AXI GPIO、BRAM、DDR等。对于数据量较少、地址不连续、长度规则的情况,BRAM 比较适用。而对于传输速度要求高、数据量大、地址连续的情况,比如 ADC,可以通过 AXI DMA 来完成。

1、硬件设计

1.1 ZYNQ7 Processing System IP核

选中 M AXI GP0 和 S AXI HP0

选中 PL 到 PS 的中断端口

选中 PL 到 PS 的中断端口

其他按开发板要求配置。

其他按开发板要求配置。

1.2 AXI Direct Memory Access IP核

AXI Direct Memory Access IP核配置如下图所示。由于只需要 PL 向 PS 的 DDR写数据,所以只使能了写通道。

1.3 AXI4-Stream Data FIFO IP核

AXI4-Stream Data FIFO IP核用于缓存数据,它的接口按照 AXI4-Stream 协议通信,它的配置如下图所示。

1.4 连续数据生成模块

编写一个生成连续数据的模块,它在接收到一个触发信号上升沿后,按 AXI4-Stream 协议输出连续数据。

module dma_frame_gen #( parameter TRANS_NUM = 32'd1550336 //1514*1024 ) ( input resetn, input clk, input trans_start, // axi-stream output [31:0] m_axis_tdata, output [3:0] m_axis_tkeep, output m_axis_tlast, output m_axis_tvalid, input m_axis_tready ); assign m_axis_tkeep = 4'b1111; reg trans_start_0, trans_start_1; wire pos_trans_start; assign pos_trans_start = trans_start_0 & (~trans_start_1); always @(posedge clk or negedge resetn) begin if(~resetn) begin trans_start_0 <= 1'd0; trans_start_1 <= 1'd0; end else begin trans_start_0 <= trans_start; trans_start_1 <= trans_start_0; end end localparam IDLE = 2'b00; localparam TRANS = 2'b01; localparam DONE = 2'b10; reg [1:0] state; reg [31:0] trans_cnt; reg [31:0] r_tdata; reg r_tvalid, r_tlast; always @(posedge clk or negedge resetn) begin if(!resetn) begin state <= IDLE; r_tdata <= 32'd0; r_tvalid <= 1'b0; end else begin r_tdata <= 32'd0; r_tvalid <= 1'b0; case(state) IDLE: begin if(pos_trans_start && m_axis_tready) begin state <= TRANS; end else begin state <= IDLE; end end TRANS: begin if(trans_cnt < TRANS_NUM) begin state <= TRANS; r_tvalid <= 1'b1; r_tdata <= trans_cnt; end else begin state <= DONE; end end DONE: begin state <= IDLE; end default: begin state <= IDLE; end endcase end end always @(posedge clk or negedge resetn) begin if(!resetn) begin r_tlast <= 1'b0; end else begin if(state == TRANS && trans_cnt == TRANS_NUM-1) begin r_tlast <= 1'b1; end else begin r_tlast <= 1'b0; end end end always @(posedge clk or negedge resetn) begin if(!resetn) begin trans_cnt <= 0; end else begin if(state == TRANS) begin trans_cnt <= trans_cnt + 1; end else begin trans_cnt <= 32'd0; end end end assign m_axis_tdata = r_tdata; assign m_axis_tlast = r_tlast; assign m_axis_tvalid = r_tvalid; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

把此模块添加到 block design 里,软件能自动识别 AXI4-Stream 端口。

1.5 block design整体设计

block design整体设计如下图所示,主要的数据通路用橙色线表示。dma_frame_gen 的 m_axis 端口连接 AXI4-Stream Data FIFO 的 S_AXIS 端口,AXI4-Stream Data FIFO 的 M_AXIS 端口连接 AXI DMA Memory Access 的 S_AXIS_S2MM 端口,AXI DMA Memory Access 的 M_AXI_S2MM 端口连接 AXI SmartConnect 的 S00_AXI 端口,AXI SmartConnect 的 M00_AXI 端口连接 ZYNQ7 Processing System 的 S_AXI_HP0 端口。

2、软件设计

2.1 AXI DMA 初始化和 DMA 中断函数

void axi_dma_init()

{

XAxiDma_Config *axi_dma_cfg_ptr;

axi_dma_cfg_ptr = XAxiDma_LookupConfig(XPAR_AXIDMA_0_DEVICE_ID);

XAxiDma_CfgInitialize(&axi_dma_0_inst, axi_dma_cfg_ptr);

// interrupt

XScuGic_SetPriorityTriggerType(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID, 0xA0, 0x3);

XScuGic_Connect(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID, (Xil_InterruptHandler) axi_dma_rx_intr_handler, &axi_dma_0_inst);

XScuGic_Enable(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID);

XAxiDma_IntrEnable(&axi_dma_0_inst, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DEVICE_TO_DMA);

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

void axi_dma_rx_intr_handler(void *CallBackRef) { int timeout; u32 irq_status; XAxiDma *axidma_inst = (XAxiDma *)CallBackRef; irq_status = XAxiDma_IntrGetIrq(axidma_inst, XAXIDMA_DEVICE_TO_DMA); XAxiDma_IntrAckIrq(axidma_inst, irq_status, XAXIDMA_DEVICE_TO_DMA); if ((irq_status & XAXIDMA_IRQ_ERROR_MASK)) { // error = 1; XAxiDma_Reset(axidma_inst); timeout = 10000; while(timeout) { if (XAxiDma_ResetIsDone(axidma_inst)) break; timeout--; } return; } if ((irq_status & XAXIDMA_IRQ_IOC_MASK)) { dma_rx_done = 1; } }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

2.2 初始化中断

void interrupt_init()

{

XScuGic_Config *intc_cfg_ptr;

intc_cfg_ptr = XScuGic_LookupConfig(XPAR_SCUGIC_SINGLE_DEVICE_ID);

XScuGic_CfgInitialize(&scugic_inst, intc_cfg_ptr, intc_cfg_ptr->CpuBaseAddress);

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, &scugic_inst);

Xil_ExceptionEnable();

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

2.3 初始化 AXI GPIO

void axi_gpio_init()

{

XGpio_Initialize(&axi_gpio_0_inst, XPAR_GPIO_0_DEVICE_ID);

XGpio_SetDataDirection(&axi_gpio_0_inst, 1, 0x01);

}

- 1

- 2

- 3

- 4

- 5

2.4 main 函数

在 main 函数中先执行中断、AXI GPIO 和 AXI DMA 的初始化函数,然后 AXI GPIO 输出一个信号上升沿触发 dma_frame_gen 模块输出连续数据,XAxiDma_SimpleTransfer 函数触发一次 DMA 传输,Xil_DCacheFlushRange 函数刷新 Data Cache。DMA 传输完成后触发 DMA 中断,如果 DMA 传输成功,dma_rx_done 在 DMA 中断中置 1。

int main() { int status; FIL fil; volatile int rec_data[BUF_SIZE]; interrupt_init(); axi_gpio_init(); axi_dma_init(); XGpio_DiscreteWrite(&axi_gpio_0_inst, 1, 0x01); XAxiDma_SimpleTransfer(&axi_dma_0_inst, (UINTPTR) rec_data, BUF_SIZE*sizeof(int), XAXIDMA_DEVICE_TO_DMA); XGpio_DiscreteClear(&axi_gpio_0_inst, 1, 0x01); Xil_DCacheFlushRange((UINTPTR) rec_data, BUF_SIZE*sizeof(int)); //刷新Data Cache while(!dma_rx_done); return 0; }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

3、上板验证

用 Debug 模式运行程序,在 main 函数的 return 0; 行放断点,当程序运行到断点处时,看 rec_data 中存的是从 0 到 BUF_SIZE-1 的连续数值,实验成功。

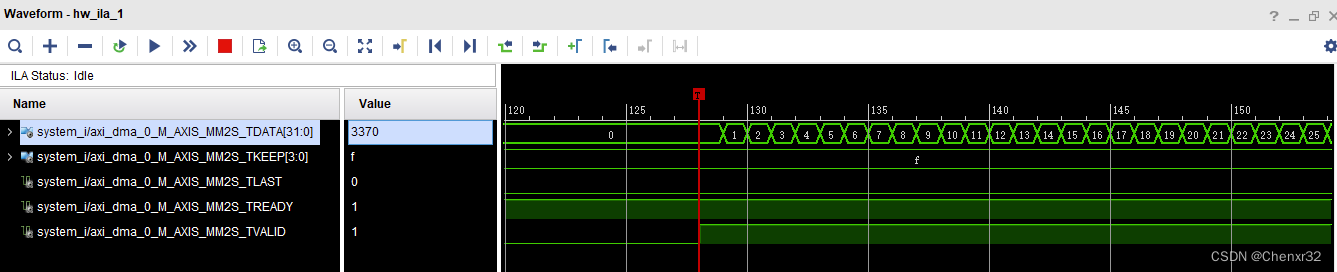

dma_frame_gen 的 m_axis 端口输出波形如下图所示。

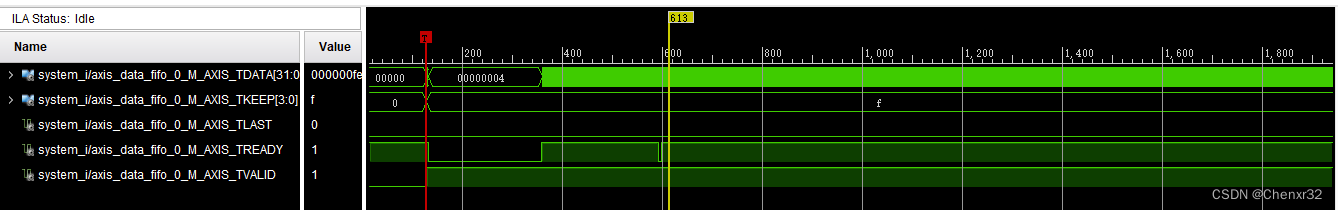

AXI4-Stream Data FIFO 的 M_AXIS 端口输出波形如下图所示。

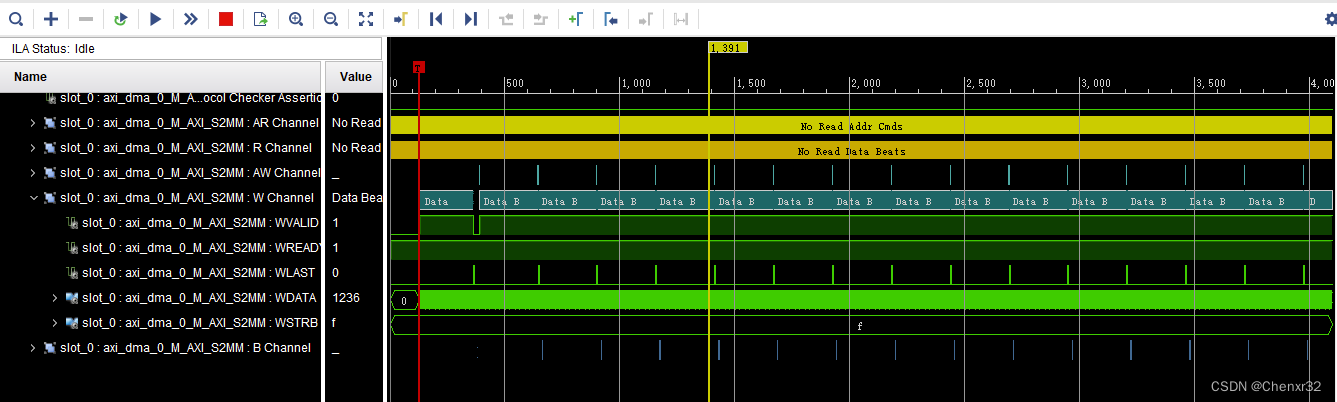

AXI DMA Memory Access 的 M_AXI_S2MM 端口的写通道波形如下图所示。