- 1使用openCV进行图像处理_opencv图像处理

- 2InstantID_instantidmodelloader

- 3pgsql 删除创建索引_PostgreSql重建索引

- 4listeners和advertised.listeners区别_listeners和advertised.listeners 是什么

- 5项目管理PMP多大作用?

- 6AIGC时代,重塑人的核心竞争力?

- 7JSON在线格式化解析工具(超好用)_在线格式化json字符串

- 8CV笔记:图片数据处理_图像数据处理

- 92024年Github上最牛的Java进阶教程及Java实战项目都在这里了!(2)_2024 java 高级进阶手册

- 10GPT问答记录:微信小程序动态tabBar开发配置(服务端+前端代码)_微信小程序 tabbar动态配置

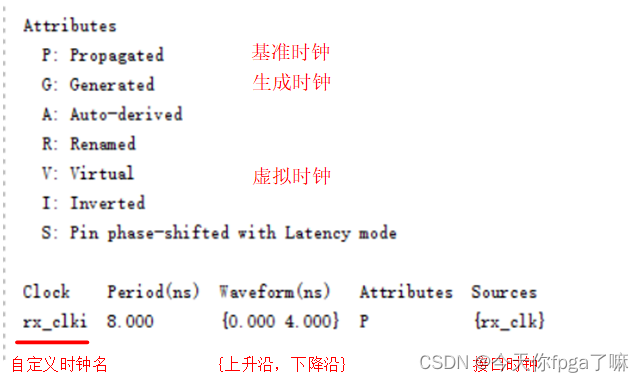

三、基准时钟、生成时钟、虚拟时钟的约束和意义_vivado 为什么pll输出的时钟变成虚拟时钟

赞

踩

前言:前面从理论角度出发学习了 时序分析理论基础 和 IO接口时序分析基本原理和意义,本篇从设计的角度学习如何合理添加时钟约束。

一、基准时钟(base clock)和生成时钟(generate clock)

这里以前面做过的千兆以太网 HDMI 项目时钟树为例:

基准时钟为 sclkin,其余通过 PLL 的生成的时钟是生成时钟(generate clk)。

Vivado 约束基准时钟和生成时钟规则:

- 如果基准时钟输入给 PLL,由于在 PLL 配置界面设置了基准时钟频率等信息,所以不需要额外再次约束基准时钟。在约束信息里会自动添加基准时钟约束,并且自动会把生成时钟也会添加约束。

- 如果基准时钟并没有送入 PLL 直接通过分频或者不分频的方式给内部模块使用就需要添加基准时钟约束和生成时钟约束。

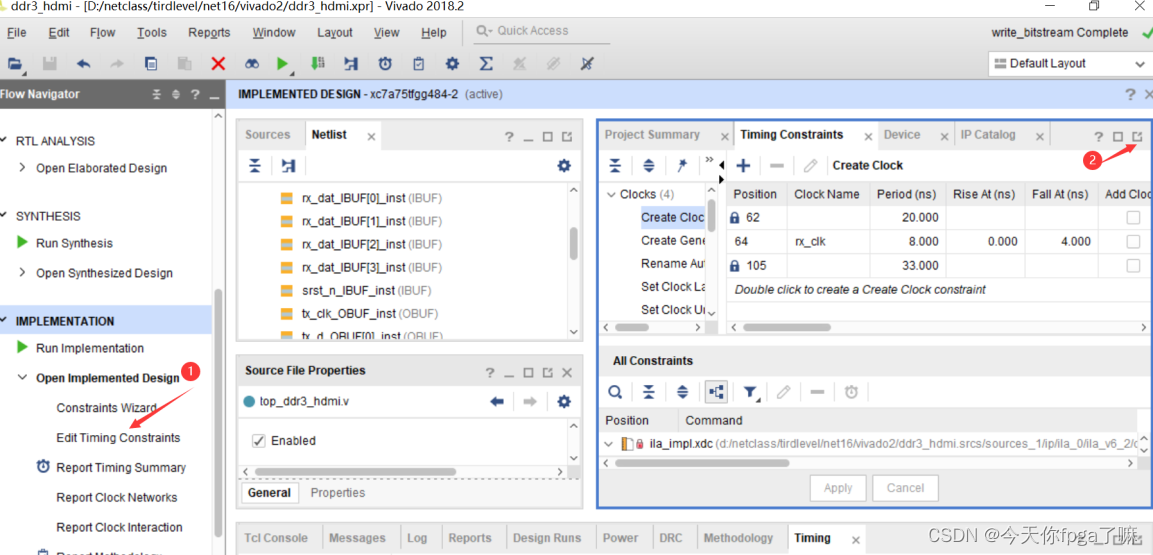

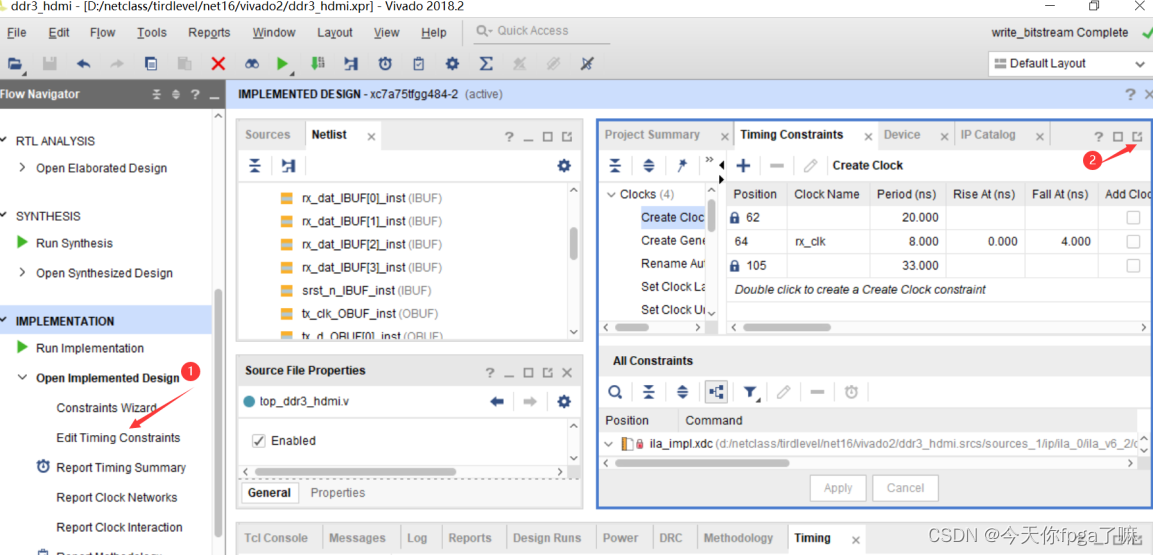

二、基准时钟的约束

1.完成综合(run implementation)

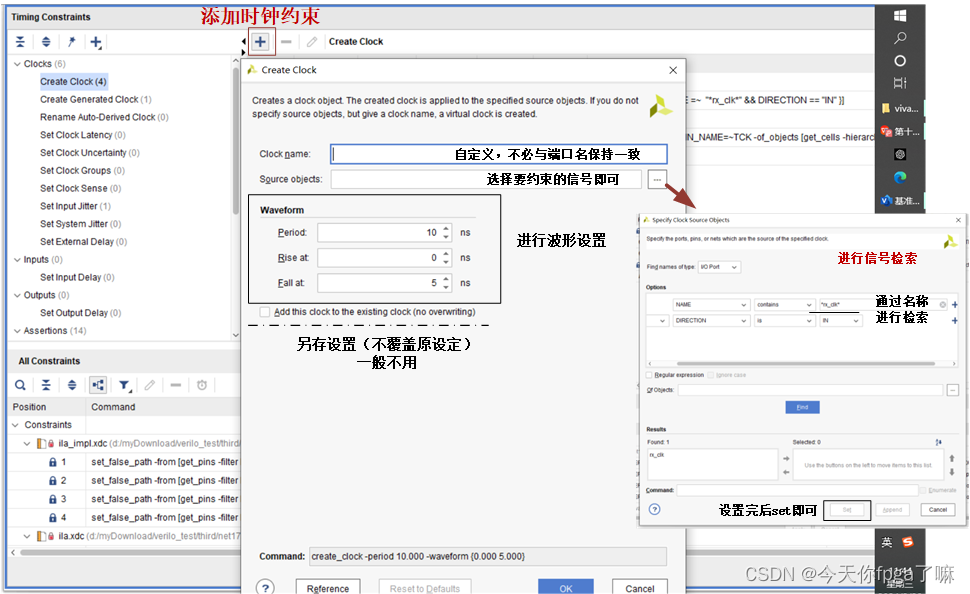

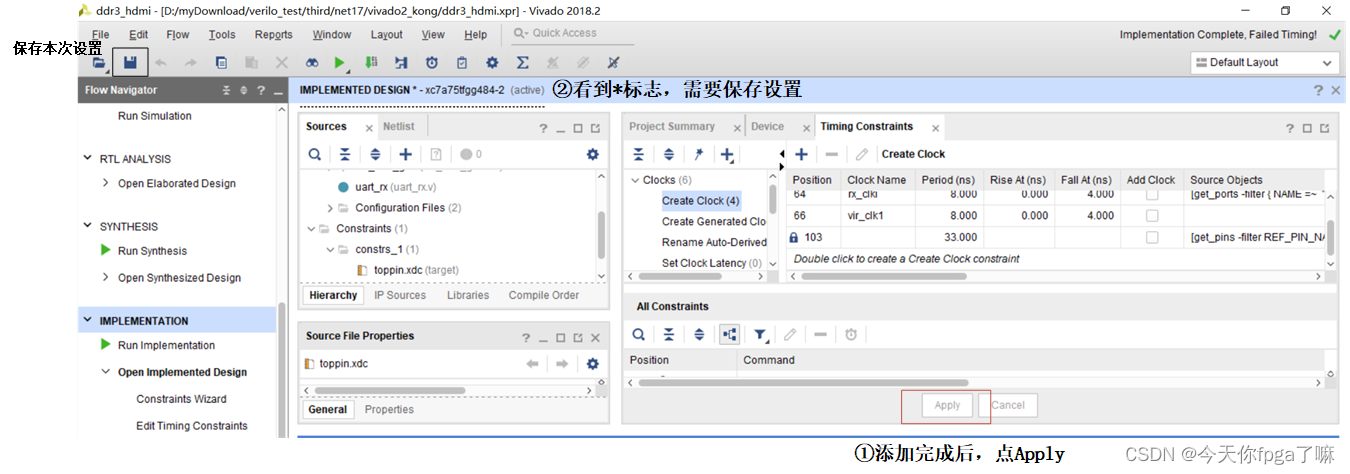

2.进行基准时钟约束(edit timing constrains)

① 在creat clock选项下添加基准时钟(rx_clki),并进行具体参数设置

② 查看时钟添加情况

具体信息如下:

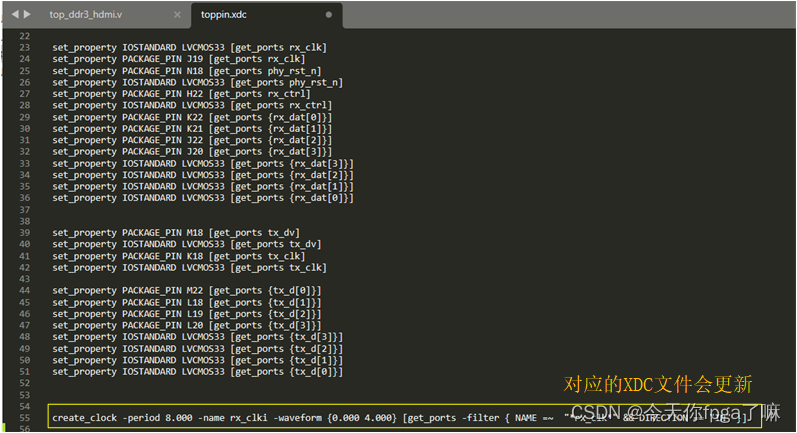

③ 保存本次设置,并自动更新到xdc文件中

约束了基准时钟之后,关于这个时钟的时序分析结果就有了。

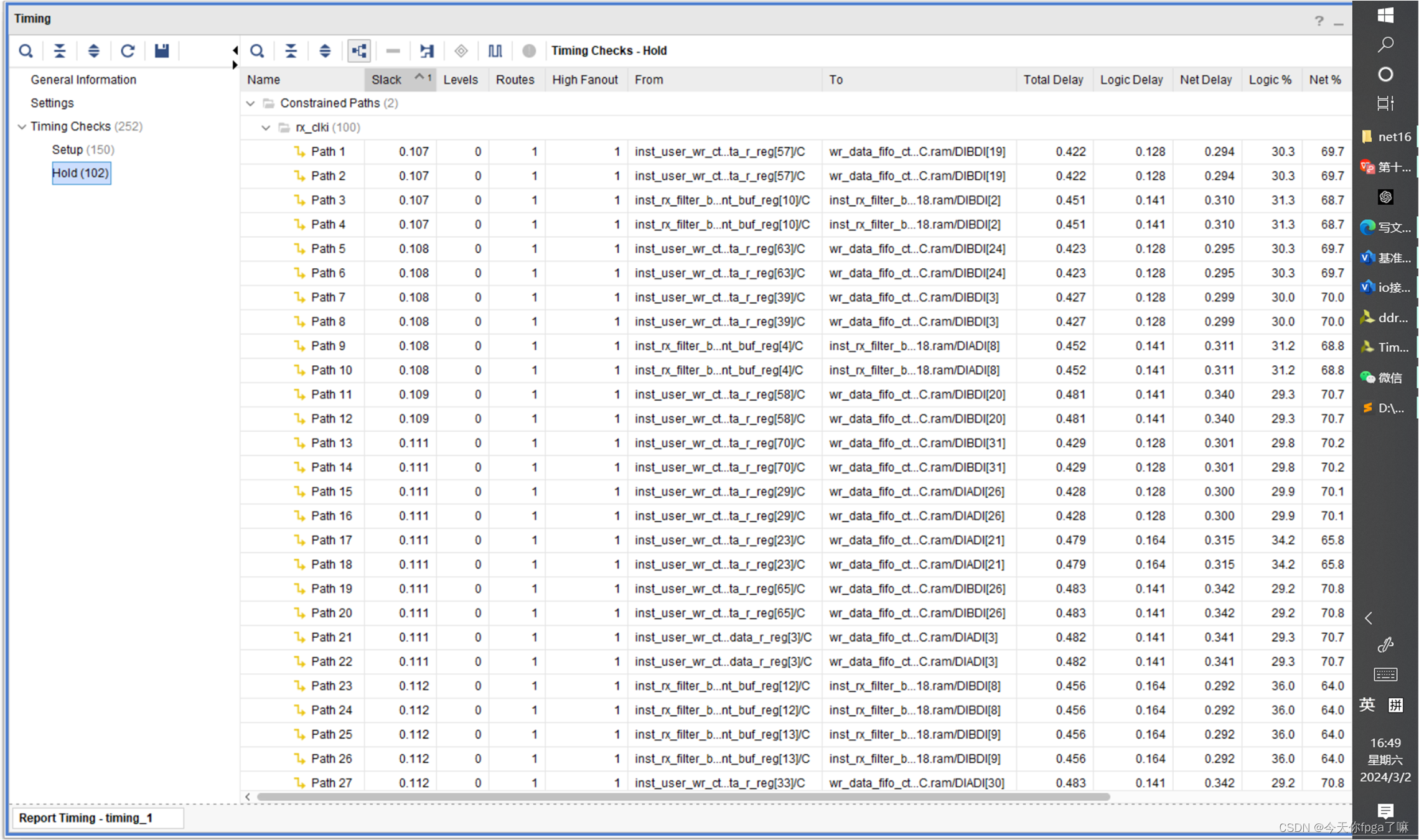

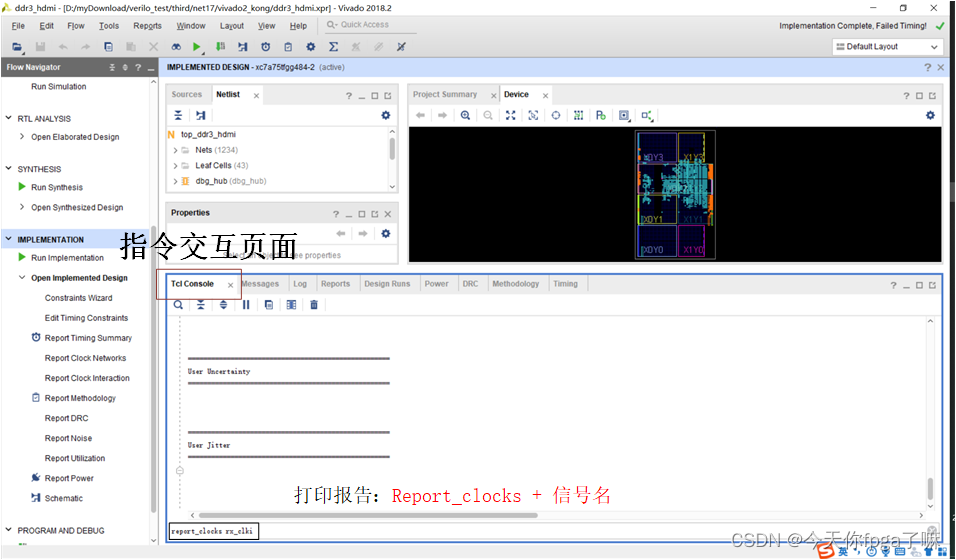

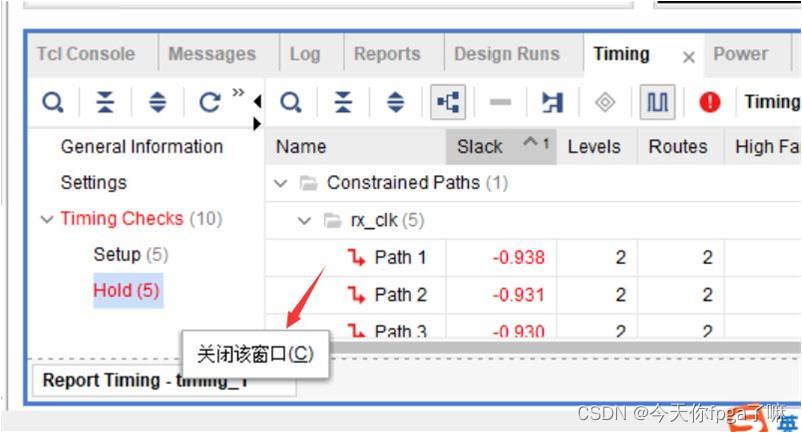

三、查看时序约束的结果

① 关闭当前时序信息

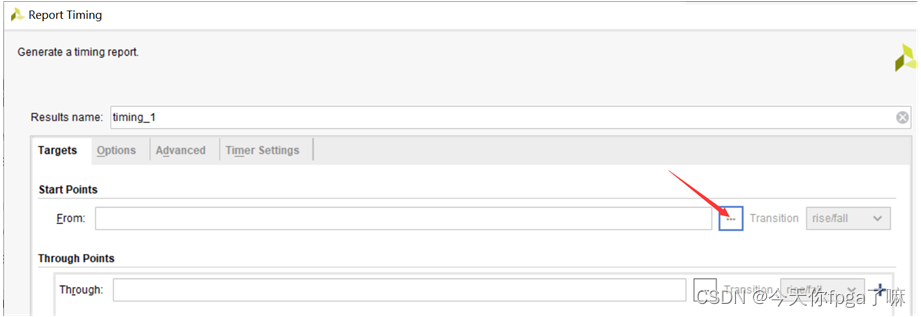

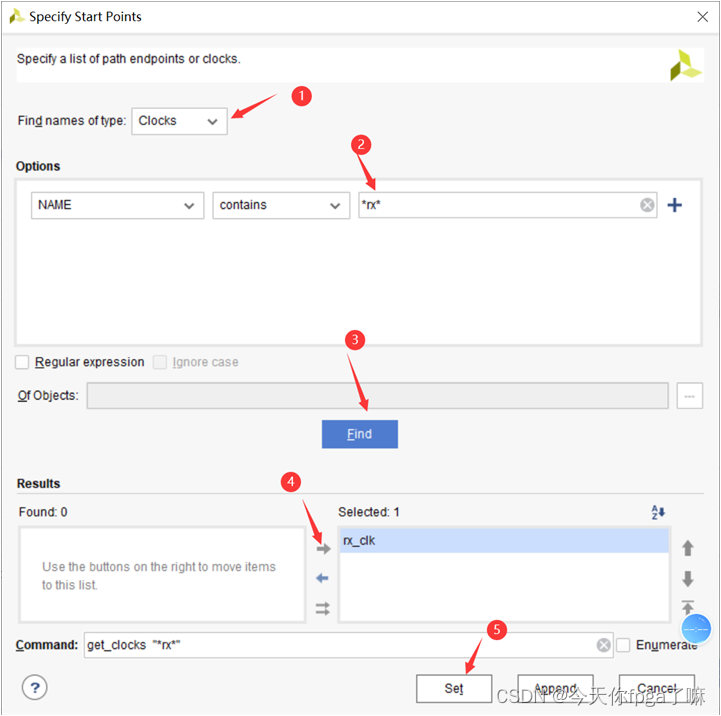

② 点击report timing,并设置打印时序报告参数

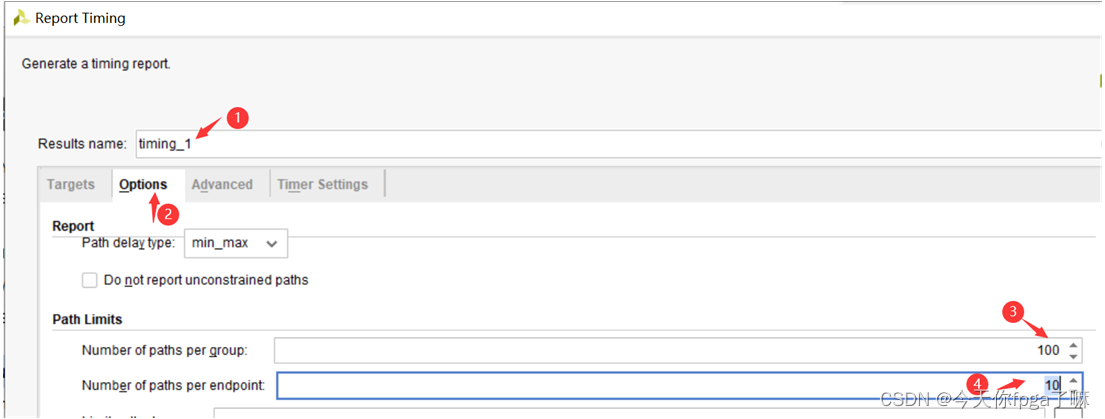

设置 option 中的观察时序路径条数和每个路径打印多少条信息,然后点击 OK 完成打印

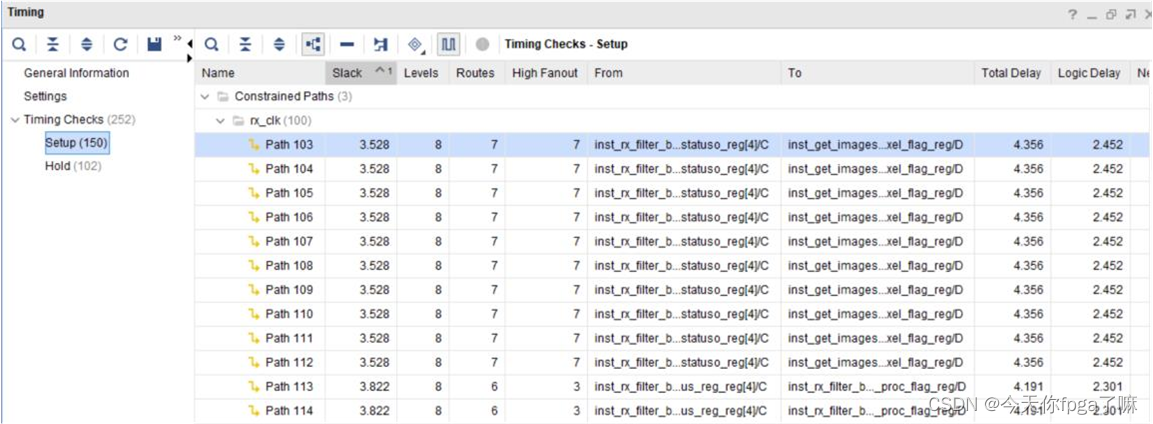

③ 报告信息如下(没有出现红色说明都是时序满足建立时间要求的)

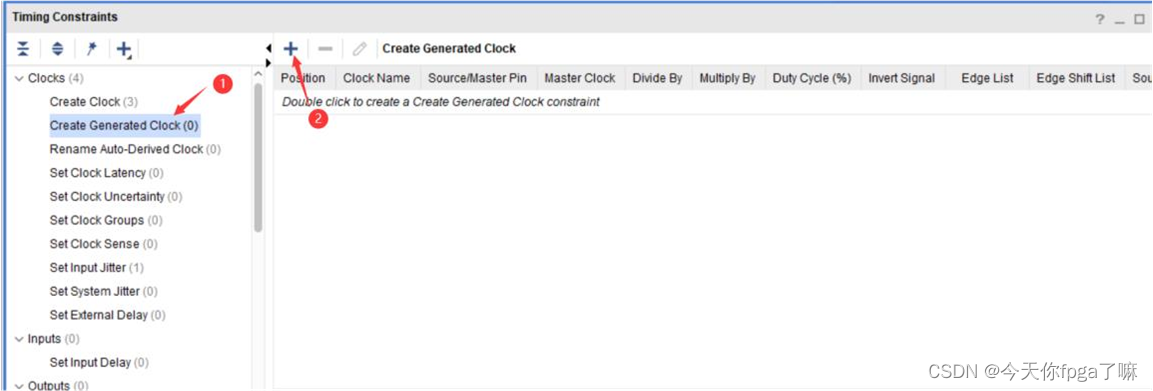

四、生成时钟约束

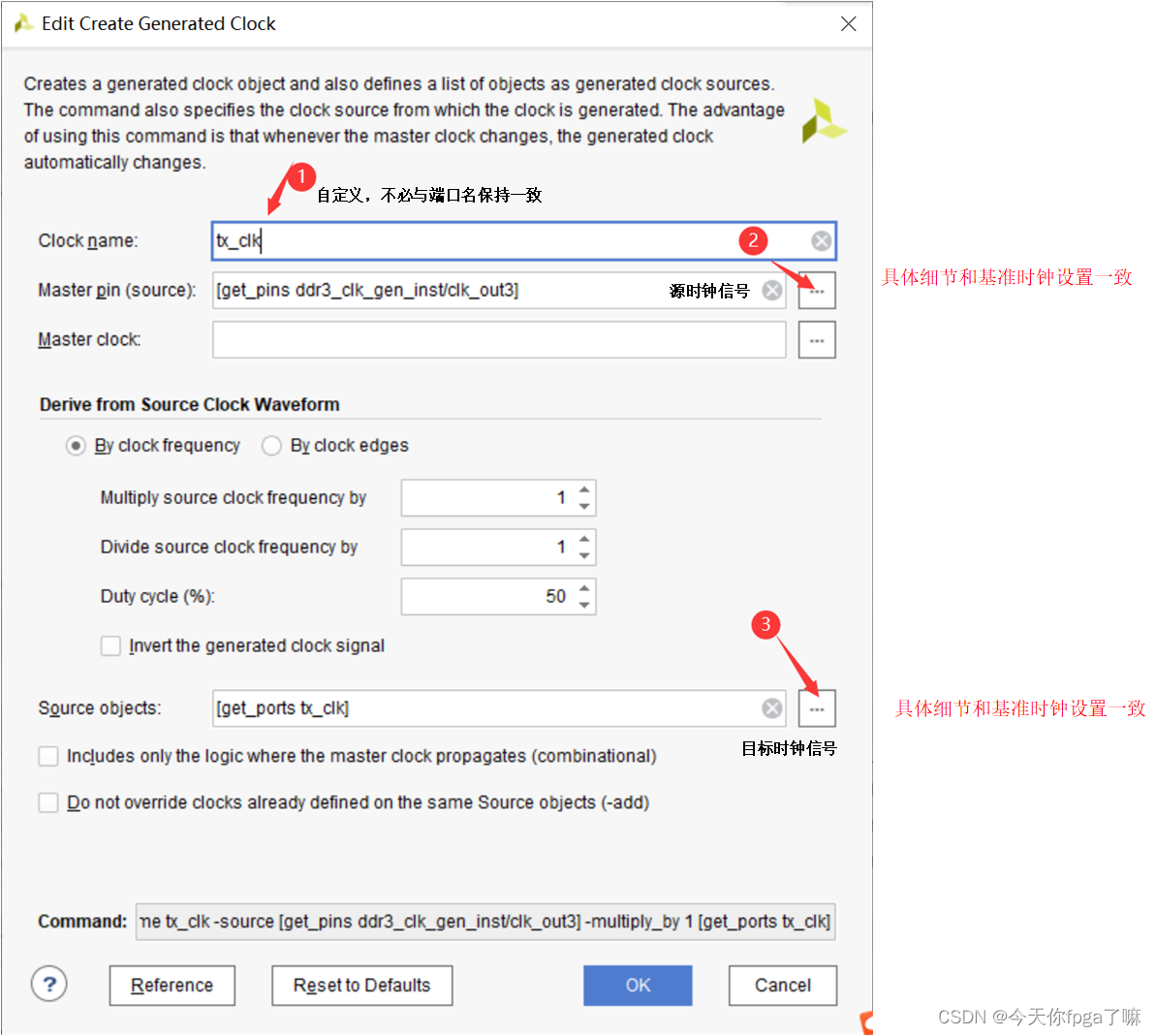

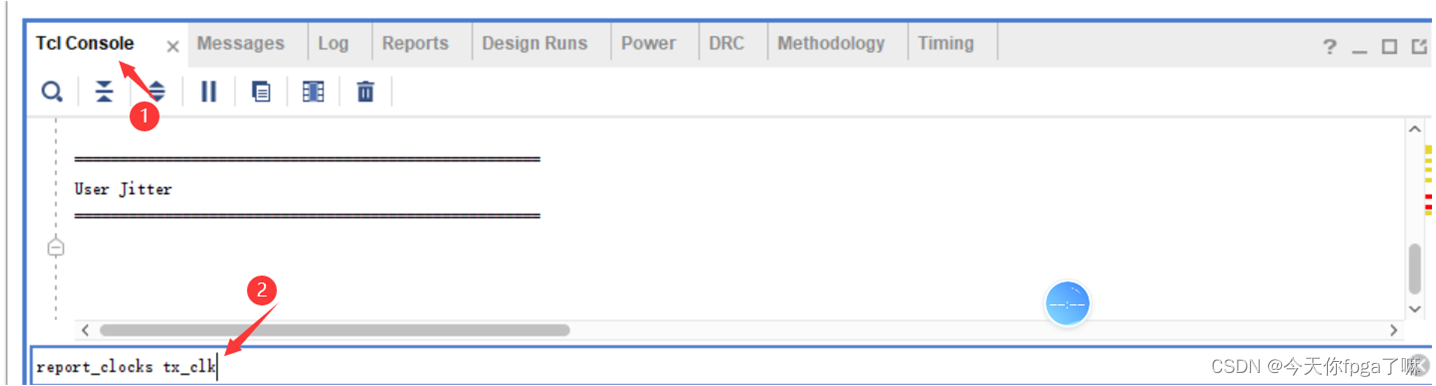

① 在create generated clock选项下添加生成时钟(源时钟:clk_out3,目标时钟:tx_clk),并进行具体参数设置

② 查看时钟添加情况并保存(此步骤和生成时钟步骤一样)

五、虚拟时钟约束

本次案例并没有用到,一般会在系统同步中使用(该技术目前被淘汰了,了解即可)

什么是虚拟时钟?

答:就是在 fpga 内部不存在的时钟,这个时钟主要来辅助做一些分析,比如系统同步时晶振这个时钟给源端的时钟;

创建虚拟时钟的方法很简单,就是创建一个时钟但是不实际指向一个 fpga 内部或者 IO 上的对象。

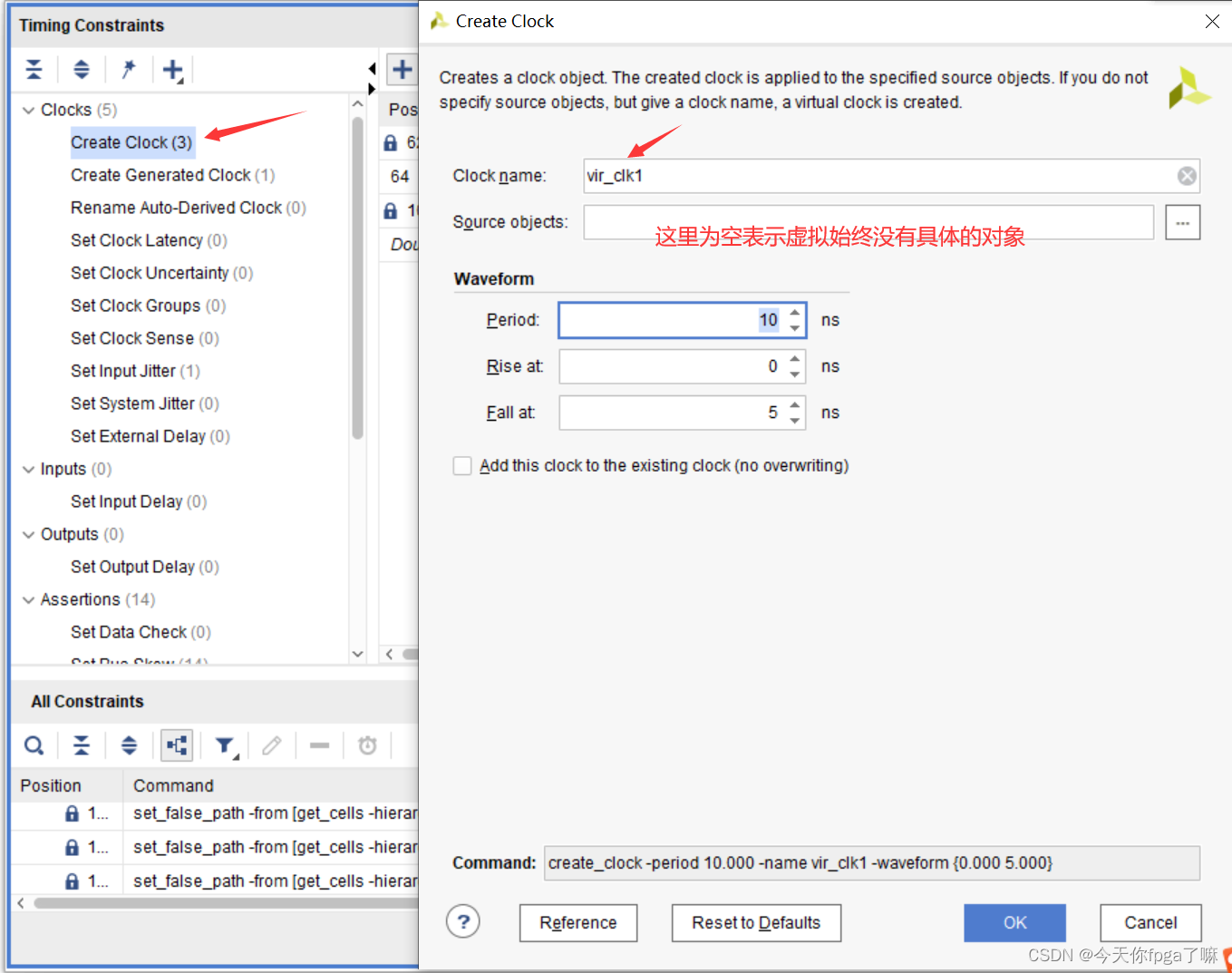

①在 create clock 中添加一个虚拟时钟(vir_clk1)

② 查看时钟添加情况并保存(此步骤和生成时钟步骤一样)

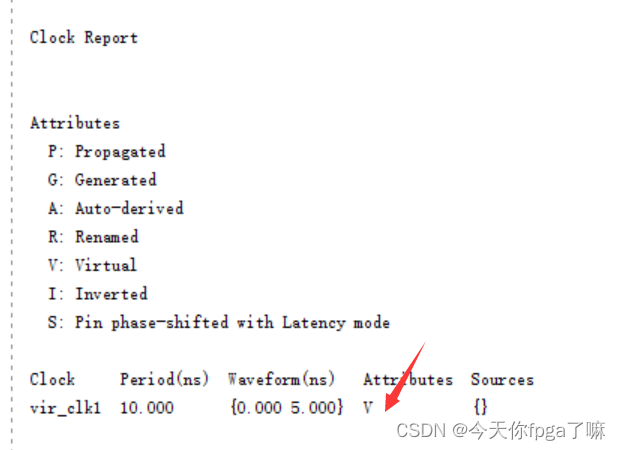

打印信息如下:

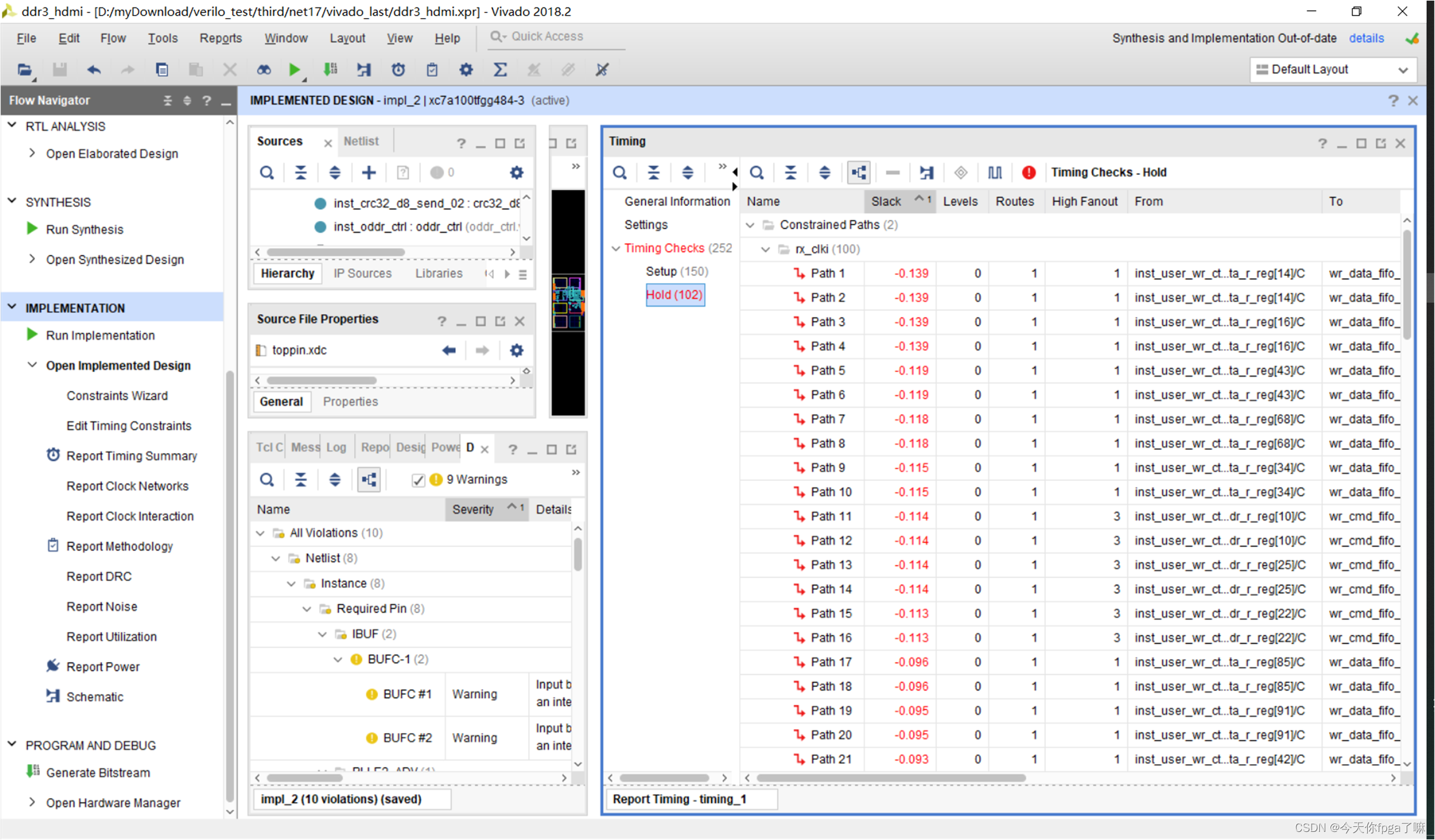

六、时序约束前后的时序报告:

时序约束前:

时序约束后: