- 1Python 读取PDF、Word文档_python 读取pdf 和word

- 2好用的IDEA插件之Git Commit Template_idea git commit template

- 3Web开发进化史!

- 4wireshark-协议分析【初见】(NBNS协议,SSDP协议、IGMPv2)

- 5python3开发-AI智能联系人管理系统_.python3开发-ai智能联系人管理系统

- 6基于YOLOv7算法的高精度实时水上漂浮物目标检测识别系统(PyTorch+Pyside6+YOLOv7)_yolo水论文

- 7Git上传文件不能超过100M 解决方案_git上传文件大小限制

- 8使用git reset --hard 命令后,怎么再恢复你的数据_add git reset --hard head~1 怎么恢复

- 9Android开发——SQLite数据库(二)android studio创建数据库,进行插入、删除、更新、查询操作_android studio mdatabase.delete

- 10完善我的大津法代码:#include

#include #include #define MAX_GRAY_LEVEL 256 // 图...

Aurora 和 ChipToChip IP(二)_chip to chip

赞

踩

摘要:对chiptochip的ip 核进行介绍,对IP进行仿真,仿真里面也带了Aurora。写的不一定全对,自行斟酌。

2.ChipToChip

我在使用chiptochip时,IP是这样设置的。

这里需要注意的是,我在使用chiptochip的同时,也需要用到的phy type是AURORA6466B,而不是selectIO,因为我需要用高速serdes进行一些数据传输。所以后文也是根据chiptochip+Aurora进行介绍。

master chiptochip与slave chiptochip的配置需要是一样的。

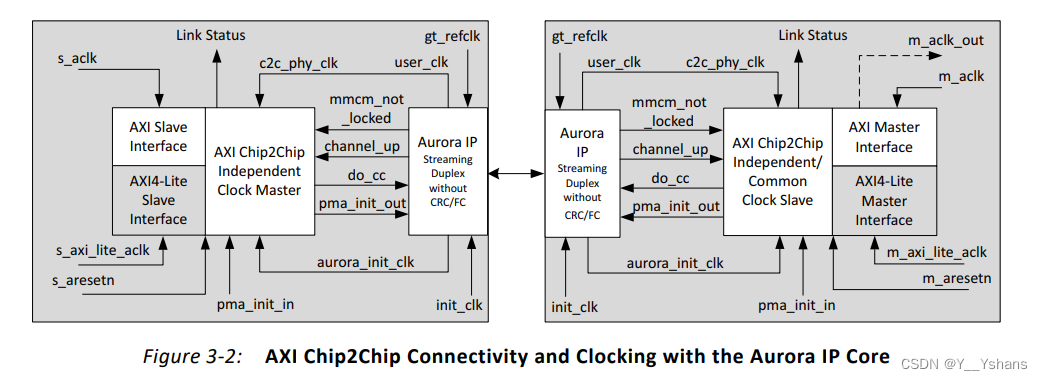

2.1 ChipToChip的框图

这个是chiptochip与Aurora的连接图。

实际工程的实现和仿真不太相同,不同点在于gt_transceiver有没有被剥离出来。在做仿真的时候gt_transceiver是被剥离出来的。相同点在于ip的接口是基本保持一致的。

Chip2chip:

我认为红框内的信号是chip2chip比较关注的信号。其余的axi4的信号不用关注,只用关注axi-lite信号。该信号组用于传输控制信号。

| 信号 | 描述 |

| axi_c2c_phy_clk_mas | 402.832031Mhz |

| t_axi_auro_channel_up_mas | Aurora给的link信号,Aurora不link,c2c也通不了 |

| t_axi_auro_tx_tready_mas t_axi_auro_tx_tdata_mas t_axi_auro_tx_tvalid_mas t_axi_auro_rx_tdata_mas t_axi_auro_rx_tvalid_mas | Aurora数据传输都用的axi-stream。这组信号用于传输控制信号,并且走的是aurora的lane4通道。这里需要注意的是aurora四个通道的ready和valid信号用的是同一个,真正后面开始传输数据的时候,需要注意。 |

| aurora_do_cc | 和aurora直连 |

| aurora_init_clk aurora_pma_init_in aurora_pma_init_out | 100Mhz |

| aurora_mmcm_not_locked_mas | 需要跟aurora连接。这里需要注意,aurora的gt剥不剥离出来会影响这个信号。所以我在有的地方对信号进行了取反。 |

| aurora_reset_pb | 和aurora直连 |

| t_axi_phy_error_out_mas | 表明两边IP配置有没有问题 |

| axi_lite | 传输控制数据 |

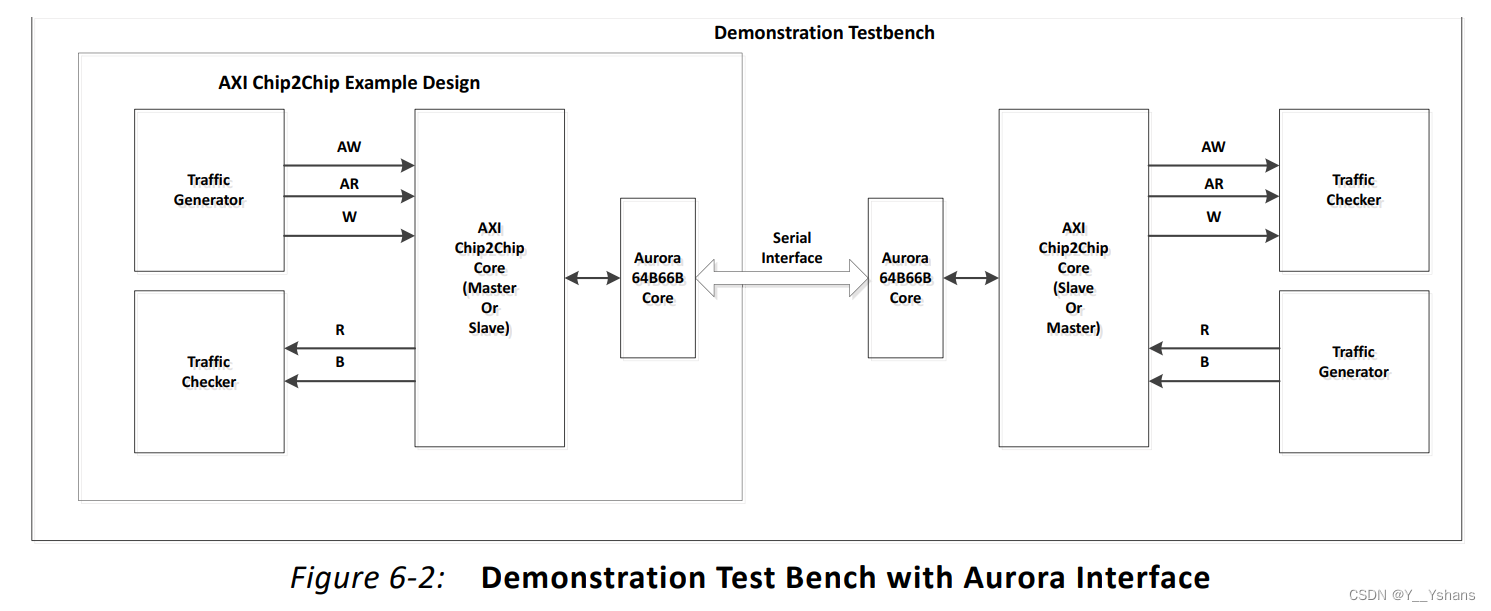

2.2 Testbench

Traffic generator模块的作用是产生data数据

Traffic checker模块的作用是对比接受的数据与产生的数据是否一致(产生数据的规则与generator模块一致)

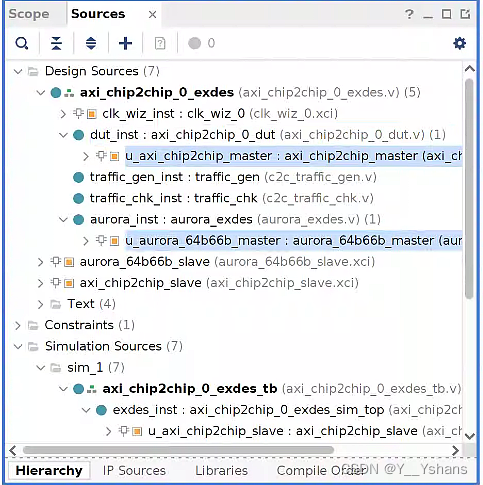

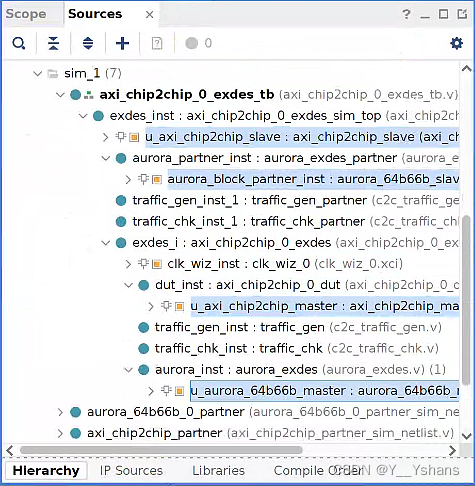

2.3 simulation

仿真需要注意一下,如果phy type设置成selectIO,直接用Xilinx example design仿真就行。但是选择了AURORA6466B,我发现仿真一直仿不出来,我将例子中的IP全部替换掉后(ip重新生成,verilog文件还是用xilinx提供的),才能正常仿真。

2.3.1 tb_top

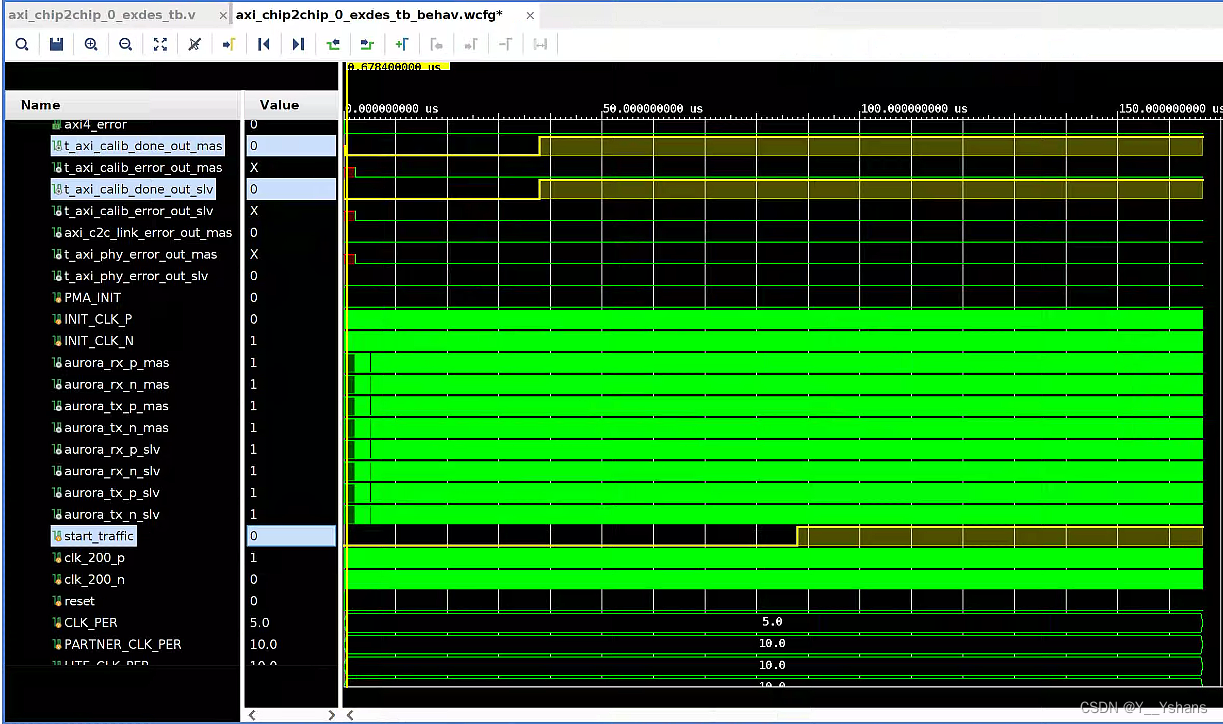

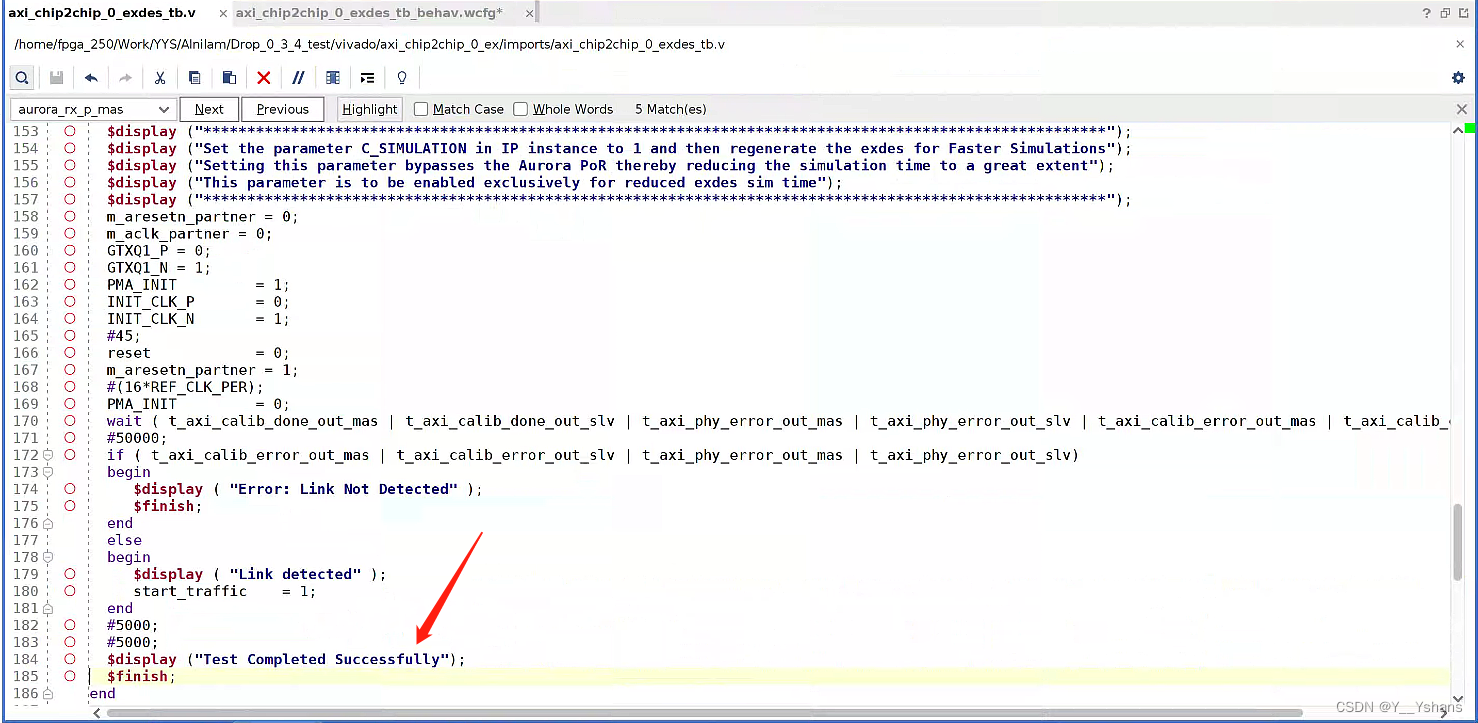

这是tb的顶层(axi_chip2chip_0_exdes_tb)仿真图。

当没有error信号,两个done信号拉高为1,start-traffic拉高为1,并且test successful & finish 之后,可以判定仿真基本是正确的。

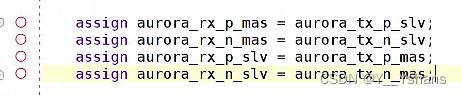

master part和slave part的rx tx分别连接,实现数据的传输。

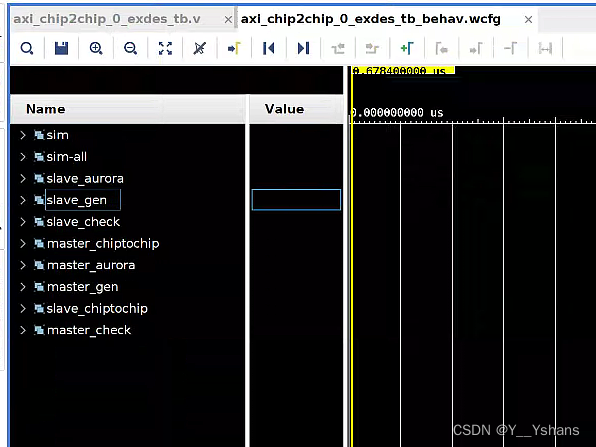

2.3.1 其它模块的仿真

我将整理好的工程上传至csdn。仿真都是用vivado自带的仿真。

总结

chiptochip并不是很难,一个模块一个模块分解着去看,还是比较容易理解。并且xilinx提供的gen模块和check模块都非常地好用(需要自己熟悉理解AXI),可以通用于以后的传输测试中。

https://download.csdn.net/download/Y__Yshans/86892336

4个Lane的Aurora仿真:

https://download.csdn.net/download/Y__Yshans/87484631

参考文章:

PG067-AXI Chip2Chip v5.0