热门标签

热门文章

- 1yolov5结果解析_background fp

- 2HarmonyOS 移动端开发指南:从零到入门,开发你的第一个应用_harmony os 4.0开发教程

- 3自然语言处理 Transformer 模型_transformer的mlp在哪

- 422K star的超强工具:Ollama,一条命令在本地跑 Llama2_启动ollama

- 5两篇论文被ECML PKDD DC09接收_ecml-pkdd(ccf b类)论文被哪里收集

- 6Ubuntu20.04双系统安装详解(内容详细,一文通关!)_ubuntu 20.04

- 7(5)Spring WebFlux快速上手——响应式Spring的道法术器_media_type="text/event-stream

- 8Linux离线安装Docker-Oracle_11g_docker离线环境安装oracle

- 9iOS-常见三种加密(MD5、非对称加密,对称加密)_ios sm3加密

- 10C语言怎么开辟超大内存?(malloc)_malloc申请大内存

当前位置: article > 正文

STM32使用FSMC与FPGA通信_stm32和fpga通过fsmc怎么通信的

作者:weixin_40725706 | 2024-04-08 10:29:45

赞

踩

stm32和fpga通过fsmc怎么通信的

ZYNQ中使用AXI总线进行PS与PL的交互很方便,STM32可以使用FSMC模拟AXI交互,实测效果还不错,只不过AXI总线可以直接交互32位数据,STM32的FSMC一般只有8/16位,我使用的是16位的。先对FSMC初始化

#include "fsmc.h" void FSMC_init(void) { GPIO_InitTypeDef GPIO_InitStructure; FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure; FSMC_NORSRAMTimingInitTypeDef readWriteTiming; //时钟使能 RCC_AHB3PeriphClockCmd(RCC_AHB3Periph_FSMC, ENABLE); RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOB | RCC_AHB1Periph_GPIOD | RCC_AHB1Periph_GPIOE | RCC_AHB1Periph_GPIOG, ENABLE); //IO初始化 GPIO_PinAFConfig(GPIOB, GPIO_PinSource7, GPIO_AF_FSMC); GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7; GPIO_Init(GPIOB, &GPIO_InitStructure); GPIO_PinAFConfig(GPIOD, GPIO_PinSource0, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource1, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource3, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource4, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource5, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource6, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource7, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource8, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource9, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource10, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource11, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource12, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource13, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource14, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOD, GPIO_PinSource15, GPIO_AF_FSMC); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_3 | GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_6 | GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 | GPIO_Pin_15; GPIO_Init(GPIOD, &GPIO_InitStructure); GPIO_PinAFConfig(GPIOE, GPIO_PinSource2 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource3 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource4 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource5 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource6 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource7 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource8 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource9 , GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource10, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource11, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource12, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource13, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource14, GPIO_AF_FSMC); GPIO_PinAFConfig(GPIOE, GPIO_PinSource15, GPIO_AF_FSMC); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2 | GPIO_Pin_3 | GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_6 | GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 | GPIO_Pin_15; GPIO_Init(GPIOE, &GPIO_InitStructure); GPIO_PinAFConfig(GPIOG, GPIO_PinSource13, GPIO_AF_FSMC); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13; GPIO_Init(GPIOG, &GPIO_InitStructure); //FSMC初始化 readWriteTiming.FSMC_AddressSetupTime = 1; readWriteTiming.FSMC_AddressHoldTime = 0; readWriteTiming.FSMC_DataSetupTime = 4; readWriteTiming.FSMC_BusTurnAroundDuration = 0; readWriteTiming.FSMC_CLKDivision = 0; readWriteTiming.FSMC_DataLatency = 0; readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1; FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Enable; FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM; FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b; FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable; FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable; FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low; FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable; FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState; FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable; FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable; FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable; FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable; FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming; FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming; FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure); //FSMC Bank1_SRAM1 Bank使能 FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE); }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

对应FPGA模块如下

module fsmc( ab, db, wrn, rdn, csn, PLL_100M, RST_n, nadv ); input [8:0]ab; inout [15:0]db; input wrn; input rdn; input csn; input PLL_100M; input RST_n; input nadv; wire rd; wire wr; assign rd = (csn | rdn); assign wr = (csn | wrn); wire [15:0]DB_OUT; assign db = !rd ? DB_OUT : 16'hzzzz; reg wr_clk1,wr_clk2; always @(posedge PLL_100M or negedge RST_n) begin if(!RST_n) begin wr_clk1 <= 1'd1; wr_clk2 <= 1'd1; end else {wr_clk2,wr_clk1} <= {wr_clk1,wr}; //提取写时钟 end reg rd_clk; always @(posedge PLL_100M or negedge RST_n) begin if(!RST_n) rd_clk <= 1'd1; else rd_clk <= rd; //提取读时钟 end wire clk = (!wr_clk2 | !rd); my_ram u1( //ram块例化 .address(ab), .clock(clk), .data(db), .wren(!wr), .rden(!rd), .q(DB_OUT), ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

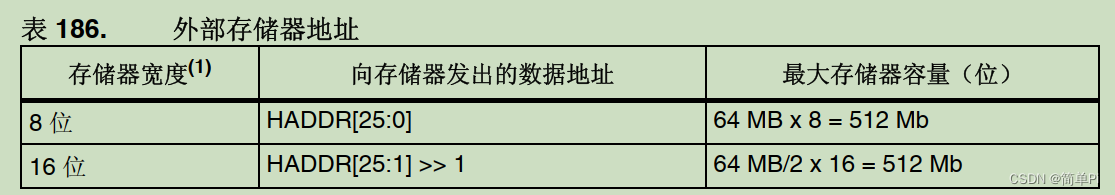

交互核心代码就一句话,但是需要注意的是在《STM32F4XX中文参考手册》中有说

因为使用的是16位数据宽度,总线内部会自动右移一位,所以我们多左移一位

#define FPGA_OFFSET_ADDR(reg) *((volatile unsigned short int *)(0x60000000 + ((reg) << 17)))

- 1

这句代码中的reg参数是与FPGA约定的寄存器地址,我们的数据是16位的,使用方法如下:

uint16_t id;

id = FPGA_OFFSET_ADDR(5); //从寄存器5读出数据放到变量id里面

FPGA_OFFSET_ADDR(6) = 0xAF14; //往寄存器6里面写入数据0xAF14

- 1

- 2

- 3

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/384820

推荐阅读

相关标签

![[蓝桥杯嵌入式]hal库 stm32 PWM的使用(随时修改占空比,随时修改频率)](https://img-blog.csdnimg.cn/direct/ee42de64b0f14932bd12cd666ec76ff4.png?x-oss-process=image/resize,m_fixed,h_300,image/format,png)