热门标签

热门文章

- 1【路径规划】(4) 蚁群算法,附python完整代码_蚁群算法旅行商问题python

- 2微信小程序,携带参数页面跳转_res.eventchannel.emit

- 3AE开发集锦_pixels.crd.co

- 4python创建画布的函数_Python如何在画布中绘制多个图表?

- 5如何在 Netlify 上手动部署 React 和 TypeScript 项目_netlify 部署配置

- 6硬核!10分钟教你搭建一个本地版GPT4.0!_gpt-4o 怎么本地布署

- 7python若干整数的最大值和最小值,整数的最大值和最小值

- 8使用docker时报Error response from daemon: driver failed programming external connectivity on endpoint_docker: error response from daemon: driver failed

- 9机器人非线性系统反馈线性化与解耦_机器人非线性补偿解耦控制器(非线性模型的线性化控制)设 计原理及控制框图

- 10vue使用video.js_cj video

当前位置: article > 正文

Xilinx Spartant6 DDR3 IP核的创建_ddr3 memory address map

作者:weixin_40725706 | 2024-05-24 04:58:35

赞

踩

ddr3 memory address map

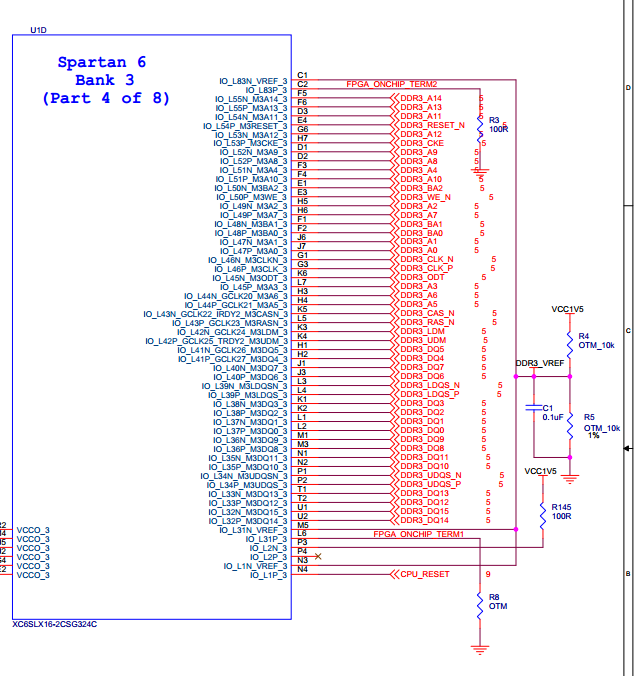

新建一个ISE工程,然后创建一个Ip核。

选择MIG Virtex-6的ip,双击。

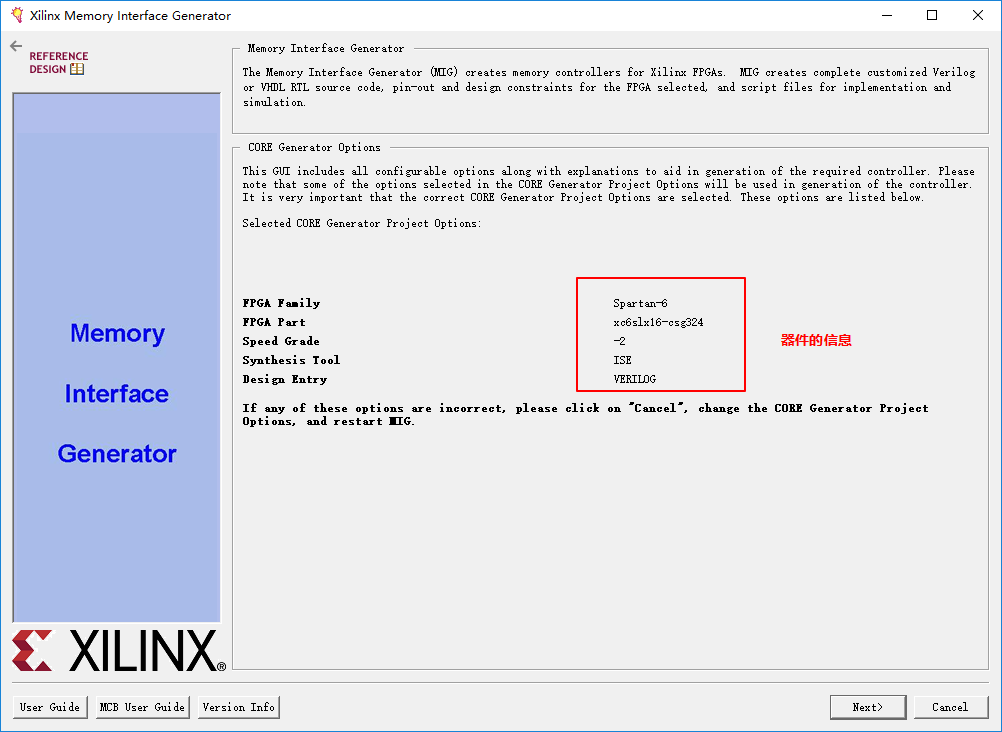

1.双击打开IP核设置的界面。

点击next

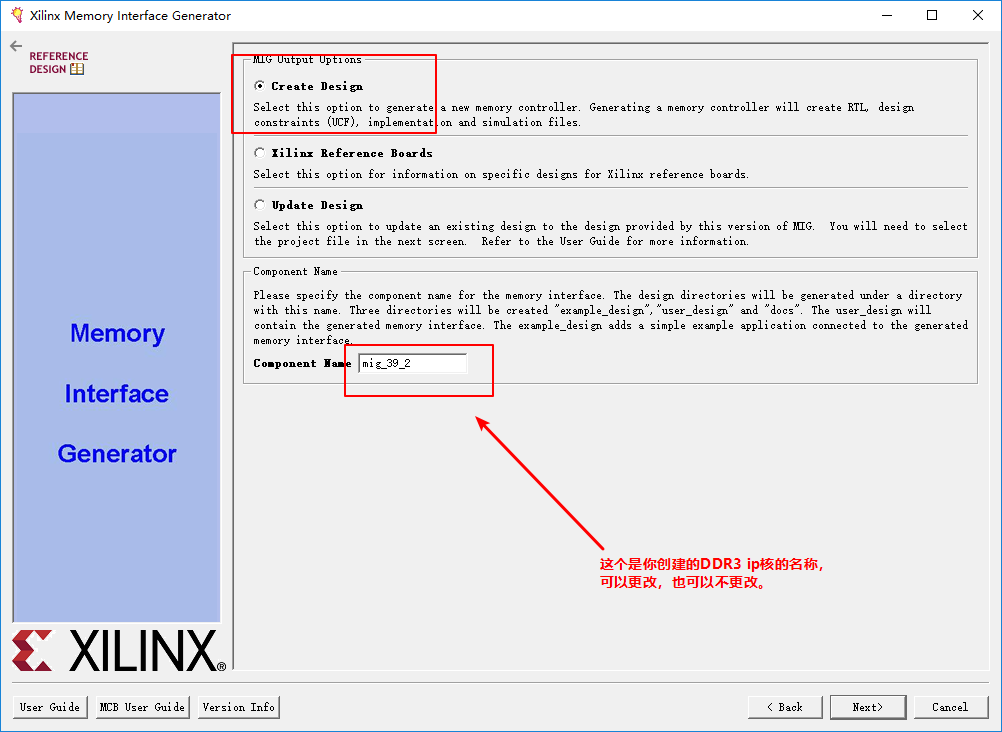

2.第二个界面

然后点击next

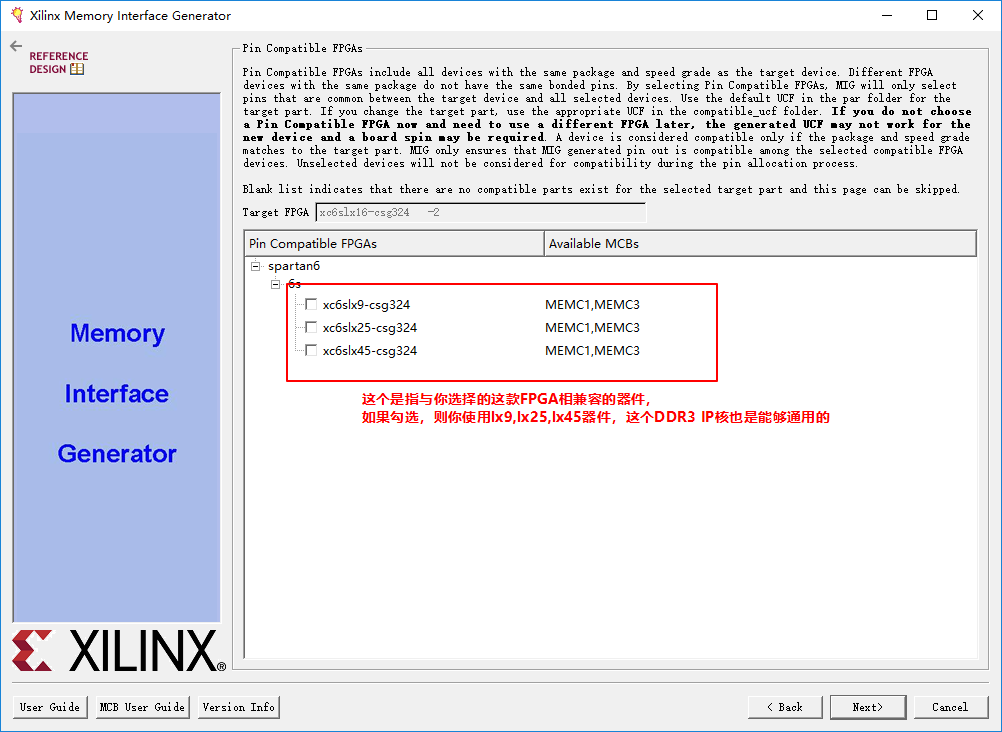

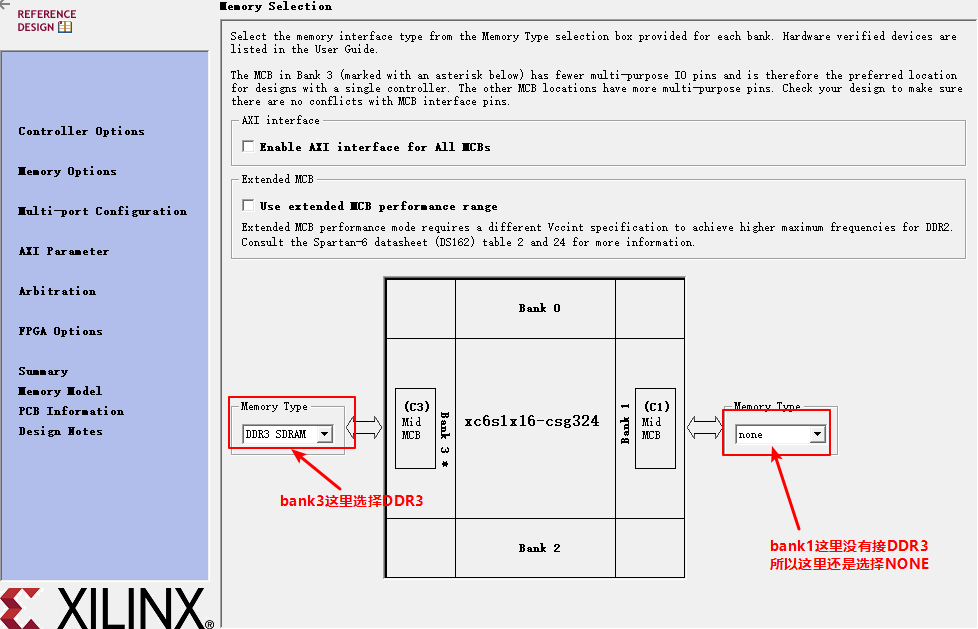

3.第三个界面

我们这里不勾选,直接next

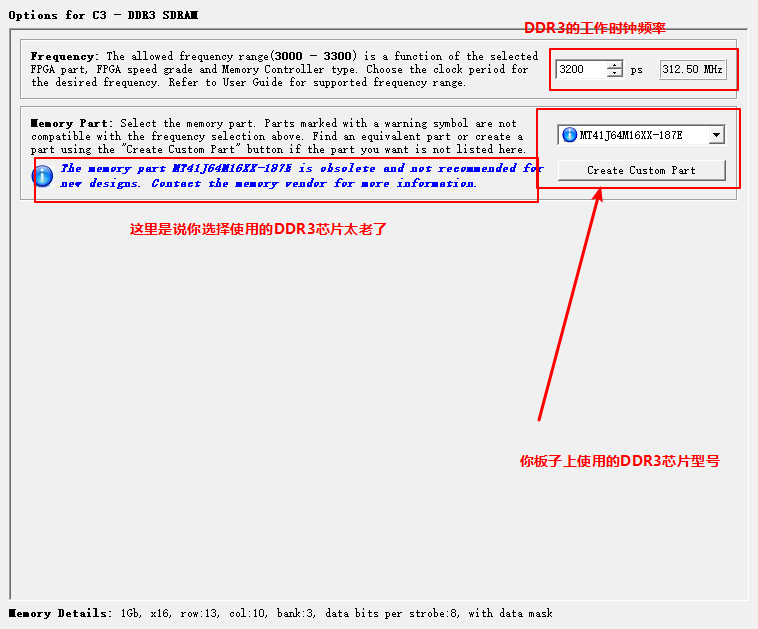

5.选择DDR3时钟的工作频率

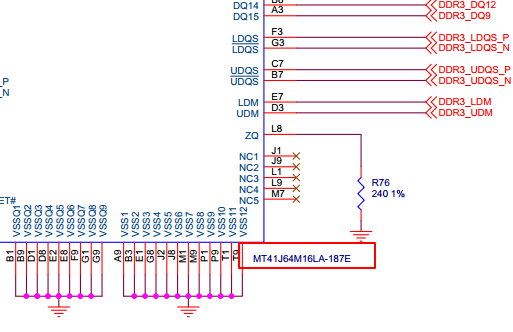

开发板上的DDR3芯片MT41J64M16LA-187E对应上就行。

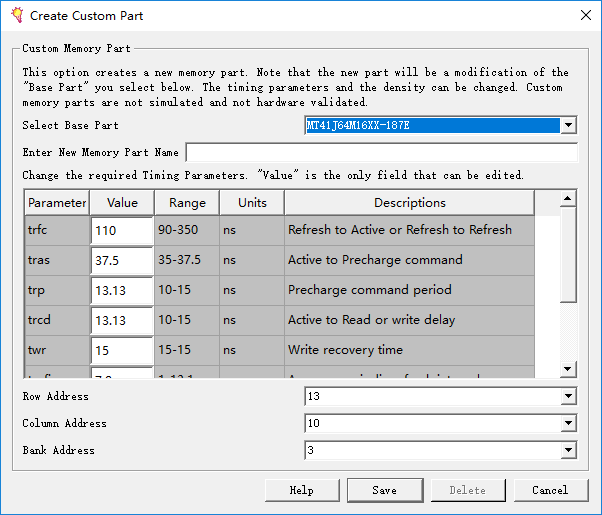

如果你板子上的DDR3芯片型号没有,那么先选择与你板子上DDR3最相近的信号,然后点击Creat custom part

看你DDR3芯片手册,将这些时序参数写进去。

填好之后,继续点击NEXT。

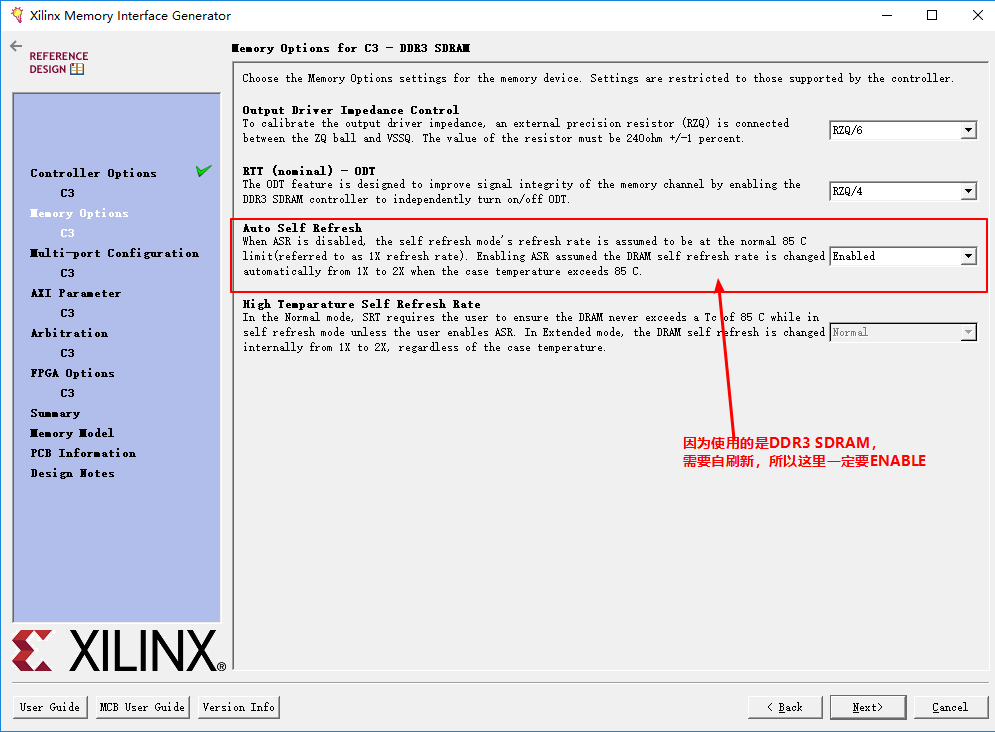

6.memory options 设置,什么都不用变,直接next

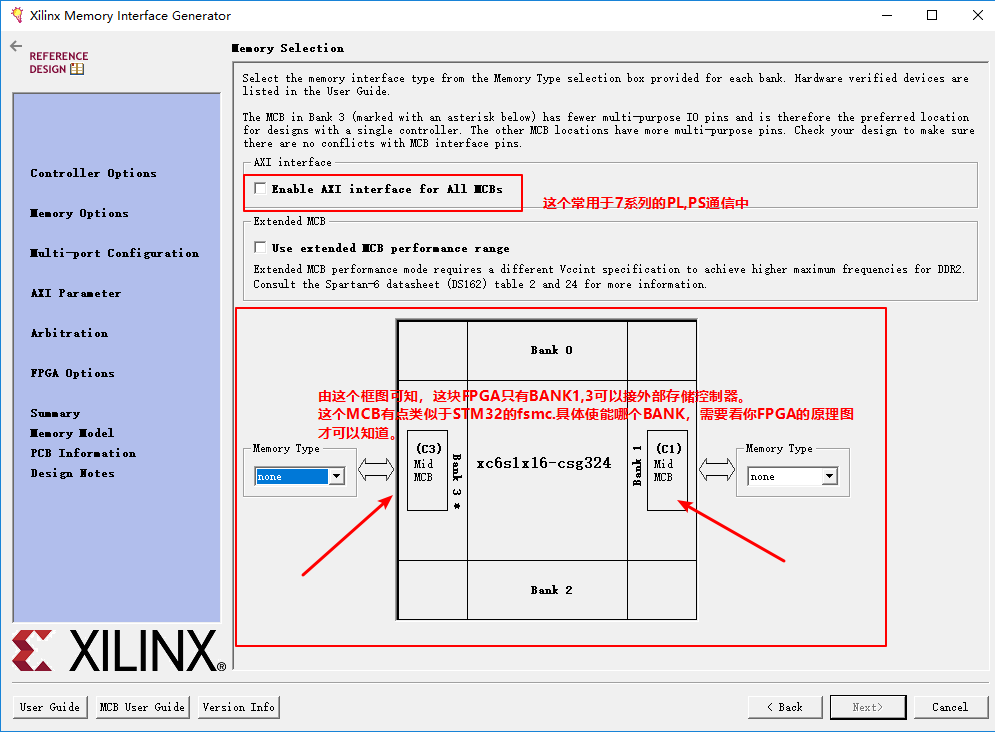

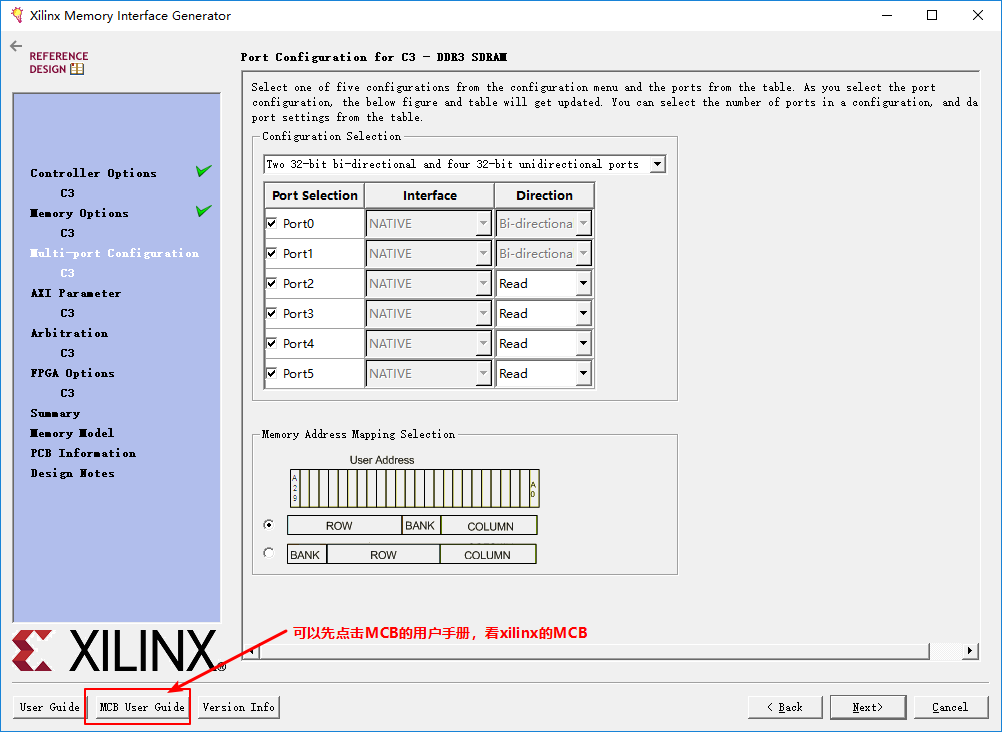

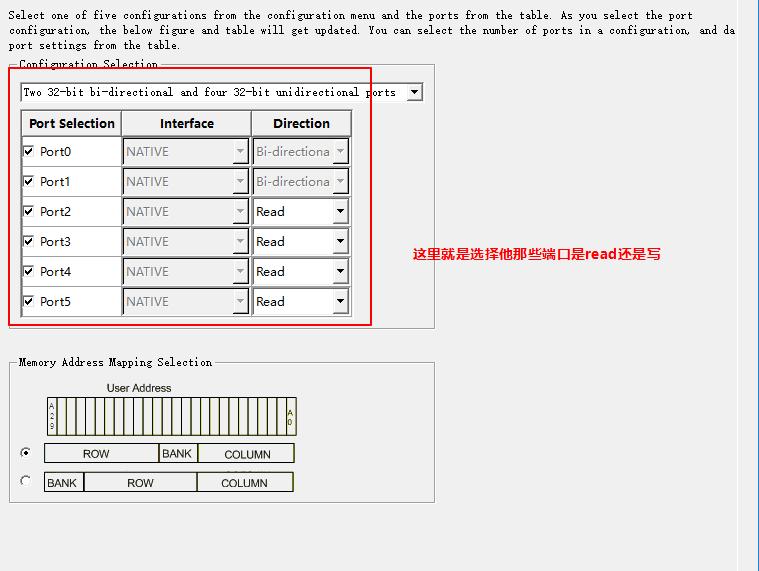

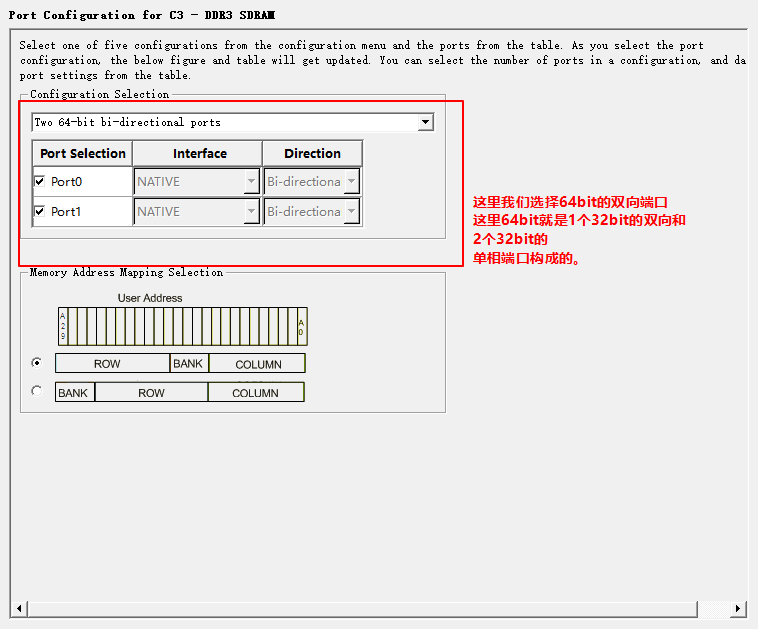

7.选择Memory port的方式。

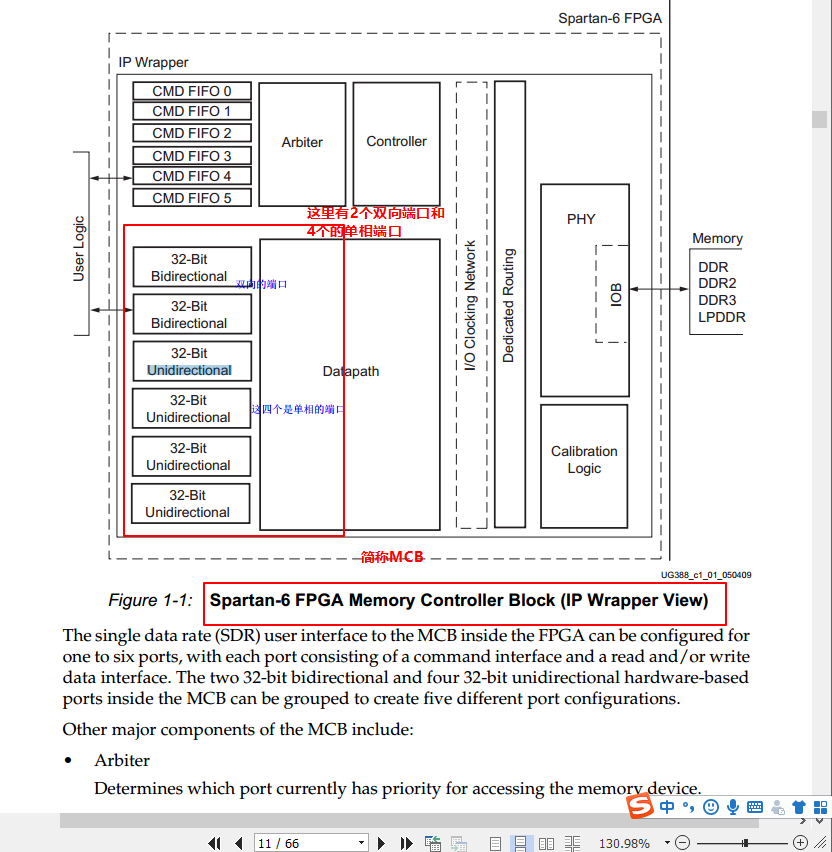

先打开MCB的用户手册

MCB的全称: Memory Controller Block

他有2个32bit双向的端口和4个32bit单相的端口组成。

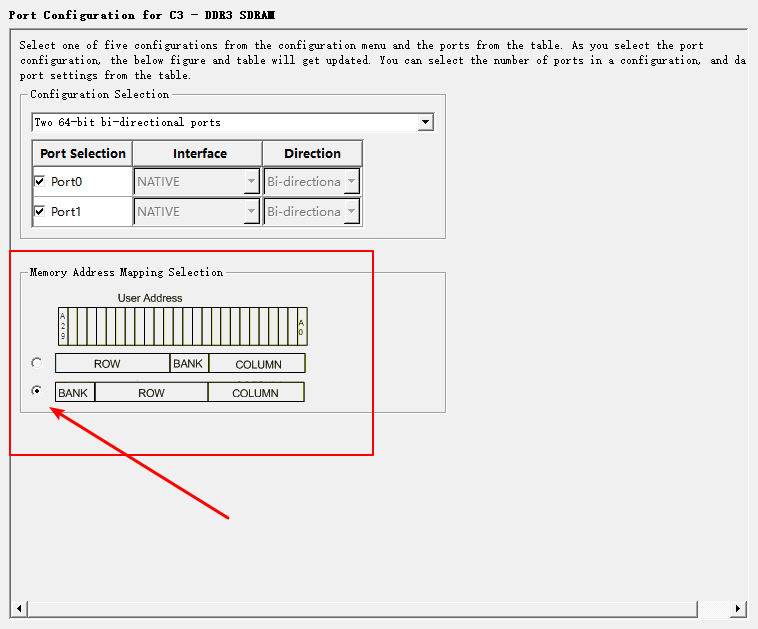

Memory Address mapping selection这里我们选择

bank row col这种形式。![]()

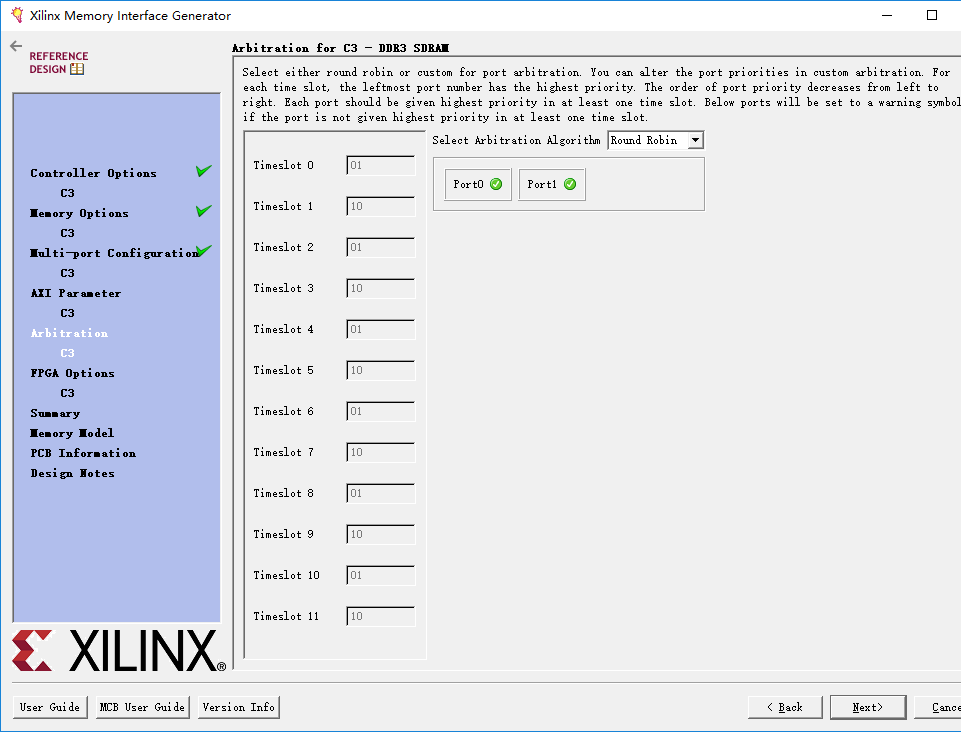

8.优先级的设置

因为我们前面有设置到我们使用了两个64bit的端口,这两个端口是可以同时进行读写的,但是DDR3芯片,一个时间只能读或者写,所以这里就需要有个优先级。

我们这里保持默认,直接点击next.

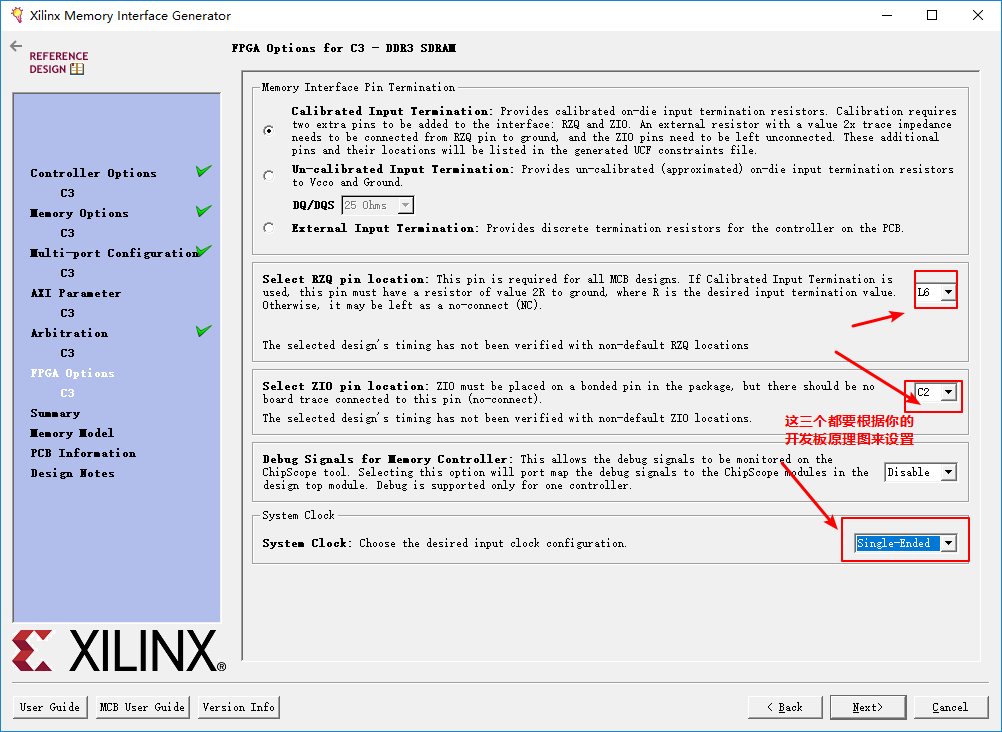

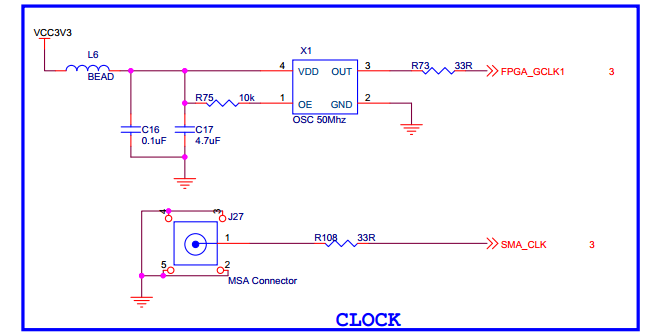

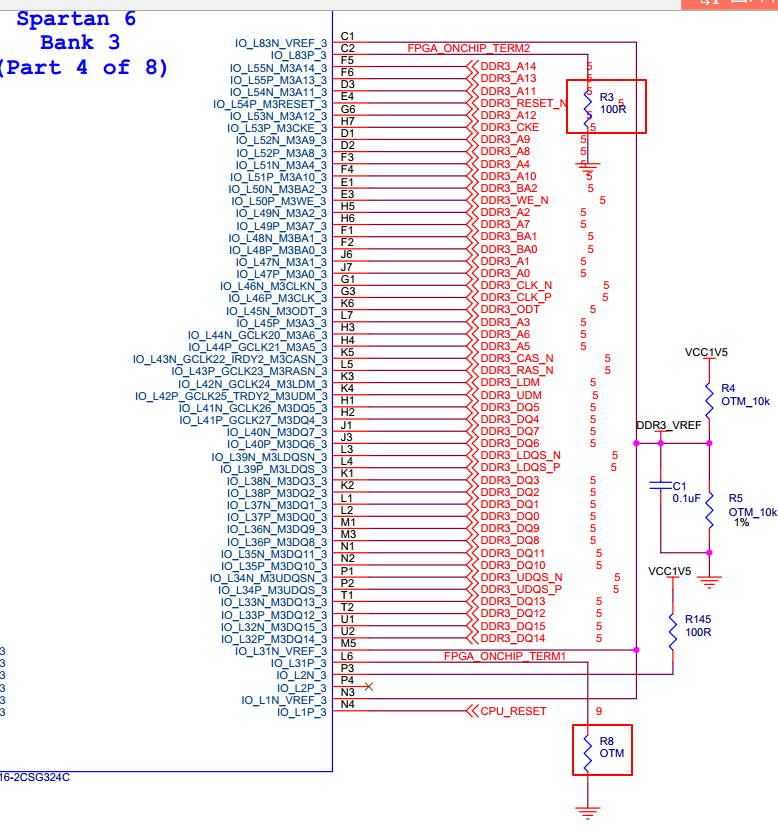

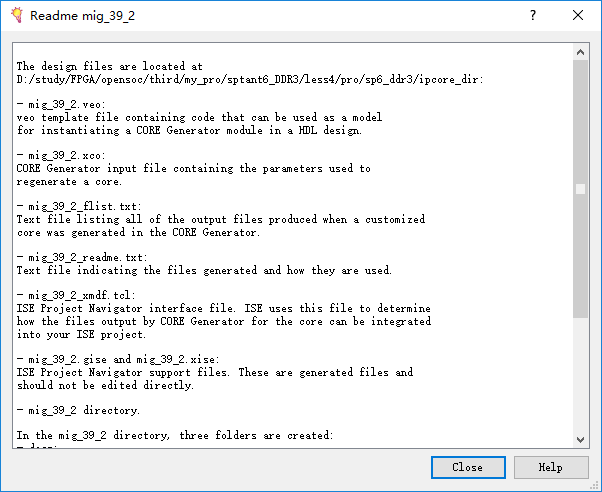

10.之后的设置一路next就行。最后生成的信息

点击close.

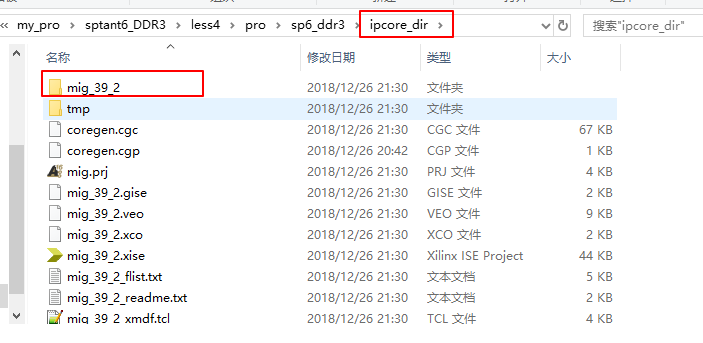

生成后再工程目录下的IP核目录下面![]()

有mig_39_2这个文件夹。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/615922

推荐阅读

相关标签