热门标签

热门文章

- 1Elasticsearch索引数据的路由规则与自定义路由分发_elasticsearch 自定义路由

- 2VScode远程开发Linux C/C++程序

- 3Spring RabbitMQ 源码分析_parameter 1 of method simplerabbitlistenercontaine

- 4图解mysql(六)——内存篇_mysql内存使用详解

- 5rocketmq面对消息积压的处理_rocketmq消息堆积解决方案

- 6计算机毕业论文答辩教师评语,毕业论文答辩指导老师评语参考

- 7ICLR上新 | 强化学习、扩散模型、多模态语言模型,你想了解的前沿方向进展全都有_整体趋势扩散学习

- 8Elasticsearch 认证模拟题 - 9

- 9【Unity 3D 从入门到实战】Unity 3D 组件总结_unity所有组件

- 10Hive的面试题总结_hive调优面试题

当前位置: article > 正文

基于FPGA的DDS任意波形发生器设计_fpga开发板上实现一个简易的任意波形发生器。该波形发生器能够产生正弦波、方波、

作者:weixin_40725706 | 2024-06-15 23:03:57

赞

踩

fpga开发板上实现一个简易的任意波形发生器。该波形发生器能够产生正弦波、方波、

一、简介

DDS技术最初是作为频率合成技术提出的,由于其易于控制,相位连续,输出频率稳定度高,分辨率高, 频率转换速度快等优点,现在被广泛应用于任意波形发生器(AWG)。基于DDS技术的任意波形发生器用高速存储器作为查找表,通过高速D/A转换器来合成出存储在存储器内的波形。所以它不仅能产生正弦、余弦、方波、三角波和锯齿波等常见波形,而且还可以利用各种编辑手段,产生传统函数发生器所不能产生的真正意义上的任意波形。

二、原理

根据傅立叶变换定理可知,任何周期信号都可以分解为一系列正弦或余弦信号之和,不失一般性,以正弦信号的产生为例详细说明直接数字频率合成技术的原理。比如一个频率为fc的正弦信号,其时域表达式为:

![]()

其相位表达式为:

![]()

从两式可以看出,正弦信号是关于相位的一个周期函数,下图更加直观的描述相位与幅度的关系,16个相位与16个幅度值相对应,即每一个相位值对应一个幅度值,比如1100对应的相位为3π/2,对应的幅度值为-1.

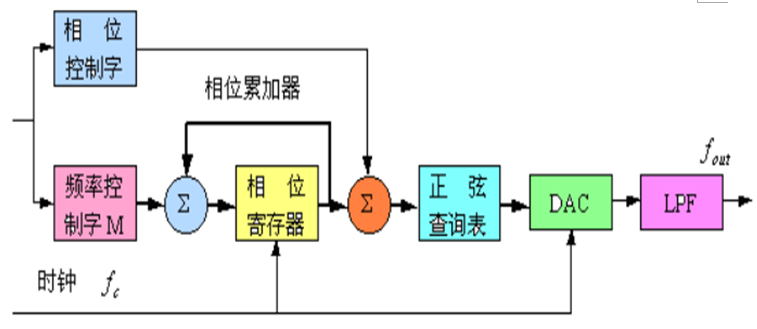

相位和幅值的一一对应关系就好比存储器中地址和存储内容的关系,如果把一个周期内每个相位对应的幅度值存入存储器当中,那么对于任意频率的正弦信号,在任意时刻,只要已知相位Φ(t),也就知道地址,就可通过查表得到s(t)。下图是DDS的基本结构框图:

由于相位累加器字长的限制,相位累加器累加到一定值后,其输出将会溢出,这样波形存储器的地址就会循环一次,即意味着输出波形循环一周。故改变频率控制字即相位增量,就可以改变相位累加器的溢出时间,在时钟频率不变的条件下就可以改变输出频率。改变查表寻址的时钟频率,同样也可以改变输出波形的频率。

为了获得较高的频率分辨率,则只有增加相位累加器的字长N,故一般N都取值较大。但是受存储器容量的限制,存储器地址线的位数w不可能很大,一般都要小于N。这样存储器的地址线一般都只能接在相位累加器输出的高w位,而相位累加器输出余下的(N-W)个低位则只能被舍弃,这就是相位截断误差的来源。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/724168

推荐阅读

相关标签