Vivado 入门 —— HLS HelloWorld 流水灯(二)—— 调用 IP 与上板验证

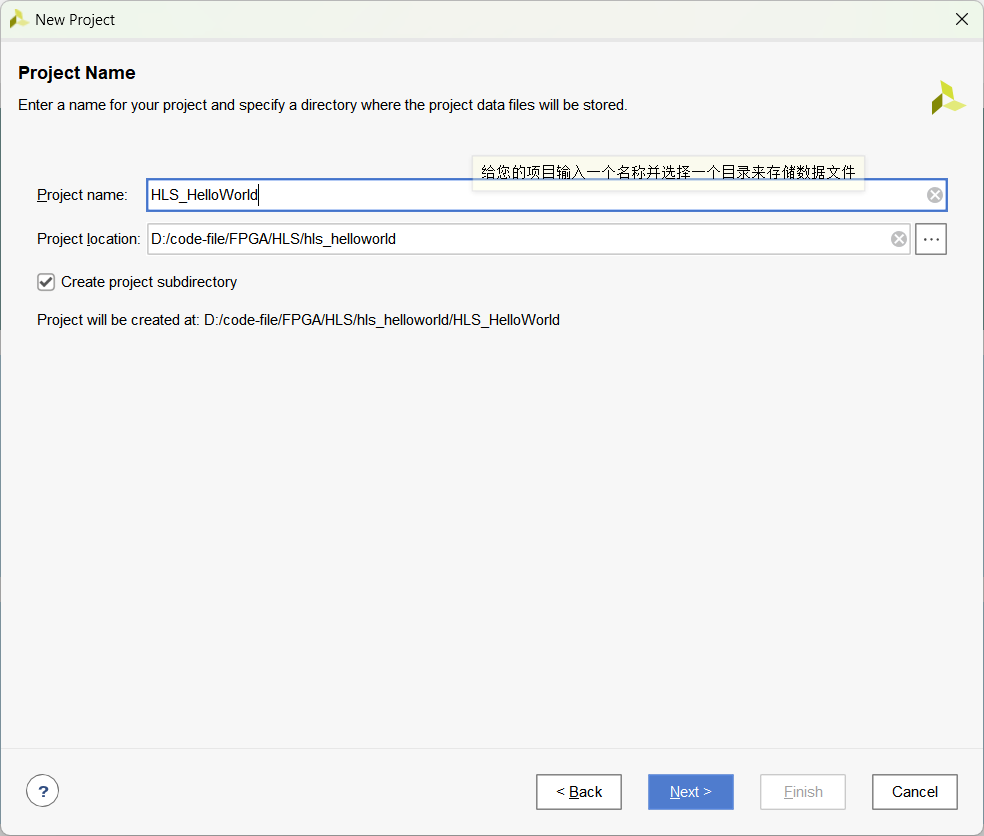

Vivado 新建项目

这里和使用 Vivado HLS 一样,要注意顶层名称与设置的一致

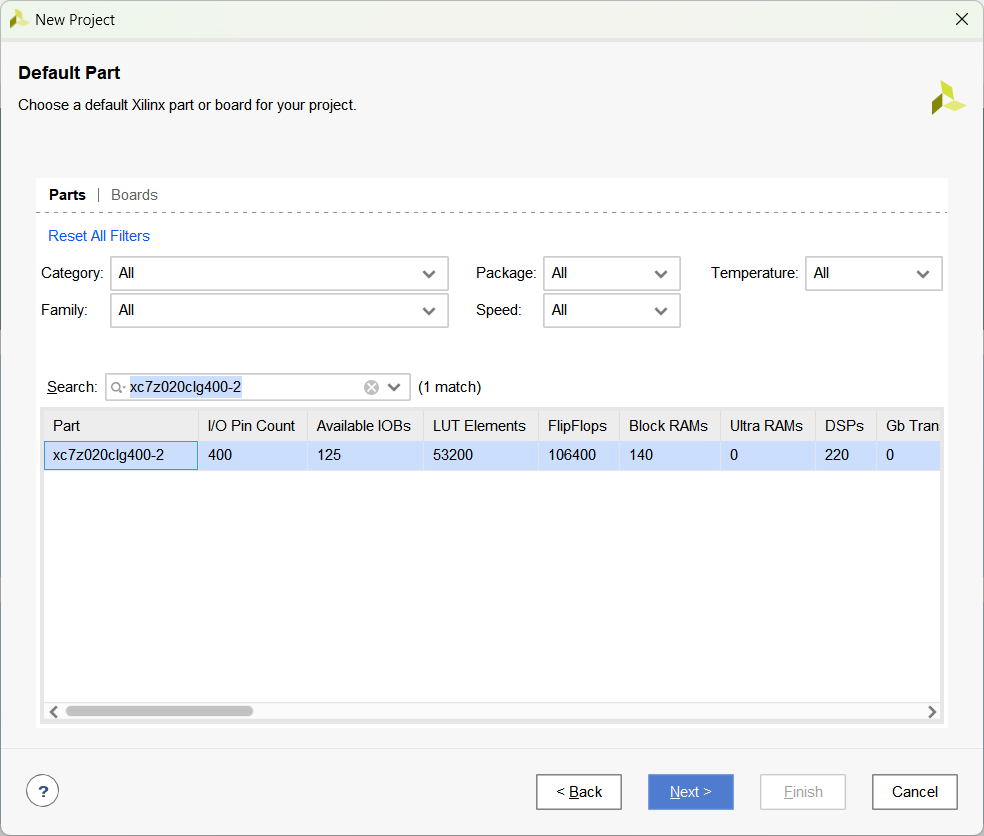

直接下一步,到芯片选择界面,选择的芯片型号为 xc7z020clg400-2:

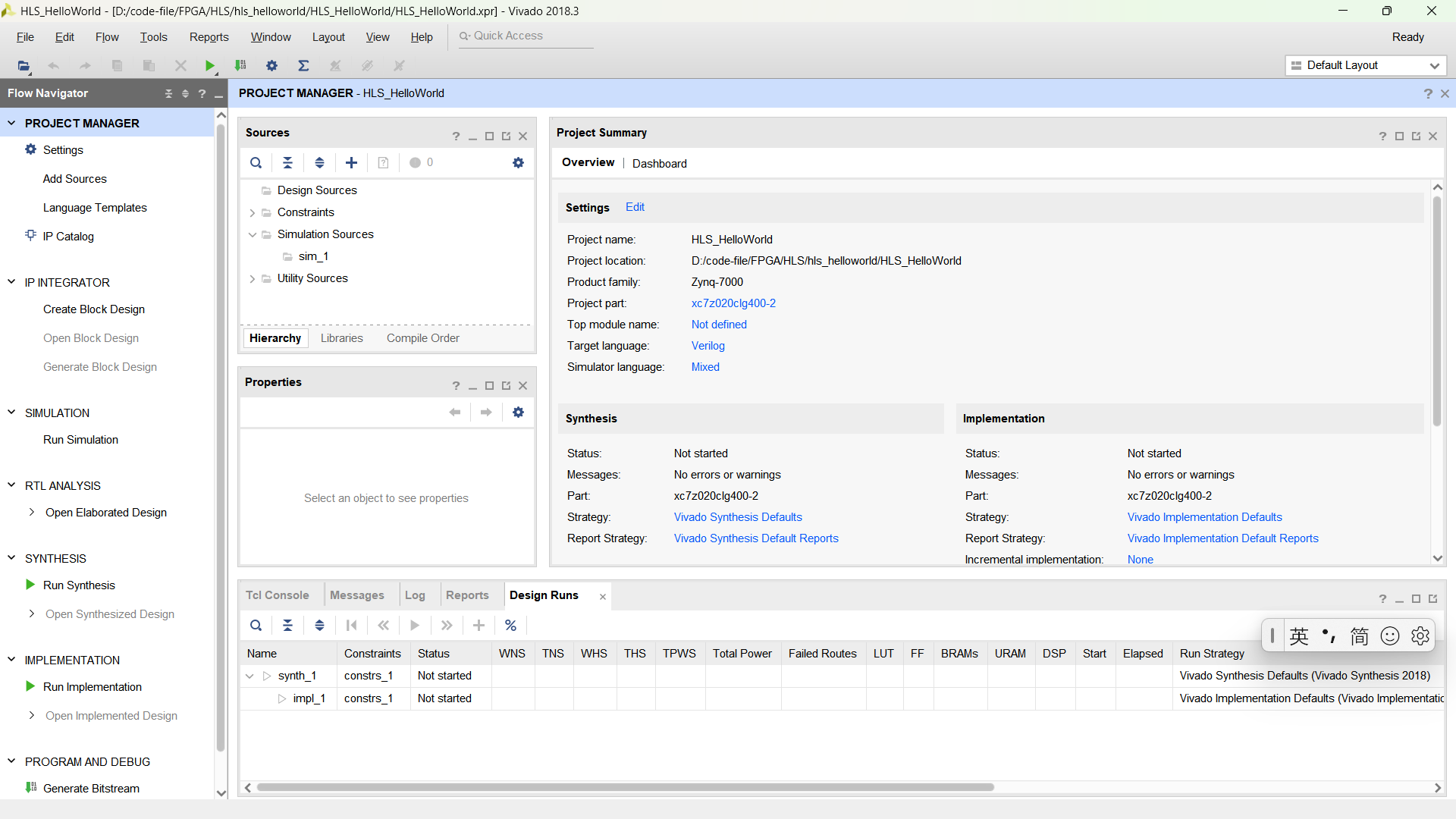

创建成功后界面如下:

注意:这里我们需要使用的时 Vivado 而不再是 Vivado HLS 了

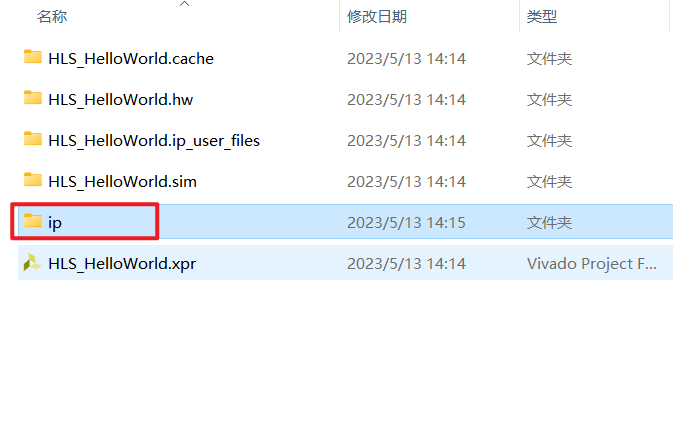

下面我们需要在我们的项目目录下新建一个文件夹用于存储 ip 文件

然后需要将我们前面已经生成的完整的 IP 文件夹复制到我们的 ip 文件夹中

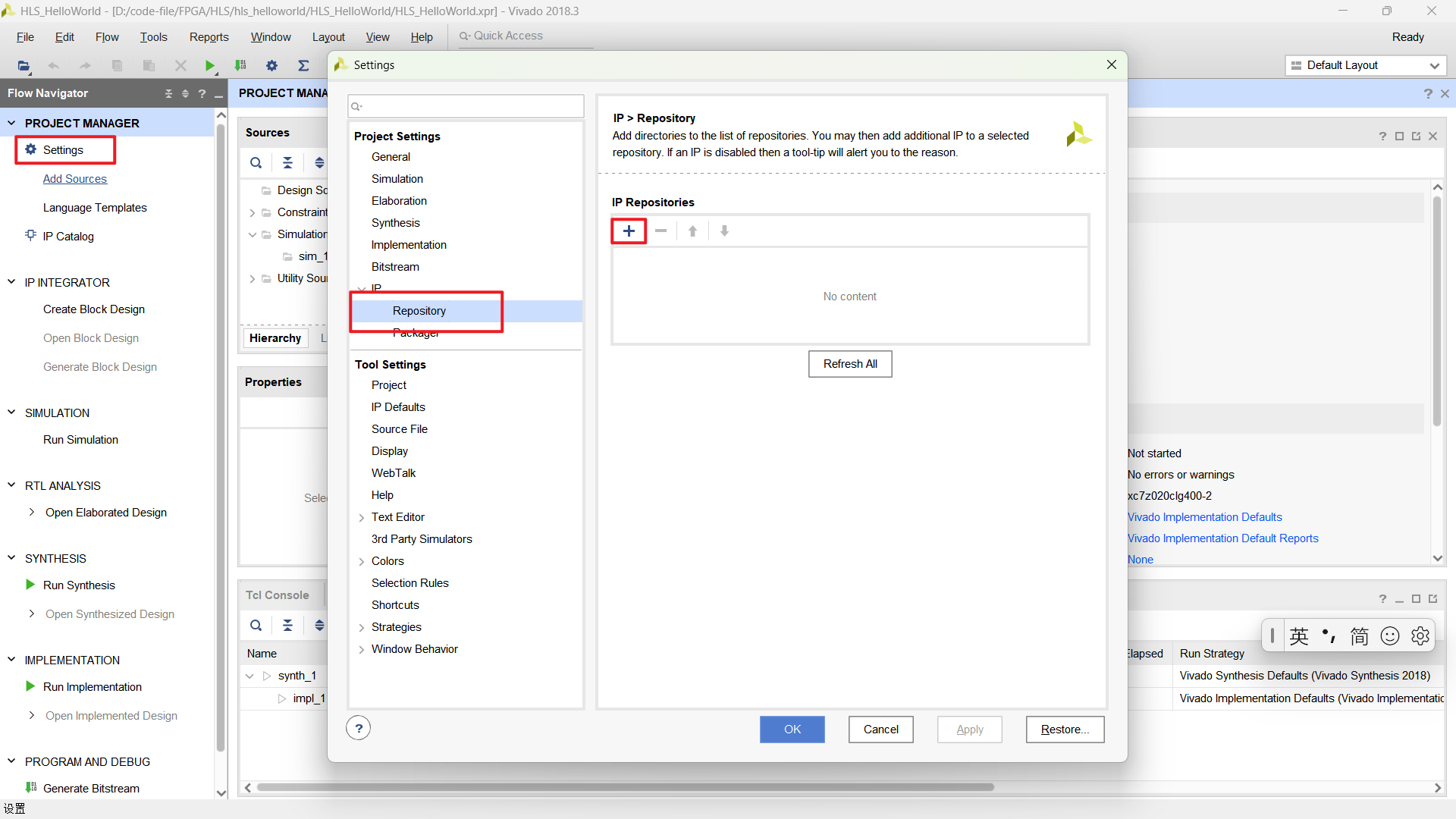

准备好之后,我们就需要在项目中添加我们自己建立的第三方 ip

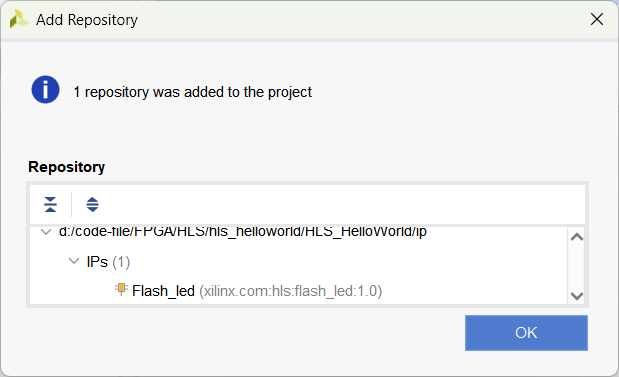

这里选择我们刚刚创建的文件夹即可,这样就能识别到里面的 IP

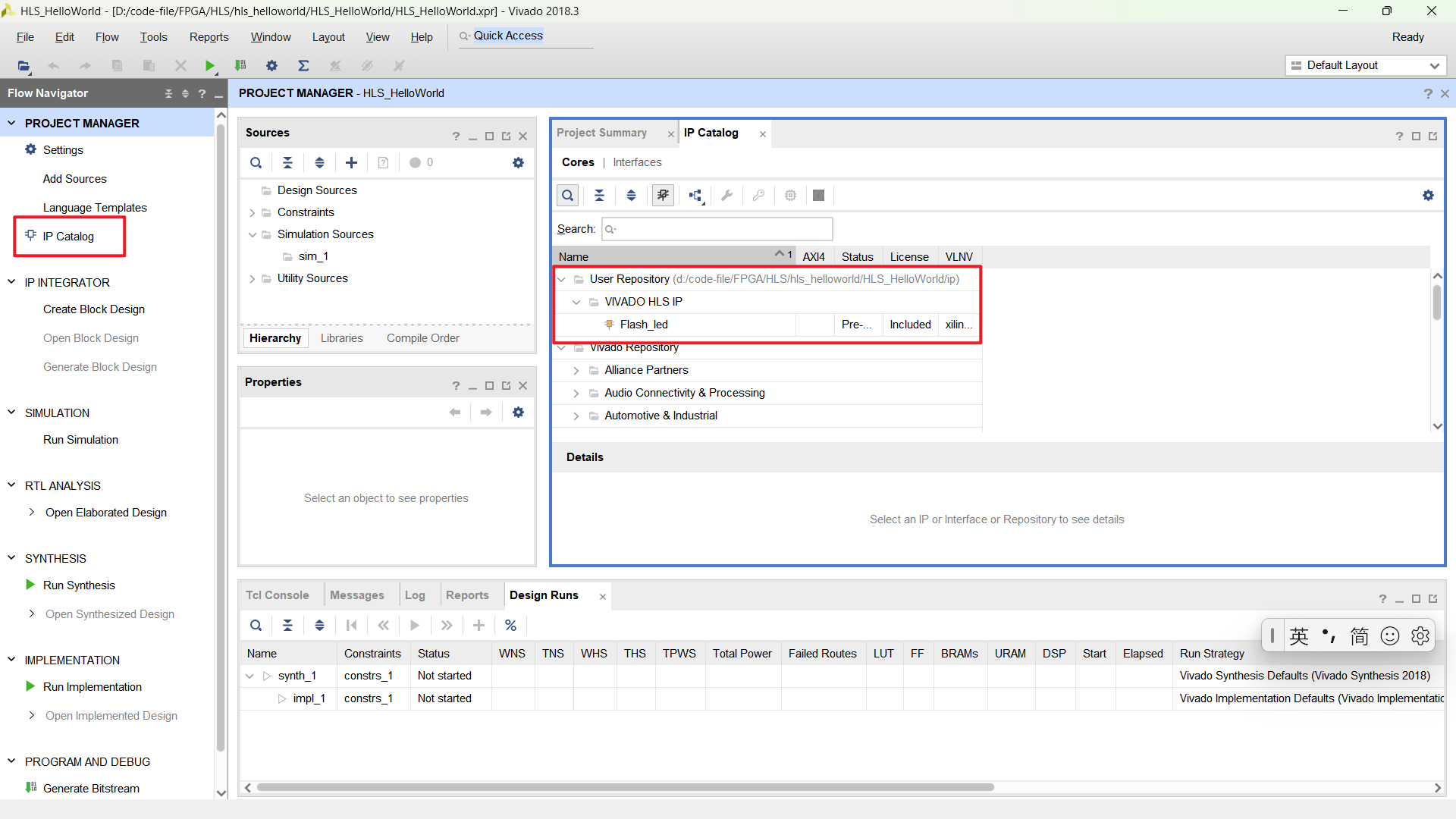

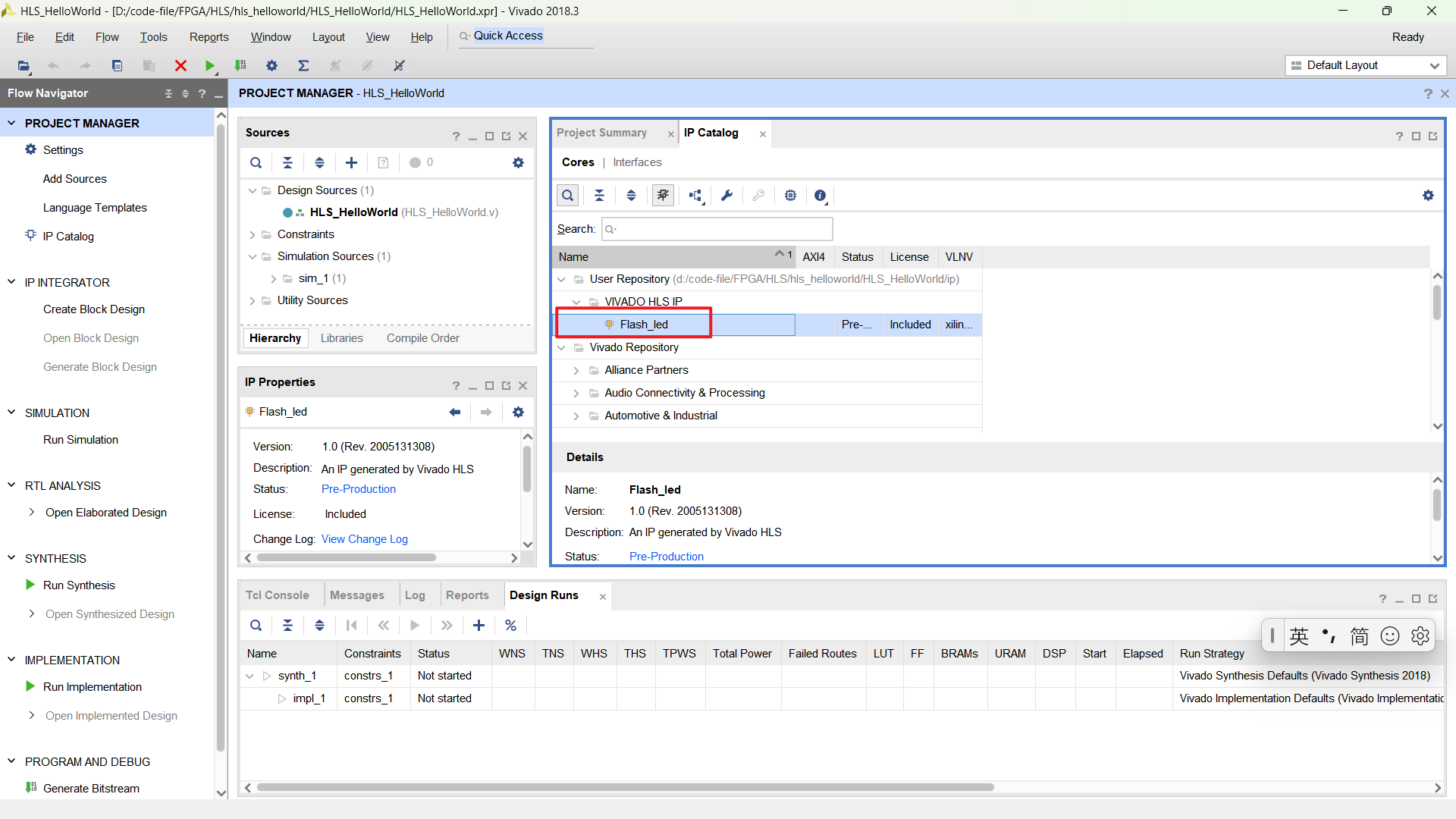

这样我们就能看到我们的 IP 了

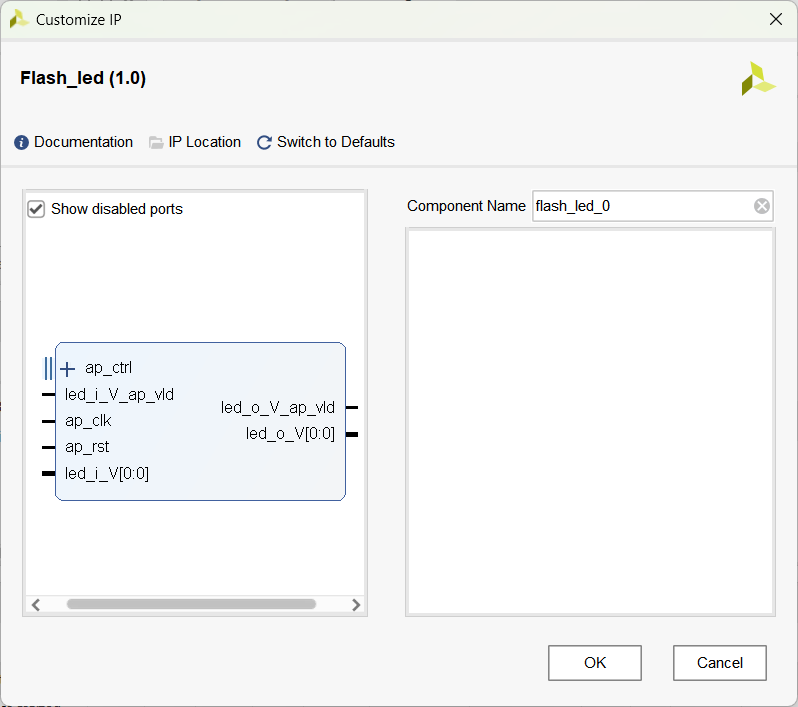

双击就能看到我们 IP 的结构图

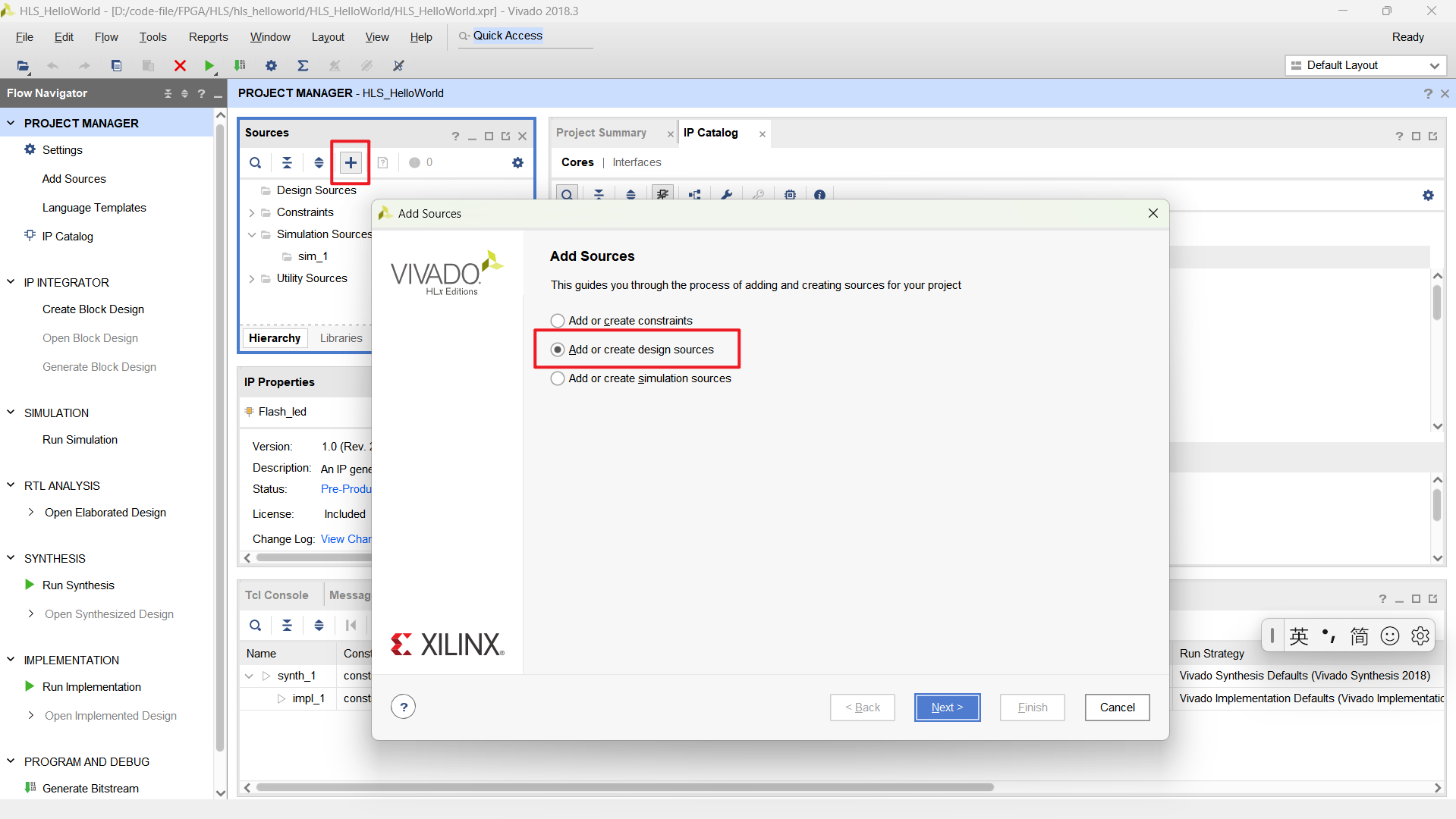

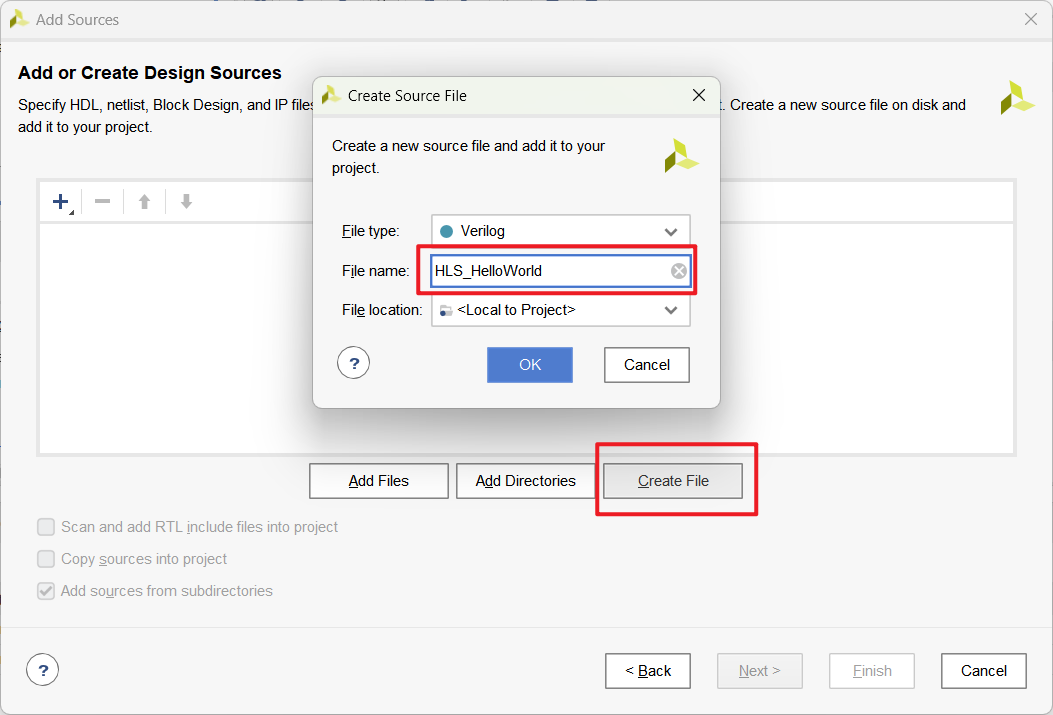

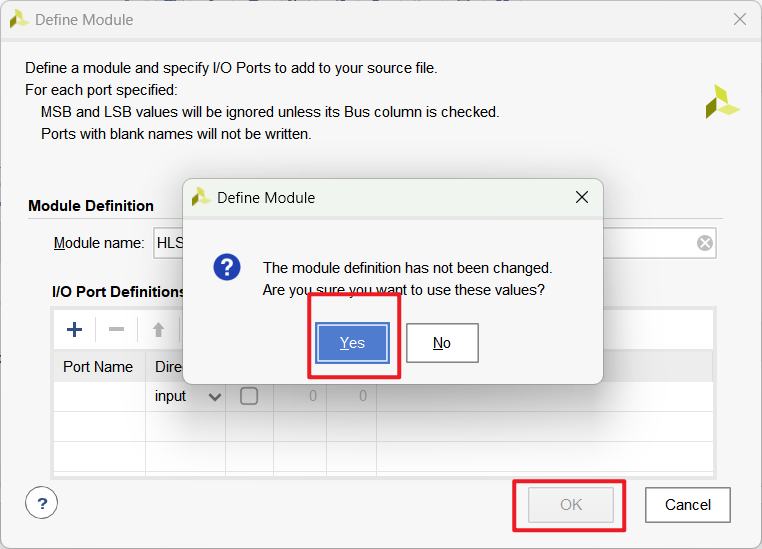

下面我们就需要创建 Verilog 文件来调用我们的 IP

代码设计

生成 IP

创建一个 Verilog 文件,来调用 IP

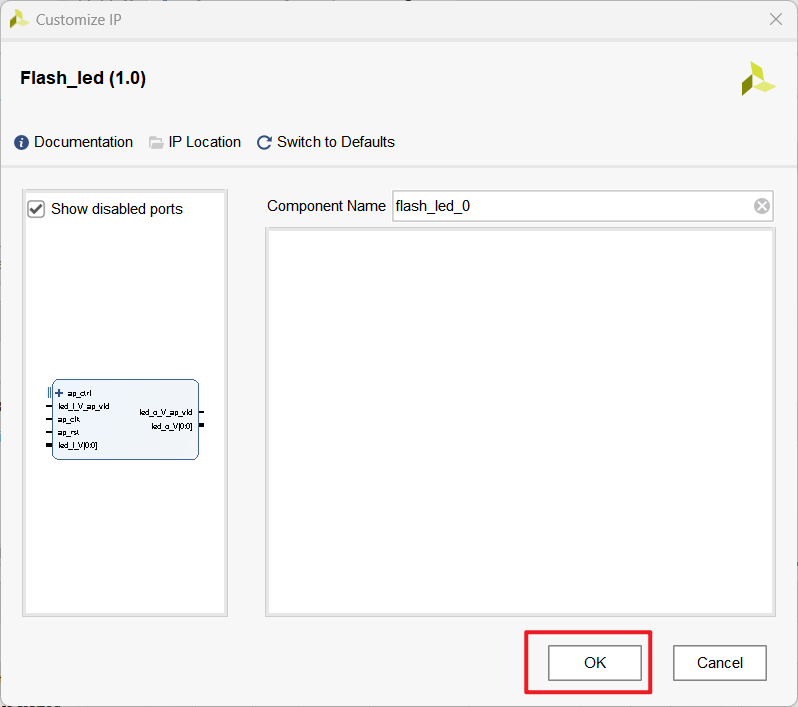

在调用 IP 之前我们需要先通过 IP 文件生成 IP,这里直接双击 IP,点击 ok 即可

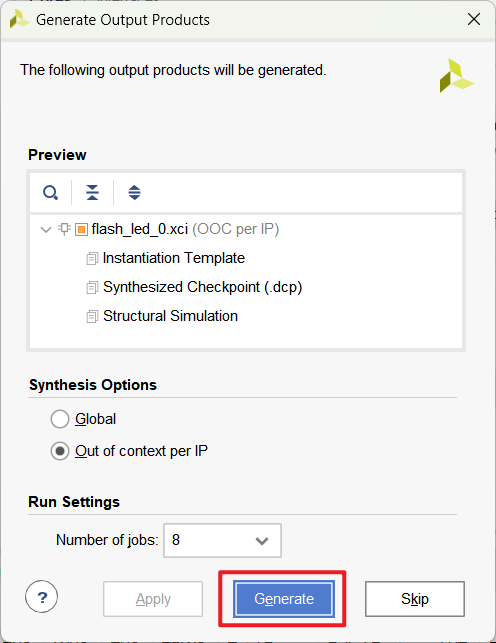

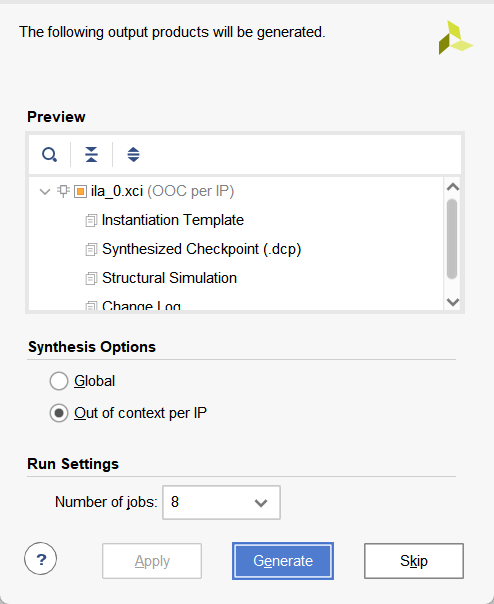

当弹出创建 IP 的对话框时,我们只需要点击生成即可:

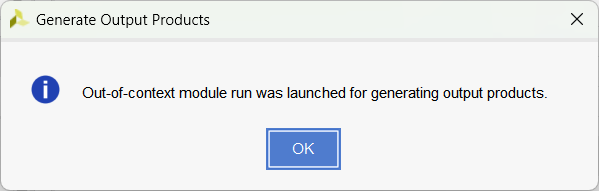

当出现如下提示框,就说明我们的 IP 已经生成成功了

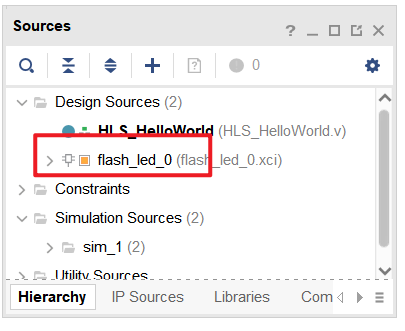

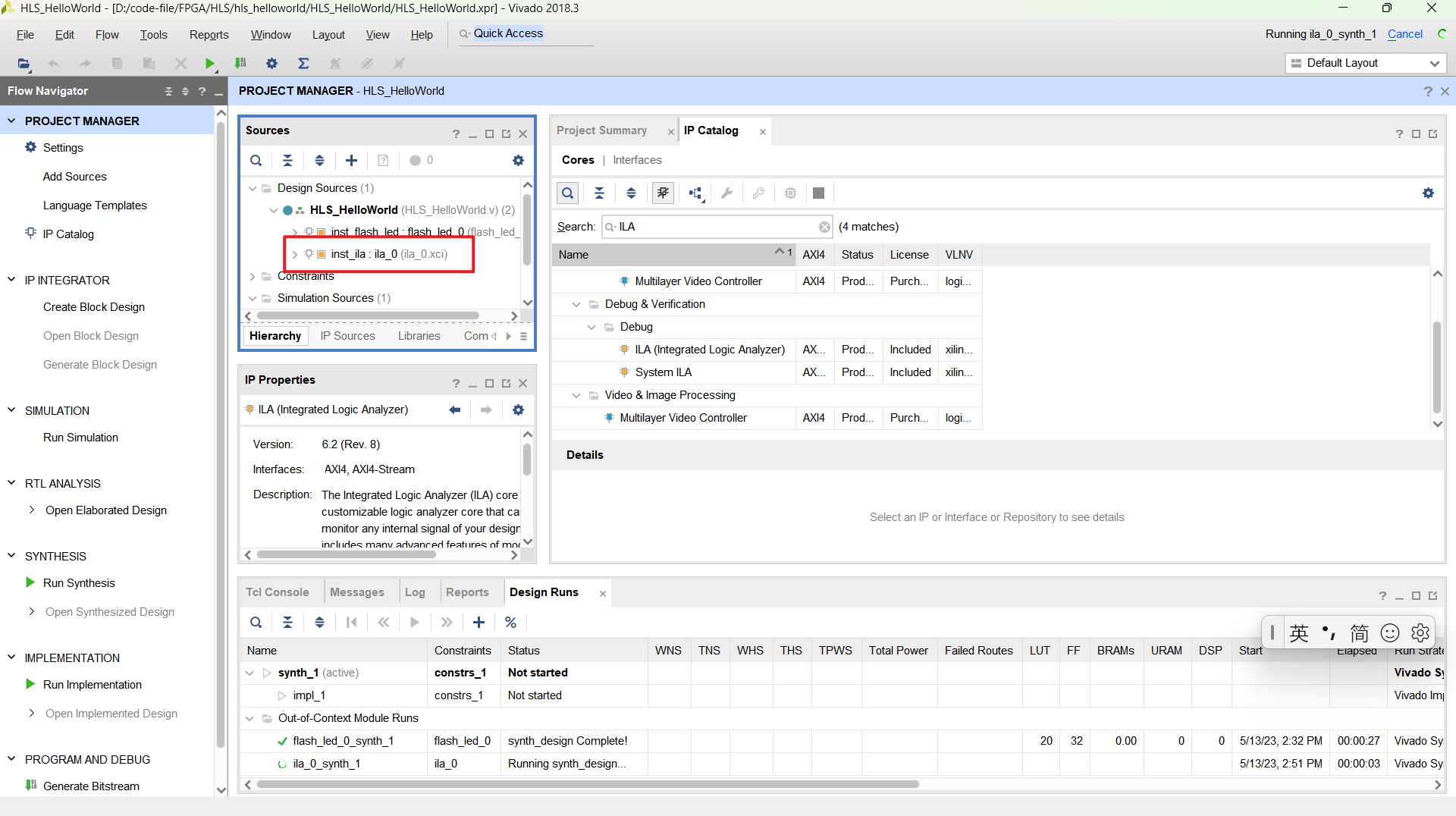

我们也可以看到 IP 文件

代码设计

下面我们就可以开始设计我们的代码文件了,完整代码如下:

HLS_HelloWorld.v:

- `timescale 1ns / 1ps

-

- module HLS_HelloWorld(

- input wire clk ,

- input wire rst_n ,

- output wire led_o

- );

-

- wire rst ;//同步复位

- wire ap_ready ;//当前可以接收下一次数据

- reg ap_start ;//IP开始工作

- reg led_i_vld ;//输入数据有效

- wire led_o_vld ;

- reg led_i ;//输入的led信号

- wire led_o_r ;

- wire ap_done ;

- wire ap_idle ;

- reg [1:0] delay_cnt ;

-

- assign rst = ~rst_n ;

- assign led_o = led_o_r ;

-

- //----------------delay_cnt------------------

- always @(posedge clk) begin

- if (rst==1'b1) begin

- delay_cnt <= 'd0;

- end

- else if(delay_cnt[1]==1'b0) begin

- delay_cnt <= delay_cnt + 1'b1;

- end

- end

-

- //----------------ap_start------------------

- always @(posedge clk) begin

- if (rst==1'b1) begin

- ap_start <= 1'b0;

- end

- else if(delay_cnt[1]==1'b1)begin

- ap_start <= 1'b1;

- end

- end

-

- //----------------led_i_vld------------------

- always @(posedge clk) begin

- if (rst==1'b1) begin

- led_i_vld <= 1'b0;

- end

- else if(delay_cnt[1]==1'b1)begin

- led_i_vld <= 1'b1;

- end

- end

-

- //----------------ap_i------------------

- always @(posedge clk) begin

- if (rst==1'b1) begin

- led_i <= 1'b0;

- end

- else if(led_o_vld==1'b1)begin

- led_i <= led_o_r ;

- end

- end

-

-

- flash_led_0 inst_flash_led (

- .led_o_V_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

- .led_i_V_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

- .ap_clk(clk), // input wire ap_clk

- .ap_rst(rst), // input wire ap_rst

- .ap_start(ap_start), // input wire ap_start

- .ap_done(ap_done), // output wire ap_done

- .ap_idle(ap_idle), // output wire ap_idle

- .ap_ready(ap_ready), // output wire ap_ready

- .led_o_V(led_o_r), // output wire [0 : 0] led_o_V

- .led_i_V(led_i) // input wire [0 : 0] led_i_V

- );

-

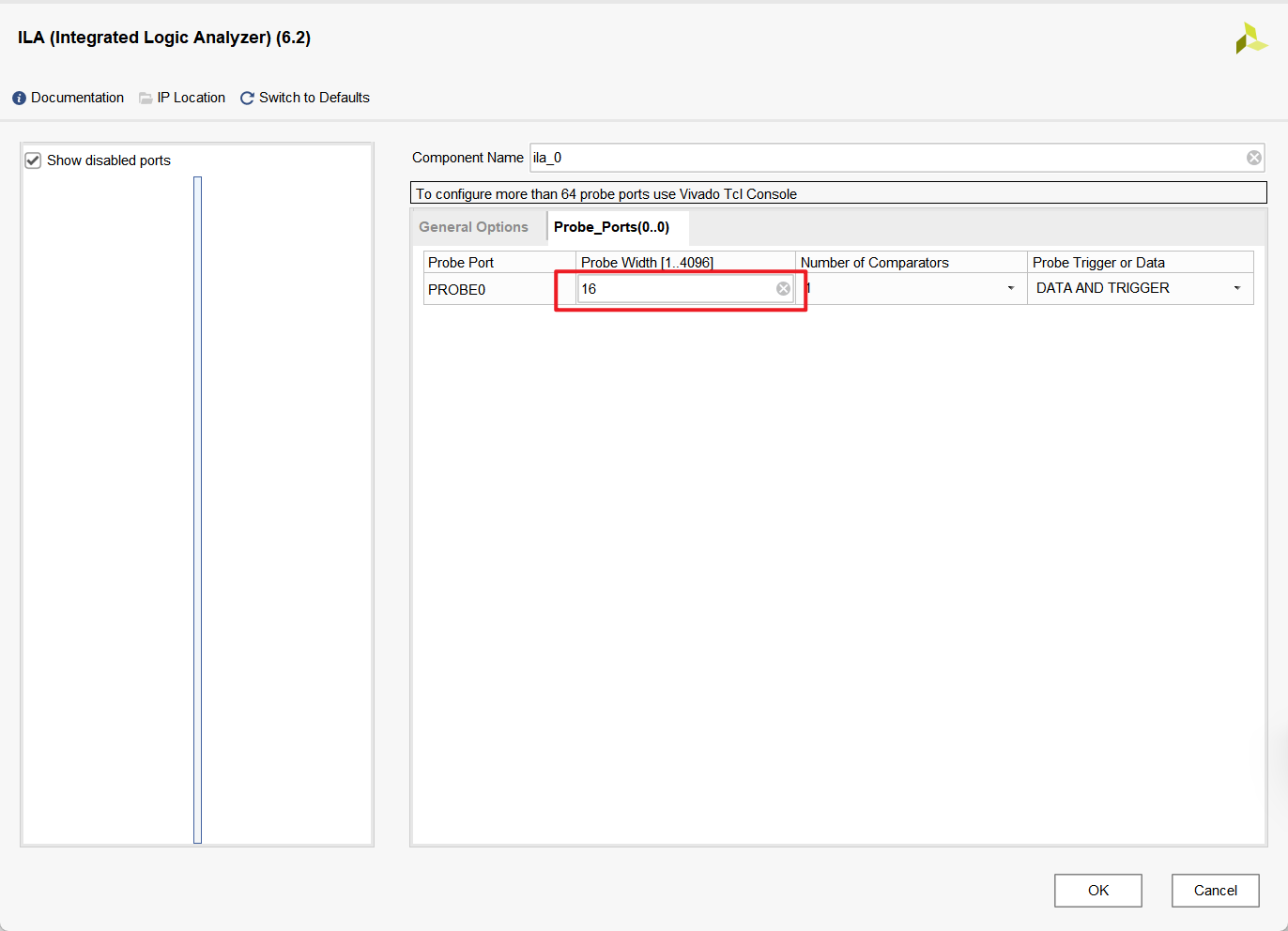

- wire [15:0] probe0;

- assign probe0={

- led_i,

- led_i_vld,

- led_o,

- led_o_vld,

- ap_start,

- ap_ready,

- ap_done

- };

-

- ila_0 inst_ila (

- .clk(clk), // input wire clk

-

-

- .probe0(probe0) // input wire [15:0] probe0

- );

-

- endmodule

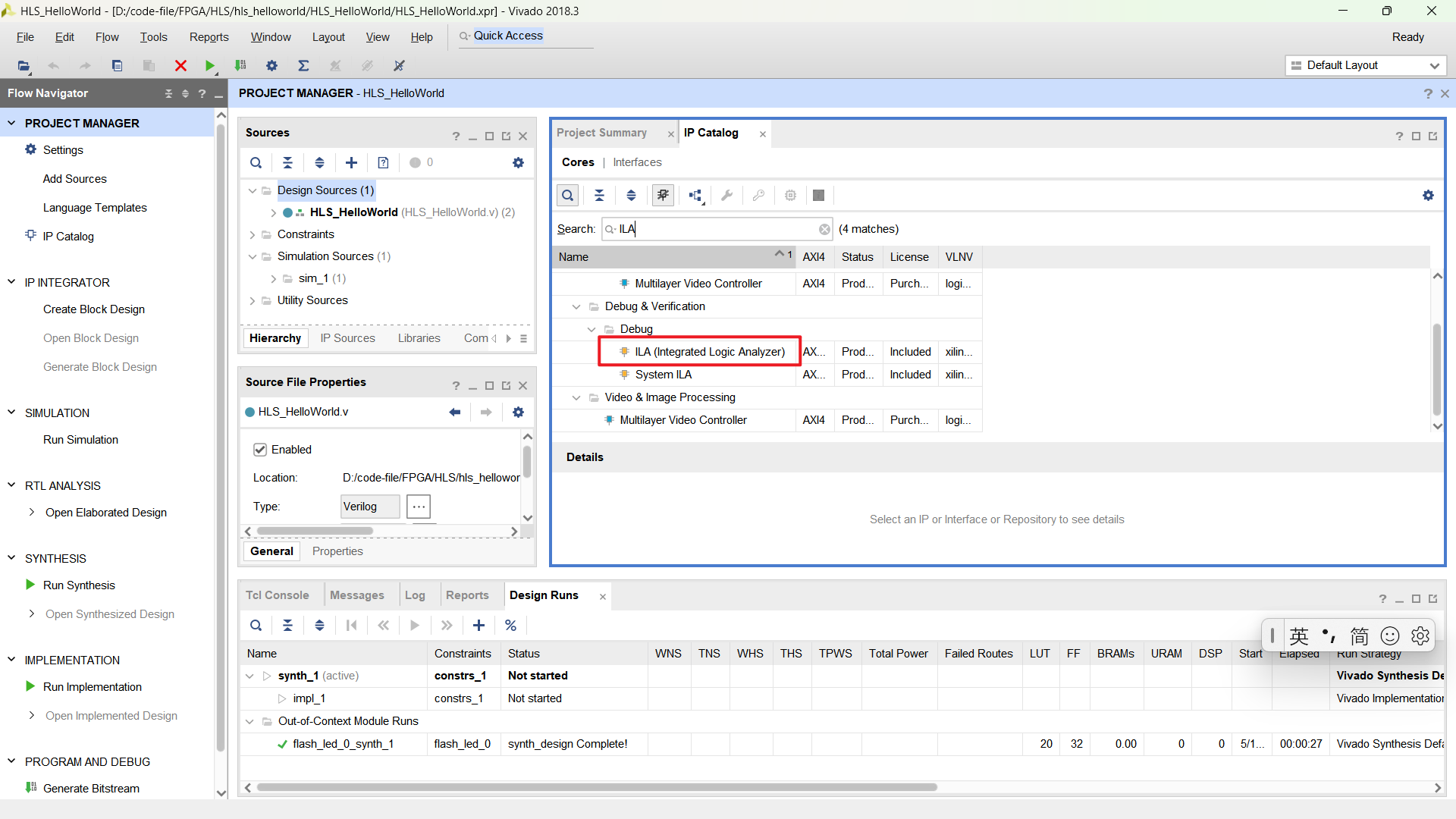

由于我们还需要观察内部信号的变化情况,我们就还需要添加一个 ILA

这里我们已经成功的生成了ILA

结果验证

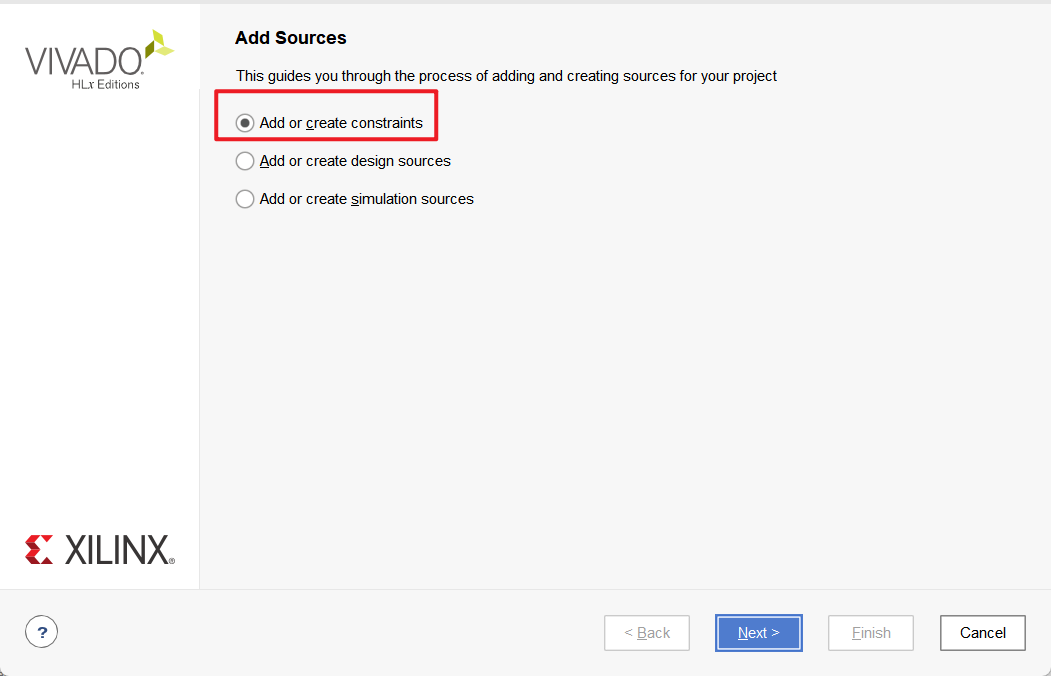

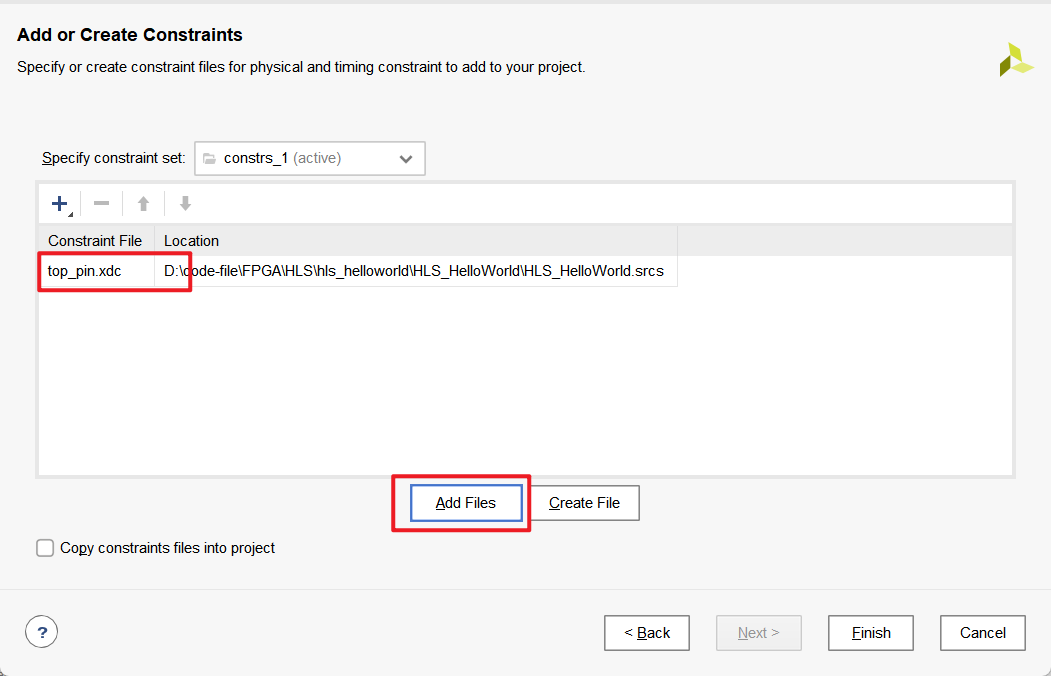

绑定引脚约束文件

当我们一切准备就绪,就可以添加约束文件来观察实验结果,约束文件内容如下:

top_pin.xdc

- ##############LED define##################

- set_property PACKAGE_PIN P15 [get_ports {led_o}]

- set_property IOSTANDARD LVCMOS33 [get_ports {led_o}]

-

- ##############Reset define##################

- set_property PACKAGE_PIN P16 [get_ports {rst_n}]

- set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

-

- ##############50M CLK define##################

- create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

- set_property PACKAGE_PIN N18 [get_ports {clk}]

- set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

选择添加约束文件

这里我们选择我们的约束文件即可:

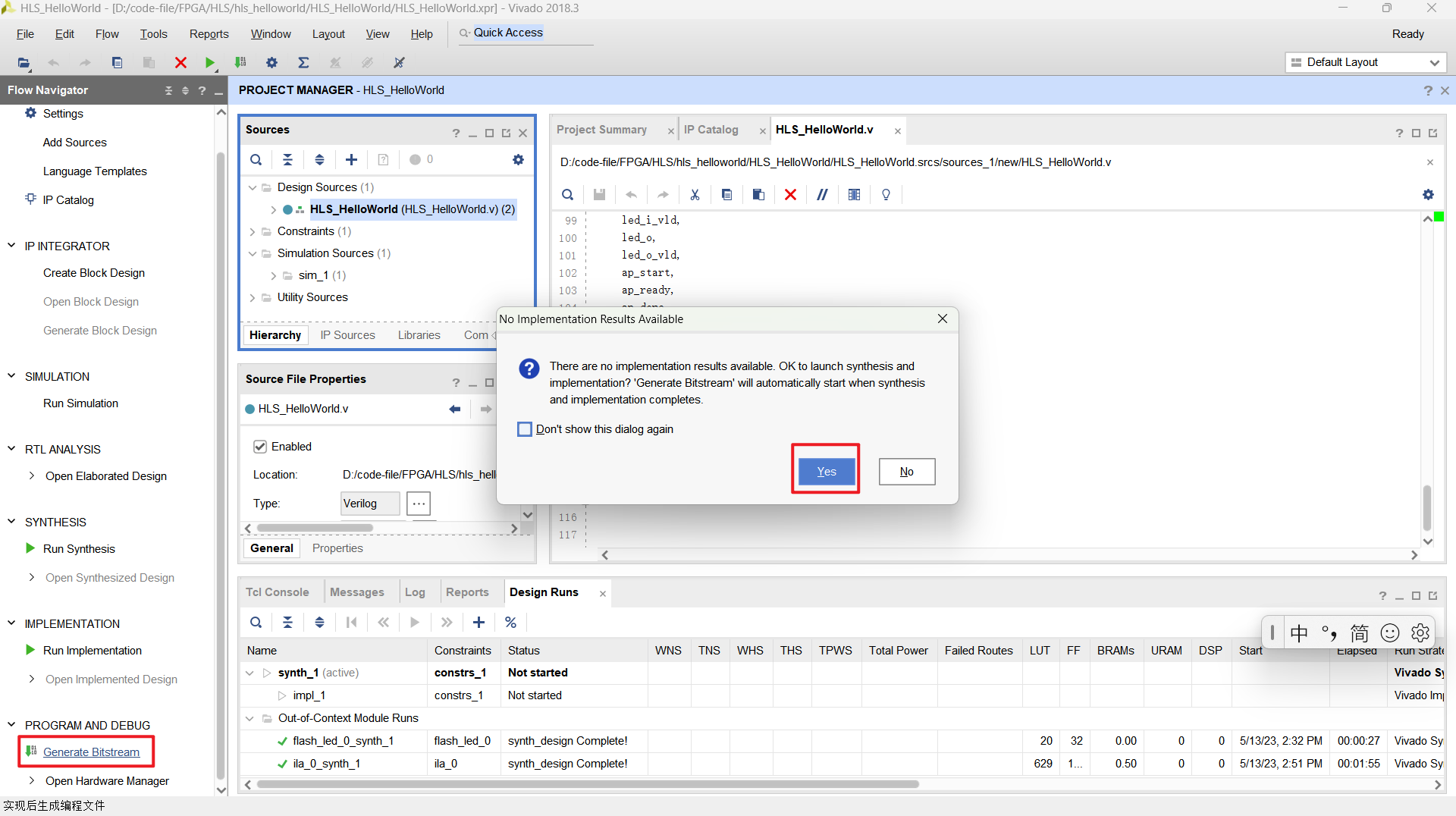

编译烧录

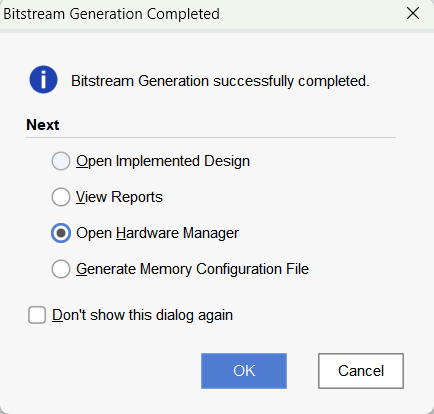

如果前面全部没有问题,我们就可以直接生成 Bit 文件

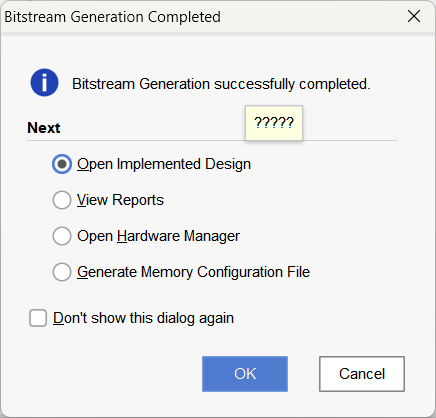

这一步时间较长,需要耐心等待,当出现如下界面就说明已经生成成功了

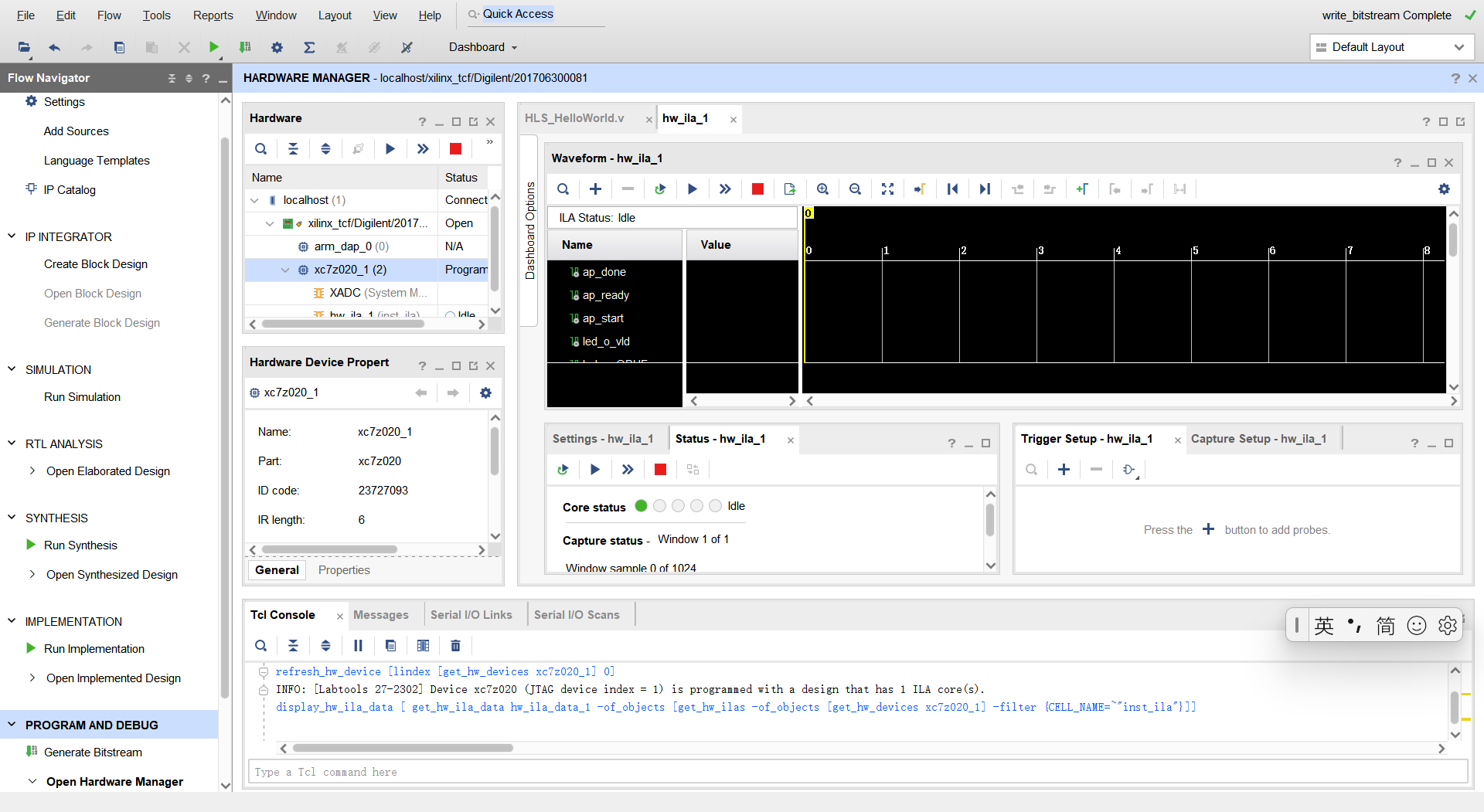

这里我们选择打开硬件设备管理

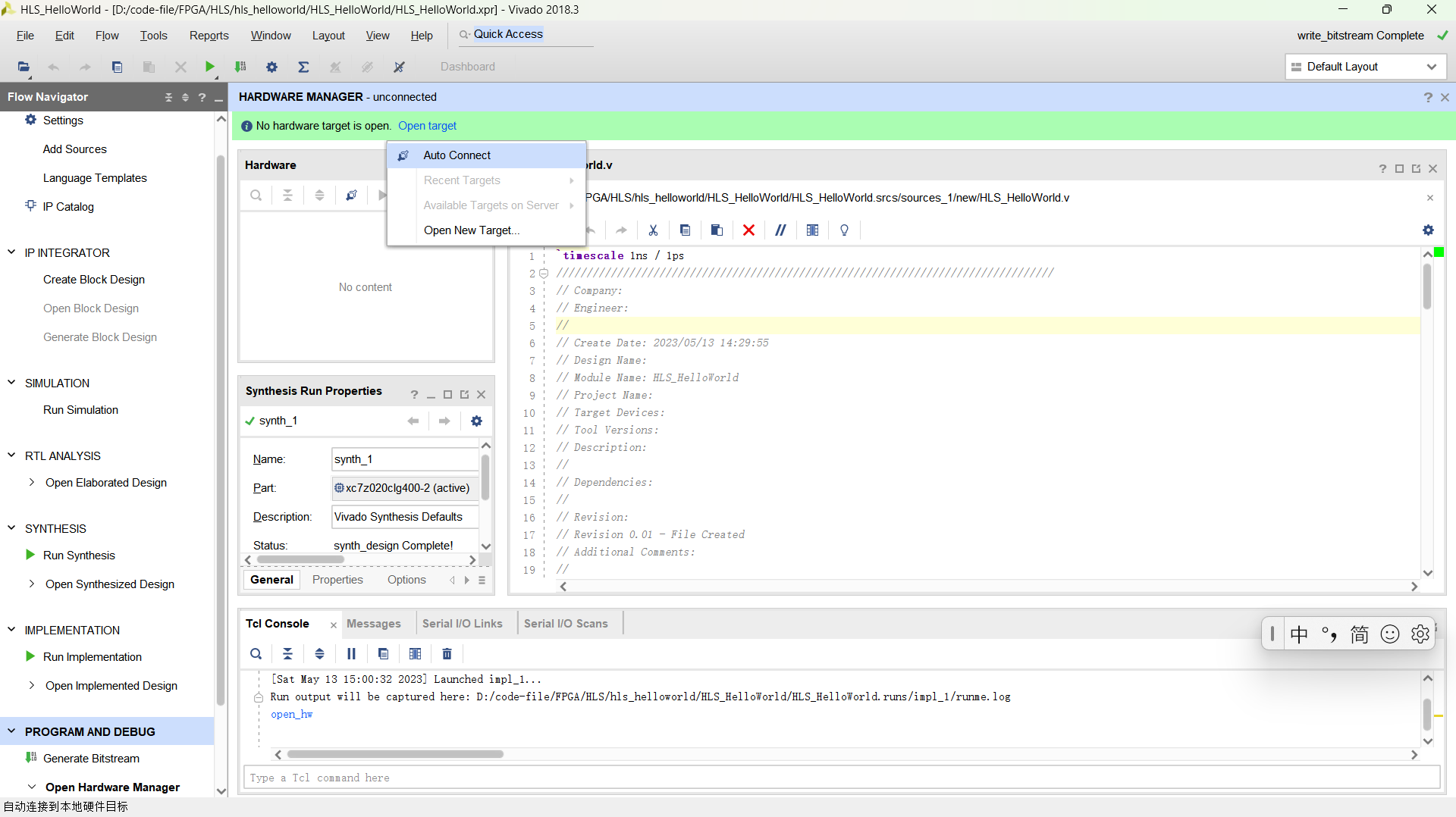

点击 open target 链接我们的 FPGA 芯片

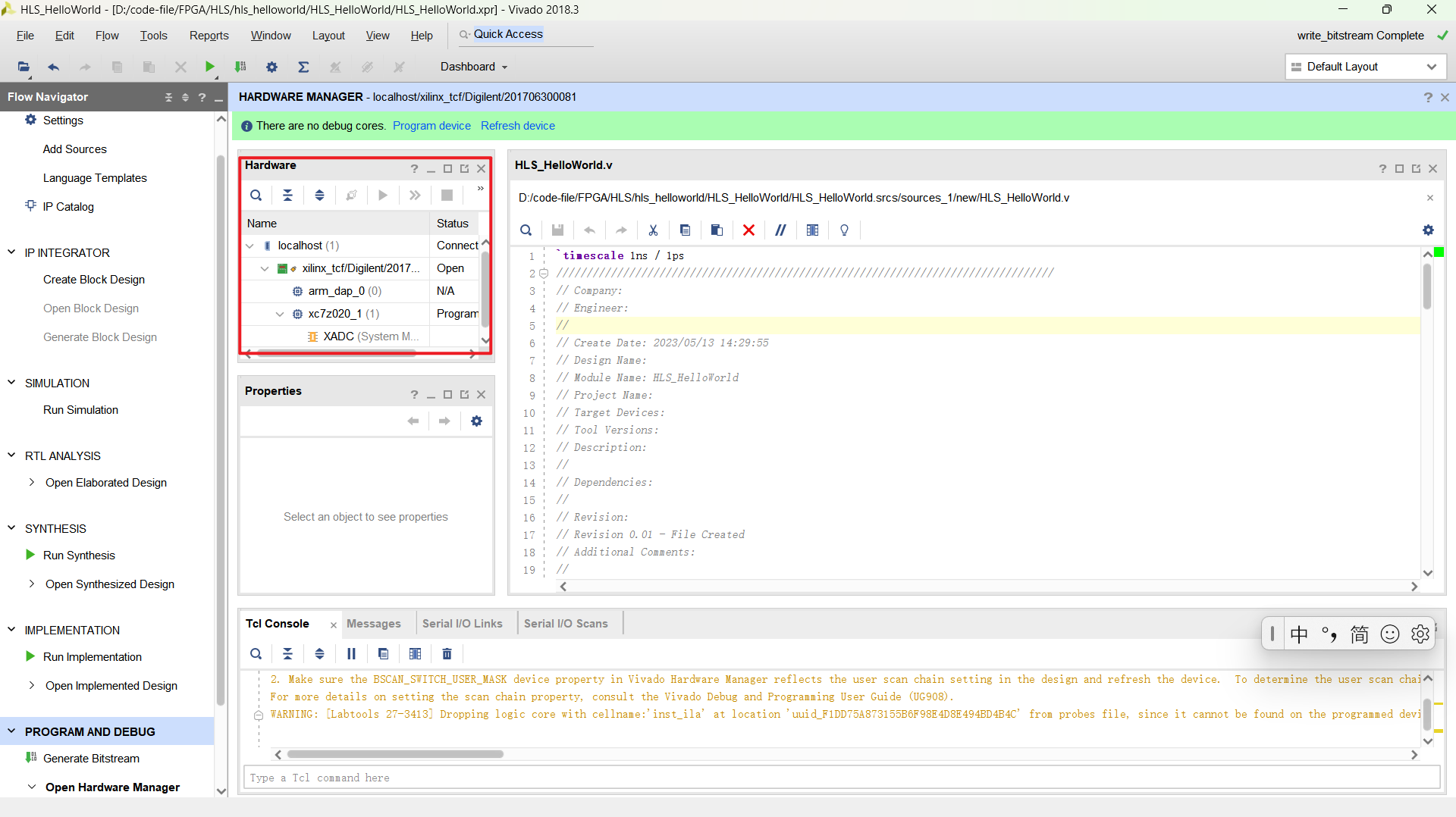

如果 Hardware 中有设备显示就说明我们已经连接成功了

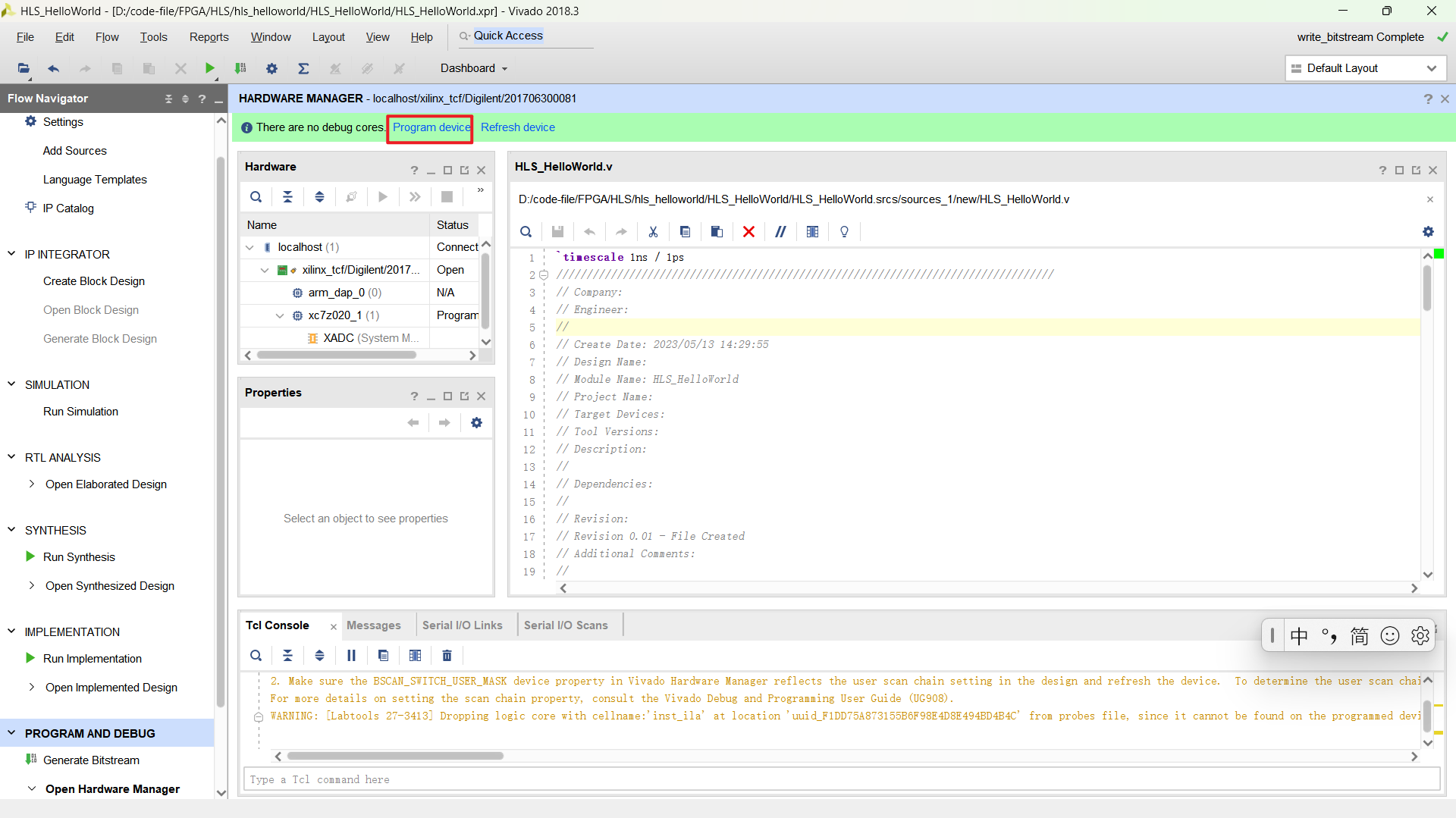

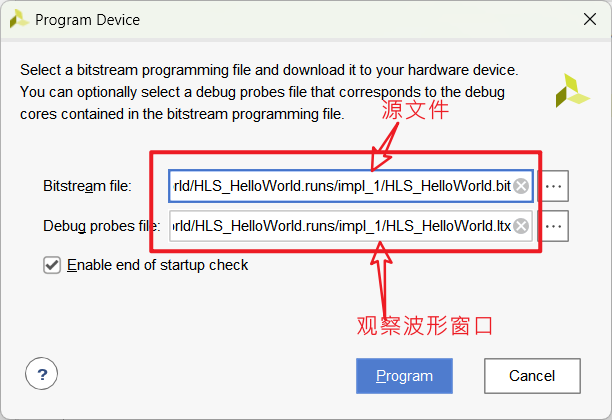

然后我们再点击烧录

这是我们可以看到如下界面,直接点击烧录

这是我们已经将文件下载到了开发板上

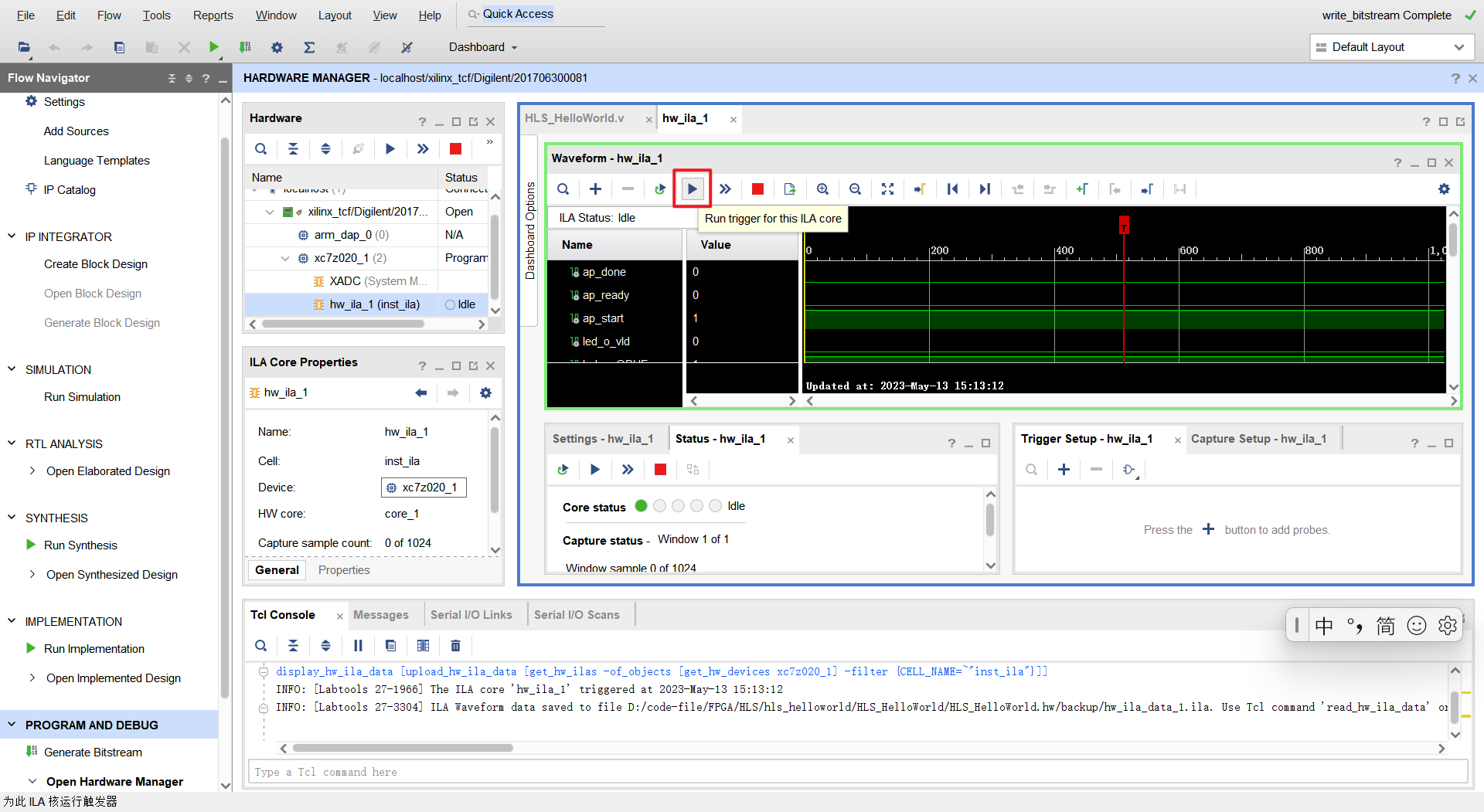

点击运行我们就可以观察到实验现象

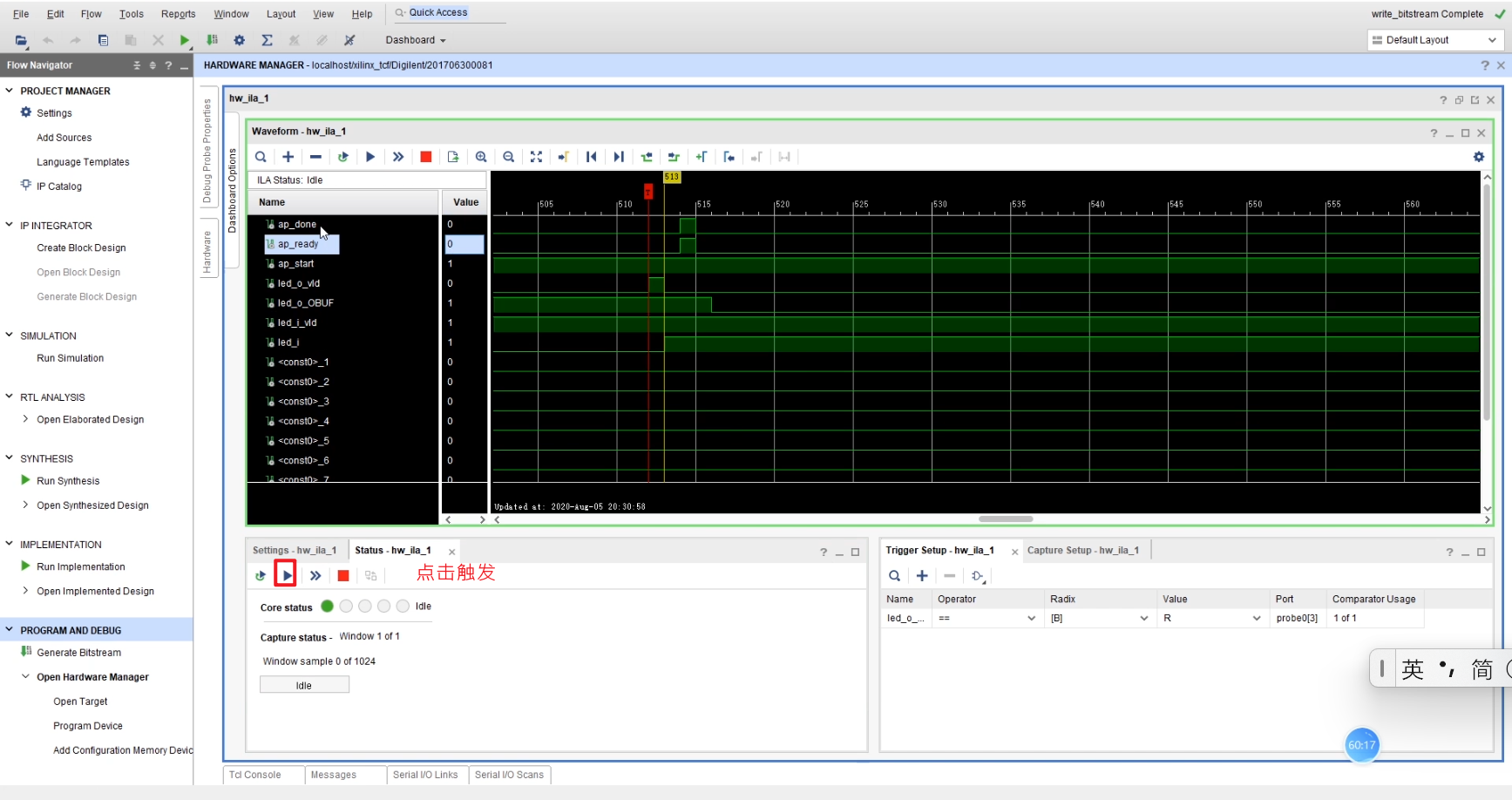

实验结果

由于前面我们设置的时钟时 100 MHz,芯片时钟为 50 MHz,所以这里时 2s 灯亮灭一次

结果:

触发信号如下

到此我们的流水灯就已经完成了