- 1Hive习题汇总(持续汇总中)_hive期末机试

- 2浅谈词嵌入(word embedding)_两个单词能不能做词嵌入

- 3AWS Python应用_pycgarm上显示的aws是什么

- 4动态规划及动态规划的应用

- 5C语言结构体声明的妙用,隐藏结构体内部信息_王凯c语言

- 6K8S彻底卸载教程_卸载kubelet

- 7基于eNSP的某大学校园网络规划与设计(开题报告)_ensp论文题目

- 8Python爬虫入门5:模拟浏览器访问网站_python模拟浏览器访问

- 9【阅读源码】Transformer的FFN机制源码解读(dropout)_ffn代码详解

- 10linux SPI驱动代码追踪_linux3.10内核spi驱动

学习笔记------时序约束之时钟周期约束_时间段约束怎么写

赞

踩

本文摘自《VIVADO从此开始》高亚军

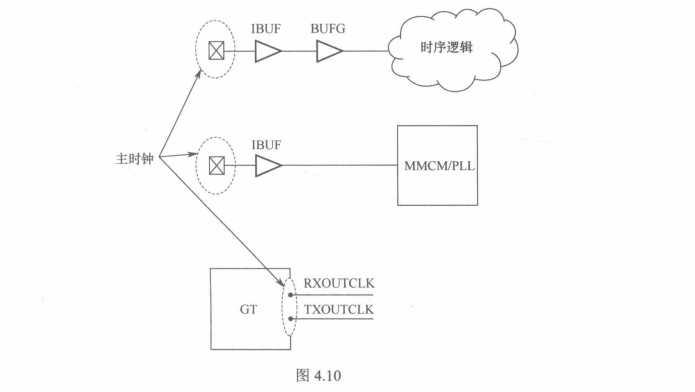

主时钟周期约束

主时钟,即从FPGA的全局时钟引脚进入的时钟或者由高速收发器输出的时钟。

对于时钟约束,有三个要素描述:时钟源,占空比和时钟周期。

单端时钟输入

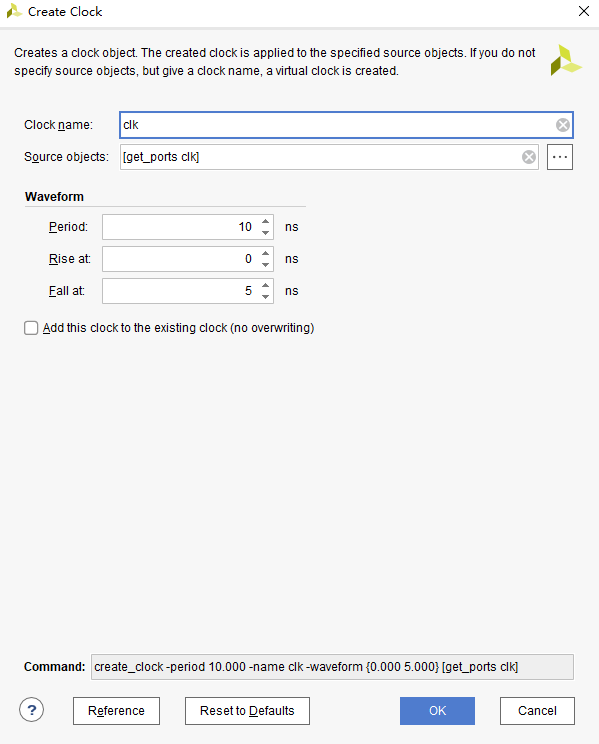

这里我们新建一个工程,clk为100mhz时钟,占空比为50/50,clk1为125mhz,占空比为75/25。这里我们需要用到create_clock来创建时钟。

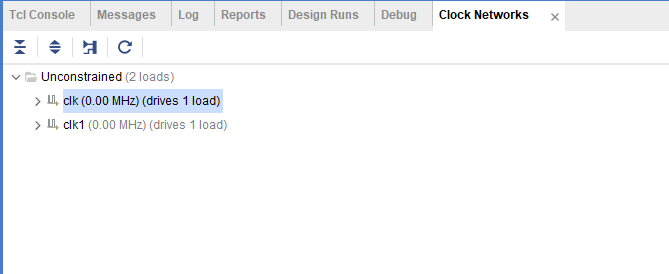

直接使用report clock networks发现有两个时钟,clk和clk1。

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

使用creat_clock创建时钟,-period为周期,-name为时钟的名字,-waveform决定了占空比,这里上升沿在0ns处,下降沿在5ns处。

同理创建clk1时钟约束。

create_clock -period 8.000 -name clk1 -waveform {0.000 6.000} [get_ports clk1]周期为8ns,占空比为75/25。

上述创建的时钟名字叫clk,clk1,在当时还好记住,但是时间长了确实不知道这两个时钟干啥的。

这里我在实际工程中发现有的喜欢用clk_xxmhz来命名时钟,但是在实际过程中发现,在不看约束的情况下往往会被这类时钟的名字误导,比如从pcie出来的时钟,如果采用的gen2。用于axi处理的时钟是125mhz,这里就将该时钟命名为clk_125mhz,其他模式为了统一,也就使用了该名字去写代码,但是在于实际过程中,发现gen2的速度不够,改为gen3,这时候axi时钟就来到了250mhz,往往在调试的过程中,这个时钟的名字大家都不愿意时刻修改,造成了实际使用的250mhz时钟而时钟名字又叫clk_125mhz这样的误解。所以这里我在实际使用中把这个时钟命令为clk_pcie,clk_dac,clk_ddr,clk_adc,这样可以通过名字区分该信号是处于哪一个时钟域下。

差分时钟输入约束

新增差分时钟clk_led2_p,clk_led2_n。输入为200mhz,占空比为50%。

对于差分时钟输入,我们只需要对其一端进行约束即可。

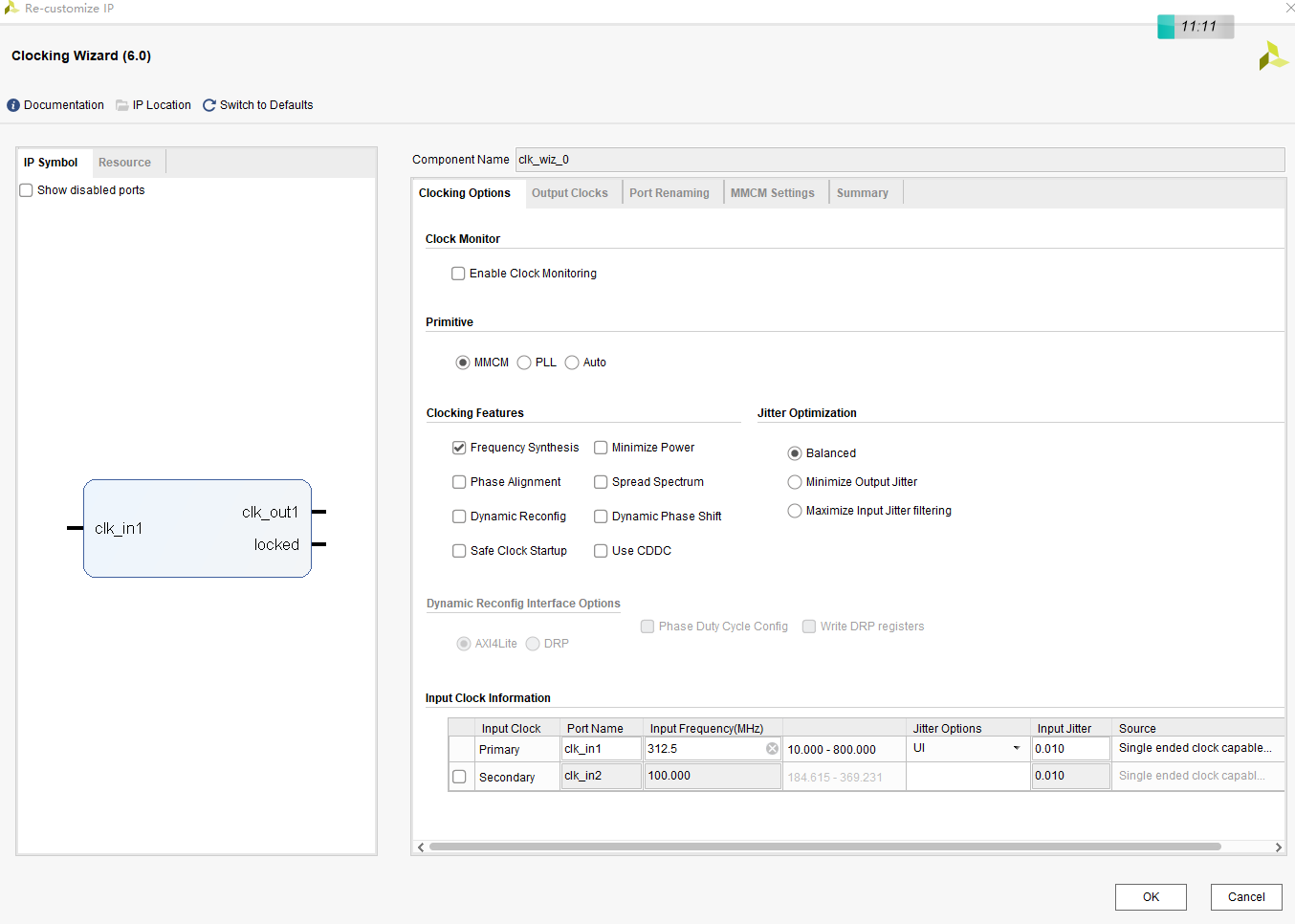

create_clock -period 5.000 -name clk_led2_p -waveform {0.000 2.500} [get_ports clk_led2_p]时钟输入直接进入mmcm或者pll

输入clk_pll,输入时钟312.5mhz,单端。

选择信号源,如果进入pll的时钟直接从引脚上输入进来就选择single ended clock capable pin或者differential clock capable pin。如果是输入时钟先经过IBUF在进入pll则直接选择nobuffer。

进入pll或者mmcm的时钟一般不需要再进行时钟约束,可以在ip的xdc文件中找到相关的约束。

生成时钟周期约束

生成时钟分为两种,自动生成的时钟和用户逻辑生成的时钟。自动生成的时钟包括由MMCM/PLL,BUFR(7系列FPGA)和BUFGCE_DIV(Ultrascale系列FPGA)生成的时钟。对于上述的这些时钟,工具会自动的根据其与输入时钟的关系自动推断出时钟周期、占空比,以及该时钟与输入时钟的相位关系。

第二种就是用户使用逻辑生成的时钟。事实上,在FPGA设计中,只有在时钟频率很低或者扇出很小的情况下才可能使用该时钟。这是因为这类时钟通常由组合逻辑和时序逻辑生成,时钟质量很差。这类情况在逻辑中还是很常见,一些低速总线上,比如说uart,iic,spi上都存在这类使用情况。但是这些时钟作者往往不回去对其专门进行约束,这样导致了工具就会产生虚假的时序报告。

例如使用逻辑产生一个2分频时钟。生成的时钟再去控制其他信号。

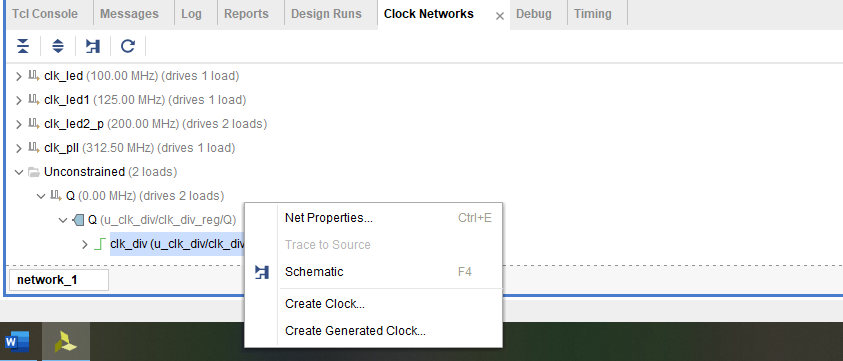

使用report clock nerworks查看时钟。

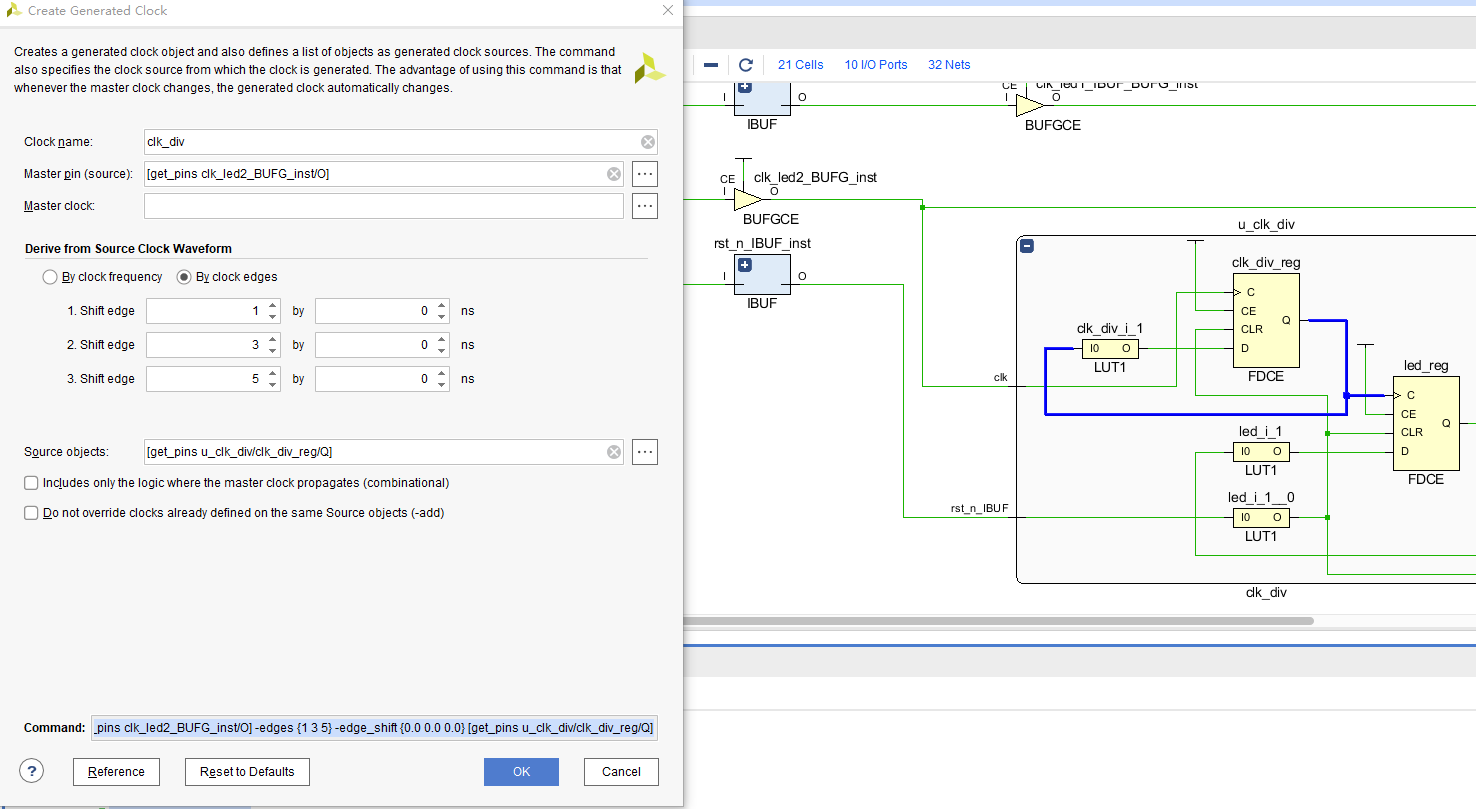

发现并没有对其进行约束。因为这个clk_div是我们内部逻辑分频出来的时钟。所以这里创建生成时钟。

创建完成后可以看到自动生成了xdc约束语句在你的约束目标文件中。

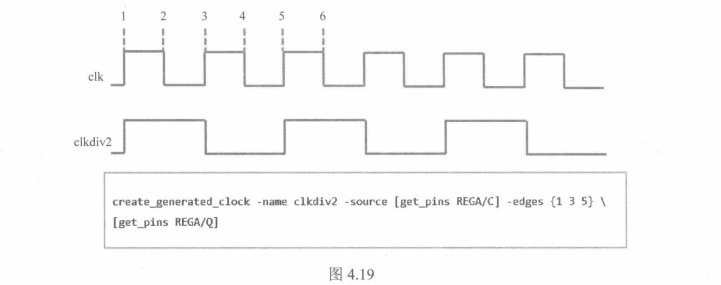

create_generated_clock -name clk_div -source [get_pins clk_led2_BUFG_inst/O] -divide_by 2 [get_pins u_clk_div/clk_div_reg/Q]使用第二种方式通过生成时钟与master clock的频率关系,以及-edges选项完成时钟周期约束。-edges指明了生成时钟的第1个上升沿,第1个下降沿和第2个上升沿对应于master clock的位置。该位置由master clock的0时刻上升沿开始计数。每遇到一个边沿即加1。-edges的三个数值正好对于生成时钟的一个周期。

create_generated_clock -name clk_div -source [get_pins clk_led2_BUFG_inst/O] -edges {1 3 5} -edge_shift {0.000 0.000 0.000} [get_pins u_clk_div/clk_div_reg/Q]然而在实际的逻辑中往往不使用直接逻辑分频的时钟进always,而是使用采沿的方式来进行后续判断。

- always@(posedge clk or negedge rst_n)

- begin

- if(rst_n == 1'b0)begin

- clk_div_d1 <= 1'b0;

- end

- else begin

- clk_div_d1 <= clk_div;

- end

- end

-

- //------------------------------------------------------------

- //------------------------------------------------------------

- always@(posedge clk or negedge rst_n)

- begin

- if(rst_n == 1'b0)begin

- led <= 1'b0;

- end

- else if(clk_div_d1 == 1'b0 && clk_div == 1'b1 )begin

- led <= ~led;

- end

- else begin

- led <= led;

- end

- end

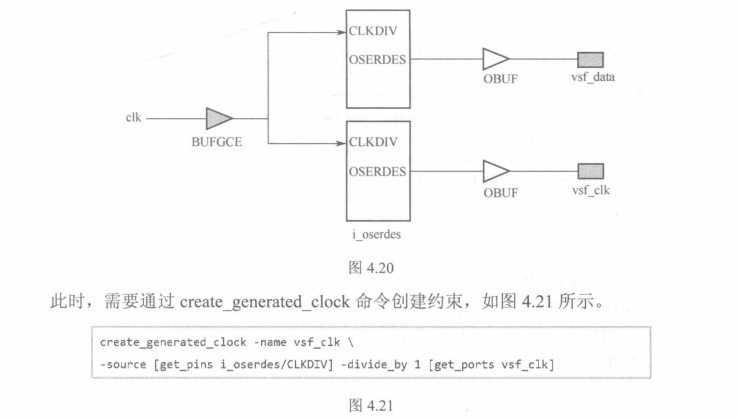

还有一种用户生成时钟的情形,即源同步设计中的随路时钟。随路时钟是指与数据同时生成的时钟,且同时给到接收端,以生成该数据在接收端的采样时钟。在源同步设计中,为了确保输出数据与输出时钟(随路时钟)具有相同的延迟,通常经过同意的电路单元(这里使用oserdes)后再输出。

这里笔者目前没有使用过这种情况。

creat_generated_clock -name vsf_clk \ -source [get_pins i_oserdes/CLKDIV] -divide_by 1 [get_ports vsf_clk]对同一时钟源添加多个时钟周期约束

这里我们也是直接打开vivado的example bft工程。

这里可以看到输入端有两个时钟,wbclk和bftclk。

- entity bft is

- port (

- wbClk, bftClk, reset : in std_logic;

- wbDataForInput :in std_logic;

- wbWriteOut: in std_logic;

- wbDataForOutput : out std_logic;

- wbInputData : in std_logic_vector (31 downto 0);

- wbOutputData : out std_logic_vector (31 downto 0);

- error : out std_logic

- );

从自带的约束中可以看到,wbclk时钟周期为10ns,频率为100mhz。bftclk时钟周期为5ns,频率为200mhz。

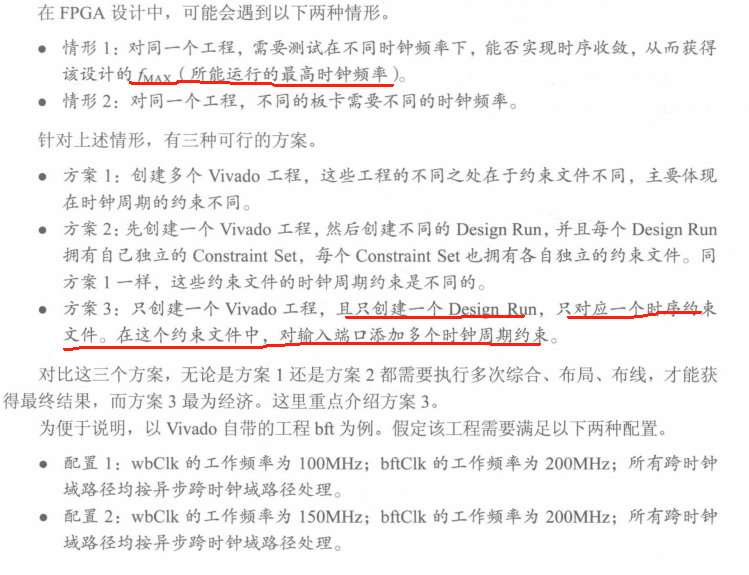

上面提到需要将wbclk时钟频率提高到150mhz。

- create_clock -name wbClkA -period 10 [get_ports wbClk]

- create_clock -name wbClkB -period 6.667 [get_ports wbClk] -add

- create_clock -period 5 -name bftClk [get_ports bftClk]

- set_clock_groups -physically_exclusive -name two_clk_grps \ -group wbClkA -group wbClkB

- set_clock_groups -async -name my_async_clks \ -group [get_clocks "wbClkA wbClkB"] -group bftClk

在约束工作频率为150mhz的时钟,需要添加-add选项,否则,都一条约束就会被覆盖。同时两个时钟wbClkA和wbClkB不可能同时存在。这里就用到了set_clock_groups及-physically_exclusive选项。在声明跨时钟与路径存在异步时,用到了set_clock_groups以及选项-asynchronous简写为-async。

可以看到最终生成的时序报告。报告会针对每个时钟,生成一个wbClkA和wbClkB显示相应的时序路径。

调整时钟特性约束

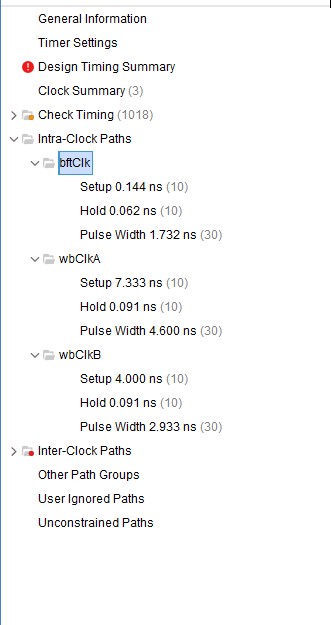

对于时钟抖动(jitter),建议采用vivado的默认值进行设置。如果需要修改,则可以通过set_input_jitter命令来实现。对于时钟的不确定性(clock uncertainty),可以采用set_clock_uncertainty进行修改。例如现在由clk_led1取得的时序路径添加额外的时钟不确定性(500ps)

set_clock_uncertainty -from clk_led1 -to clk_led1 0.500

在最后的时序报告中可以看到clock uncertainty的数值。