- 1如何将原始SNP信息转化为0,1,2的矩阵形式_snp 0 1 2

- 2对于云原生时代的后端业务开发和项目系统学习,选Go Or Java?_go最佳就是云原生开发吗

- 3Guitar Pro 8.1 Mac/WIN中文破解版 2024最新下载、安装、激活、换机图文教程

- 4Linux之bash介绍

- 55个大厂出品的移动端组件库推荐!

- 6OpenAI(chatgpt)提示Account deactivated怎么办?_your openai account has been deactivated, please c

- 7RK3568 学习笔记 : 更改 u-boot spl 中的 emmc 的启动次序

- 8GitHub双重认证问题_github two-factor recovery

- 9如何开发类似QFIL下载工具_qsaharaserver.exe

- 10NLTK库安装教程(详细版)_nltk安装

FPGA秋招-笔记整理(2)

赞

踩

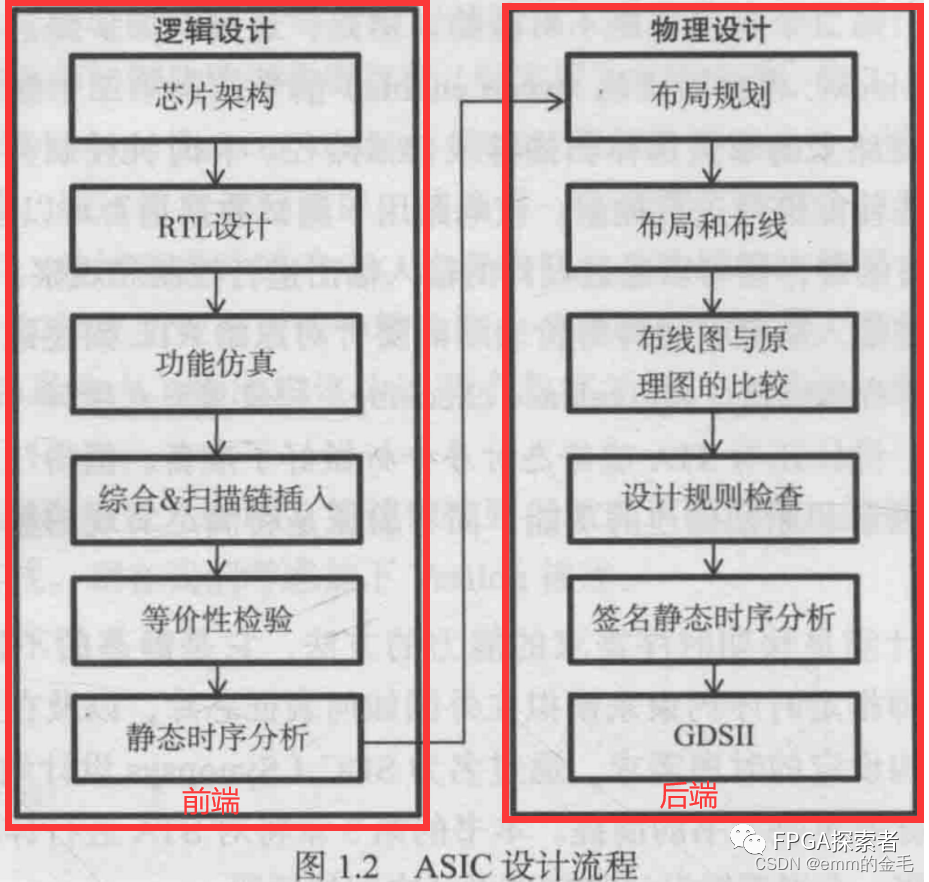

一、数字IC前端设计的主要流程

参考:数字IC前端设计流程及工具【RTL设计+功能仿真】【综合】【DFT】【形式验证】【STA静态时序分析】

以门级网表(Netlist)的生成为界限,将整个流程分为前端和后端。

布局布线之前可以认为是前端,布局布线之后为后端。

数字前端设计

逻辑设计:芯片架构->RTL代码->功能仿真->综合&扫描链插入->等价性检验->静态时序分析

功能仿真:验证RTL代码设计的功能正确性,没有加入延迟信息,又叫前仿真。主要工具:Mentor的Modelsim、Synopsys 的 VCS,Candence 的 NC-Verilog。

在综合、布局布线之后,加入延迟的仿真称为后仿真。

综合:目的是将RTL代码转换成门级网表。典型的网表文件包含:单元(Cell)、引脚(Pin)、端口(Port)、网络(Net)。

- 综合输入:RTL代码、工艺库、约束

- 综合输出:Netlist门级网表(用于布局布线)、标准延迟文件(用于时序仿真)、综合后的报告

扫描链插入:扫描链插入的主要思想是在设计中添加额外的逻辑,将寄存器或触发器连接成一个或多个链条,形成扫描链。这些扫描链可以允许测试设备在运行时向芯片的内部输入测试模式信号,以便对芯片进行测试和诊断。

DFT 可测性设计:

(1)Scan Chain(扫描链),针对时序电路,测试寄存器(Flip-Flop)和组合逻辑;

(2)MBIST(Memory Bulit-in Self Test,内建自测试),测试芯片中存储资源, rom 和 ram,在设计中插入内建自测试逻辑;

(3)Boundary Scan(边界扫描),测试封装与 IO、芯片间互联,主要逻辑有 TAP Controller 和 Boundary Scanchain)、JTAG(JTAG 是boundary scan design中用到的一个基本结构)。TAP(Test Access Port)Controller 是一种常见的数字电路中的测试控制器,用于实现测试访问端口(Test Access Port)功能,通常与 JTAG(Joint Test Action Group)接口相关联。

ATPG(Automatic Test Pattern Generation,自动测试向量生成,基于扫描链,根据算法推算出应该加载到扫描链上的激励序列和期望序列,这样的序列称为测试向量);

DFT 构建硬件结构,ATPG 生成测试向量。

形式验证:属于验证范畴,从功能上对综合后的网表进行验证,常用的是等价性检验,以功能验证后的HDL设计为参照,对比综合后的网表功能,验证是否在功能上存在等价性,保证综合后没有改变原先HDL描述功能。(常用的工具Synopsys的Formality)

静态时序分析:STA 静态时序分析(Static Timing Analyse),属于验证范畴,从时序上对综合后的网表进行验证,检查电路是否存在建立时间、保持时间等违例。

注意 STA 和 形式验证的不同,STA 从时序上验证,形式验证从功能上验证。

STA 工具有 Synosys 的 Prime Time。

保证网表正确的方法:

(1)以往的方法是对网表文件进行功能仿真,但是这种方法仿真时间长,覆盖率低。

(2)常用的方法:形式验证+静态时序分析。这种方法仿真速度快,覆盖率高。

ASIC的综合与FPGA的综合有什么不同:

(1)原理相同

(2)只是映射的器件不同。FPGA将逻辑映射为LUT、RAM、REG、MUX等,而ASIC将逻辑映射成标准单元(如门电路、寄存器、RAM、ROM)。

(3)标准单元库中对于某一种功能门电路具有不同的版本,分别对应不同的驱动版本。

数字后端

布局规划->布局布线->布线图与原理图比较->设计规则检查->签名静态时序分析->GDSII

签名静态时序分析(Signature Static Timing Analysis)是一种在数字电路设计中用于评估时序性能的方法。它是一种基于静态分析的时序分析技术,用于检查设计中的信号路径是否满足时序要求。

在签名静态时序分析中,首先确定设计中的关键路径,即对设计性能有最大影响的信号路径。然后,对这些关键路径进行详细的时序分析,以确定信号在其路径上传播所需的时间,即信号的延迟。这种分析通常使用电路中的逻辑门延迟模型以及信号传输线的传输延迟模型来进行。

GDSII(Graphic Data System II)是一种电子设计自动化(EDA)领域中的标准格式,用于描述集成电路(IC)的物理布局