- 1java.security.cert.CertificateException异常的正确解决方法,亲测有效,嘿嘿嘿

- 2Git下载和安装_git 下载

- 3zookeeper is not a recognized option

- 4【11】SCI易中期刊推荐——计算机方向(中科院4区)_非oa 人工智能sci四区

- 5Pytorch实用教程:pytorch中 argmax(dim)用法详解

- 6提示词(prompt)工程指南(三):高级提示_awesome prompt

- 7Python中4种读取JSON文件和提取JSON文件内容的方法

- 8【Linux】shell编程4(break语句、continue、exit、shell的函数、返回值return)_linux break

- 9凸多边形最优三角剖分(算法设计:动态规划)_凸多边形的最优三角剖分,按照三步,采用动态规划去解决

- 10Python常用模块 之 redis:连接和操作redis数据库_python redis库

毕设分享|基于51单片机DDS信号发生器设计_pira 芯片

赞

踩

在电子通信技术日益发展的时代潮流下,直接式(DFS)和锁相式(PLL)已经不能满足生活和科研方面对于频率技术的需求。经过科研人员的不断攻坚下,直接数字频率合成器(DDS)应运而生。它现在广泛运用于移动通信、电子雷达、航天等方面。本次设计主要通过FPGA模块+单片机最小系统实现对数字信号、模拟信号的控制和输出功能,并基于此原理完成信号发生器的软件、硬件设计。

第一章 方案分析与系统设计

1.1 设计方案选型与分析

方案1:采用Qualcomm公司生产的DDS集成芯片Q2368设计信号发生器。该芯片内部包括了相位累加寄存器,波形存储器,频率控制字等模块,并且拥有灵活的频率和相位控制方式。当工作于最基本的DDS方式时,PIRA和PIRB配合即可实现,频率和相位的控制,但集成好的DDS芯片不能面向使用者进行二次开发,只能输出自带的波形。此方案也可实现DDS的设计,但该芯片的外围电路比较复杂,输出波形也不便于设计。

方案2:采用基于锁相环式的频率设计方法实现信号发生器的功能。该频率合成器可实现频率的加、减、乘、除,它的整体结构是一种闭环系统。同时此种信号发生器设计时,可采用ADI公司的ADF4113锁相环芯片来实现,锁相环控制频率在指定位数上。该芯片的功能优良,常用于设计较高分辨率、低杂散的频率合成器。它的结构简单,便于集成和小型化是较突出的优势,流行于市场上的电子、通信产品的设计。较为短板的地方在于,此方案无法实现任意波形的输出。

方案3:采用基于FPGA的直接数字式的频率设计方法实现信号发生器的功能。其基本结构包括累加寄存器和波形存储器两部分,此设计主要基于LUT查找表的原理,多个LUT组合可实现ROM查找表功能。通过FPGA芯片完成电路设计,当控制字输送进累加寄存器并进行加操作,输出控制数据可选择ROM查找表中存放的波形数据进行输出,再搭配模拟电路的方法实现波形输出,当改变波形存储器(ROM查找表)中的波形数据,并选择信号输出就可以设计出任意波形发生器。此设计方法的直接数字式结构简单、便于集成、频率分辨率相较其他方法高出很多等优点,且可实现幅度、频率、相位的数控调节。

通过上文中提到的几种设计方法的对比,第一种设计方案直接使用DDS集成芯片,但是它的但这种设计存在诸多的缺陷,例如不够灵活、模块固定、不容易更换,只能输出出厂时在其内部设计好的波形数据,使用者再次设计自己想要的波形,因此不选择方案一。第二种设计方案,在设计中的分辨率要低于第三种设计方案,无法实现任意波形的设计,并且它使用时锁定的时间相对而言比较长,故不方便进行设计快速锁定的信号发生器件。方案三,此设计方法的直接数字式结构简单、便于集成、频率分辨率相较其他方法高出很多,本次设计最高频率达到10MHz,在使用时功耗方面也具有相对较低的突出点,同时在理论功能上也能够实现任意波形的组合和选择输出,因此本设计采用此方案三。

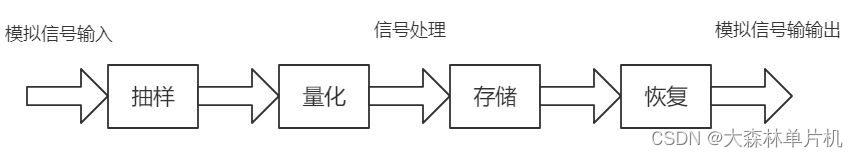

1.2 DDS结构和设计方法

DDS技术是基于奈奎斯特取样定理,其工作的原理如图2.1所示,利用相位累加原理从相位的方面考虑研究波形信号的基本组织结构和工作原理。这次以正弦波为例子,通过正弦波线性增加的相位即可对它进行波形信号取样、波形信号量化、数据编码一系列操作实现连续的模拟信号转换成离散的数字信号,并将生成的二进制数字信号码存储在波形存储器(ROM/RAM)中,就相当于在内部存储器中存储了一个完整的周期性波形幅度值。当需要一个连续的正弦波时,可以通过控制频率控制字,来达到以相位累加器的相位变化量控制采样点数量的功能。同时,从正弦波的相位与时间的角度来看,角频率ω=△φ·△t,故在采样频率恒定的条件下,在内嵌模块中把波形存储器中的波形幅度数据并周期性地识别读出并输出可视的模拟信号波形。