中航证券2024 AI智算时代已至,算力芯片加速升级_中航证券《ai智算时代已至,算力芯片加速升级》

赞

踩

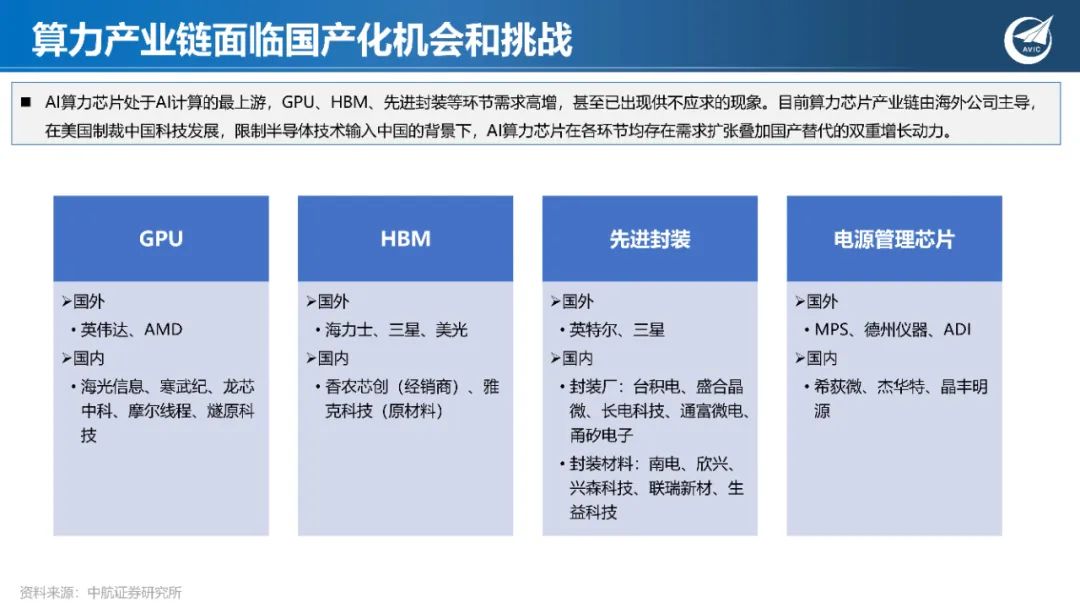

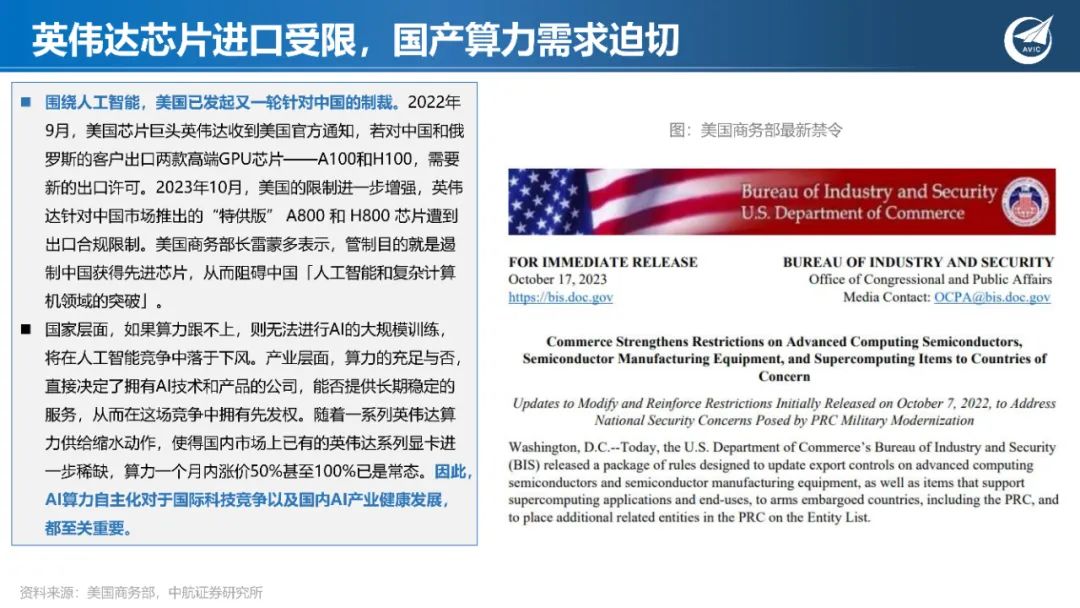

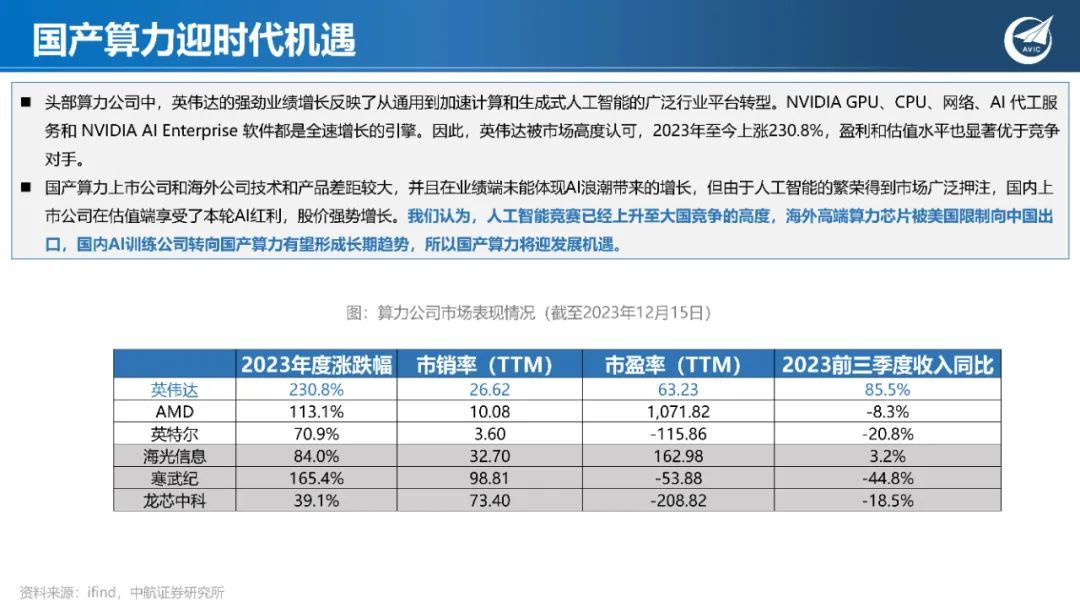

一、AI处史上最长繁荣期,算力国产化需求迫切

AI正处史上最长繁荣大周期

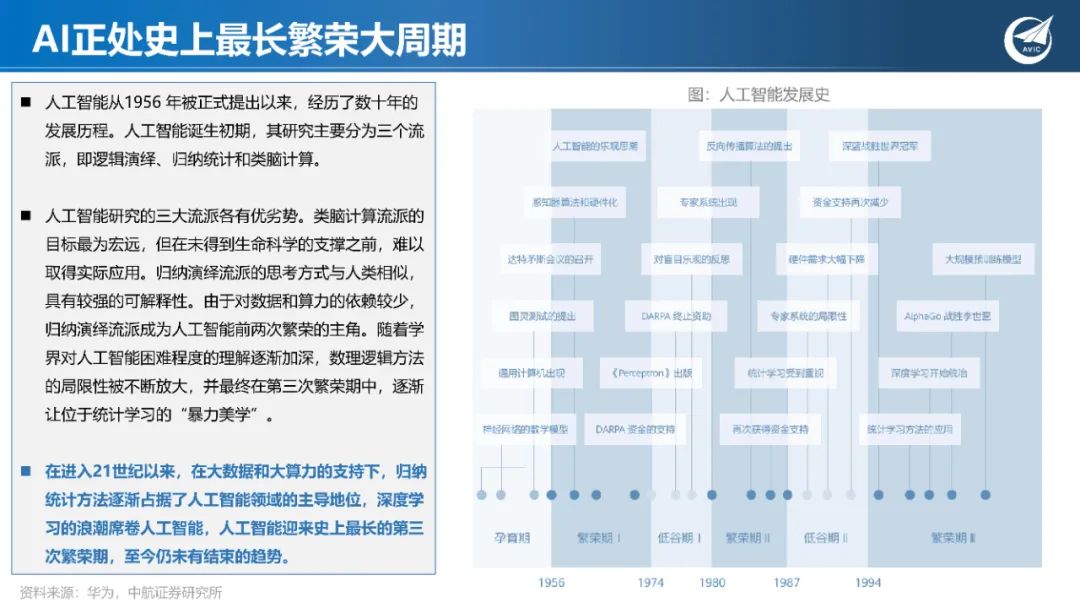

人工智能从1956 年被正式提出以来,经历了数十年的 发展历程。人工智能诞生初期,其研究主要分为三个流 派,即逻辑演绎、归纳统计和类脑计算。 人工智能研究的三大流派各有优劣势。类脑计算流派的 目标最为宏远,但在未得到生命科学的支撑之前,难以 取得实际应用。归纳演绎流派的思考方式与人类相似, 具有较强的可解释性。由于对数据和算力的依赖较少, 归纳演绎流派成为人工智能前两次繁荣的主角。随着学 界对人工智能困难程度的理解逐渐加深,数理逻辑方法 的局限性被不断放大,并最终在第三次繁荣期中,逐渐 让位于统计学习的“暴力美学”。 在进入21世纪以来,在大数据和大算力的支持下,归纳 统计方法逐渐占据了人工智能领域的主导地位,深度学 习的浪潮席卷人工智能,人工智能迎来史上最长的第三 次繁荣期,至今仍未有结束的趋势。

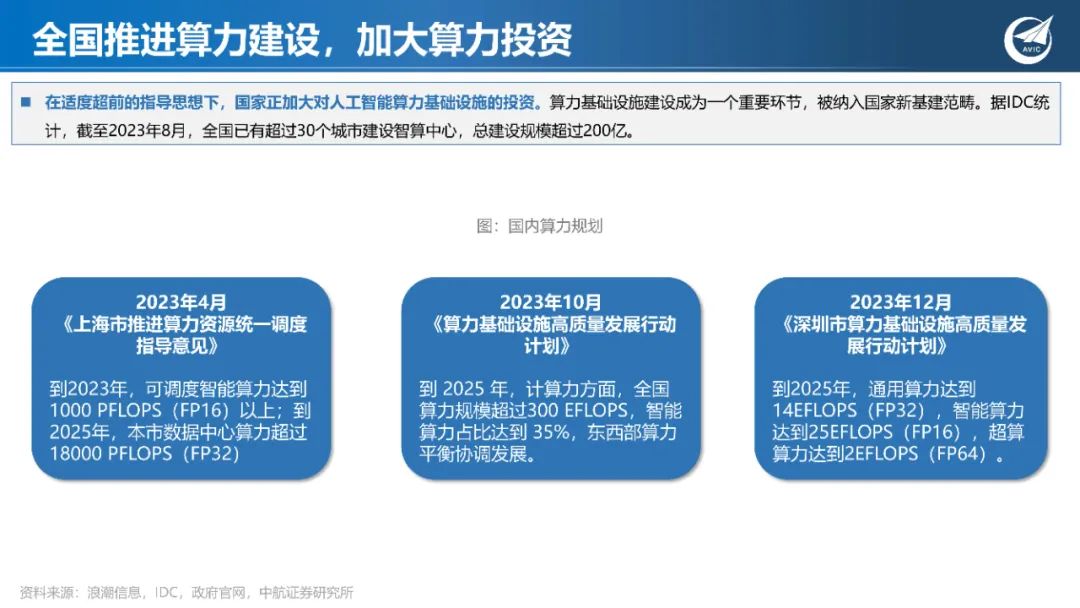

智能算力规模将快速增长

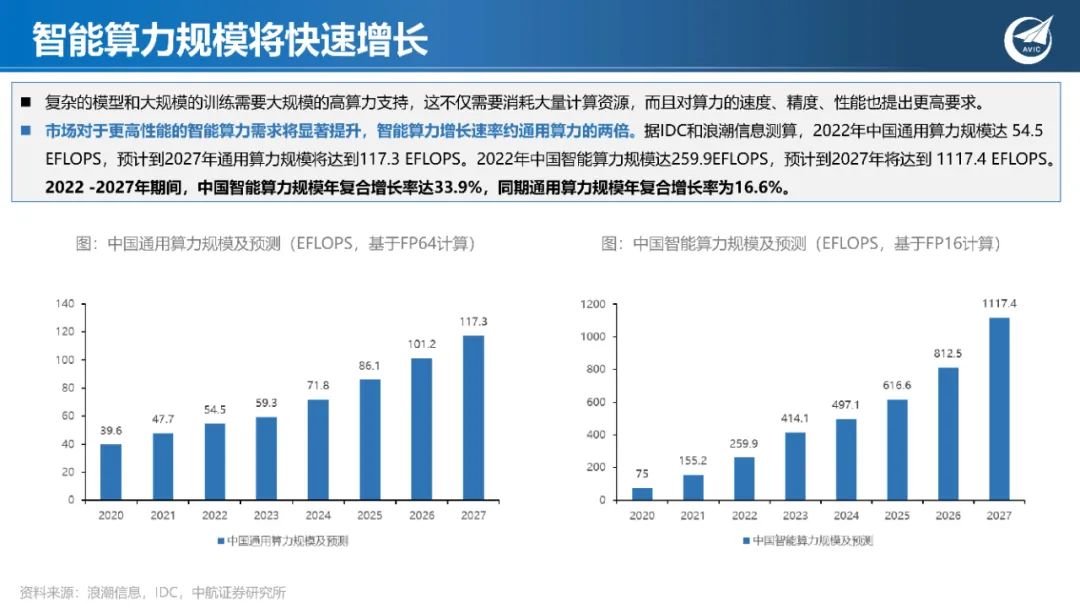

复杂的模型和大规模的训练需要大规模的高算力支持,这不仅需要消耗大量计算资源,而且对算力的速度、精度、性能也提出更高要求。 市场对于更高性能的智能算力需求将显著提升,智能算力增长速率约通用算力的两倍。据IDC和浪潮信息测算,2022年中国通用算力规模达 54.5 EFLOPS,预计到2027年通用算力规模将达到117.3 EFLOPS。2022年中国智能算力规模达259.9EFLOPS,预计到2027年将达到 1117.4 EFLOPS。 2022 -2027年期间,中国智能算力规模年复合增长率达33.9%,同期通用算力规模年复合增长率为16.6%。

AI服务器需求旺盛

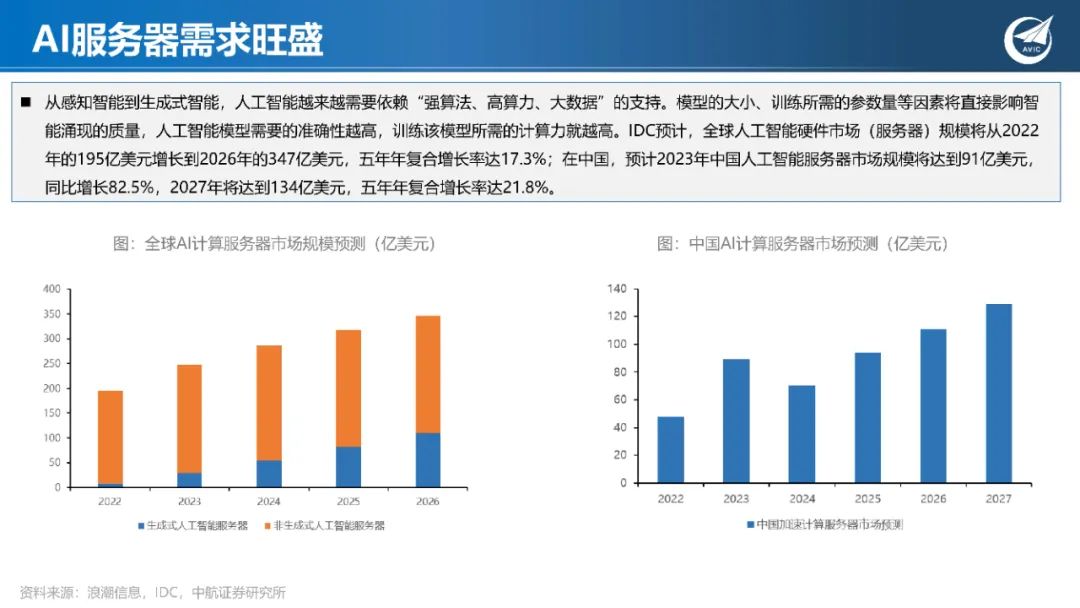

从感知智能到生成式智能,人工智能越来越需要依赖“强算法、高算力、大数据”的支持。模型的大小、训练所需的参数量等因素将直接影响智 能涌现的质量,人工智能模型需要的准确性越高,训练该模型所需的计算力就越高。IDC预计,全球人工智能硬件市场(服务器)规模将从2022 年的195亿美元增长到2026年的347亿美元,五年年复合增长率达17.3%;在中国,预计2023年中国人工智能服务器市场规模将达到91亿美元, 同比增长82.5%,2027年将达到134亿美元,五年年复合增长率达21.8%。

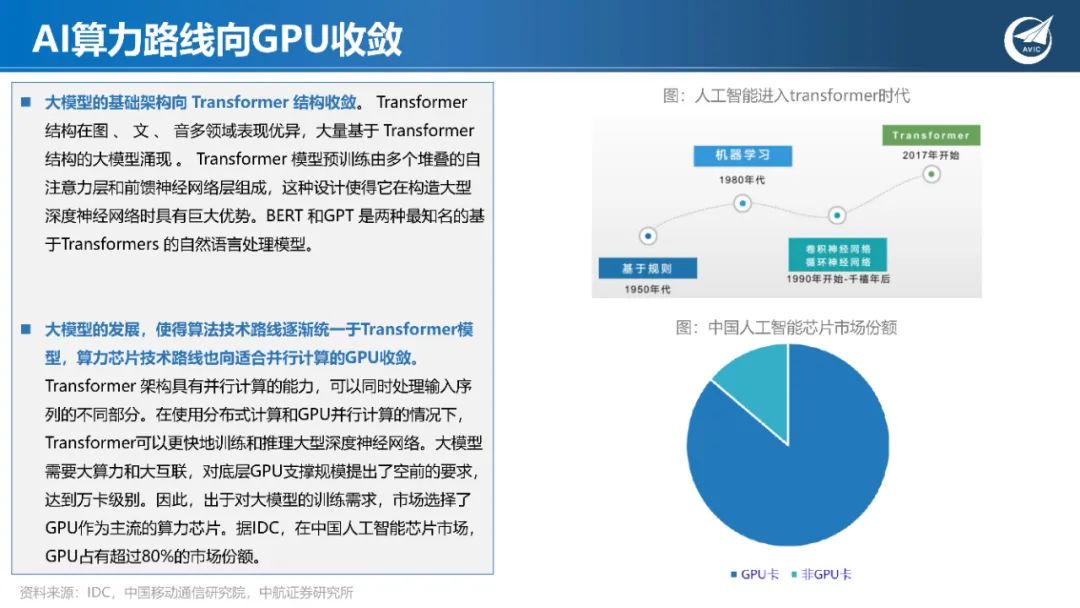

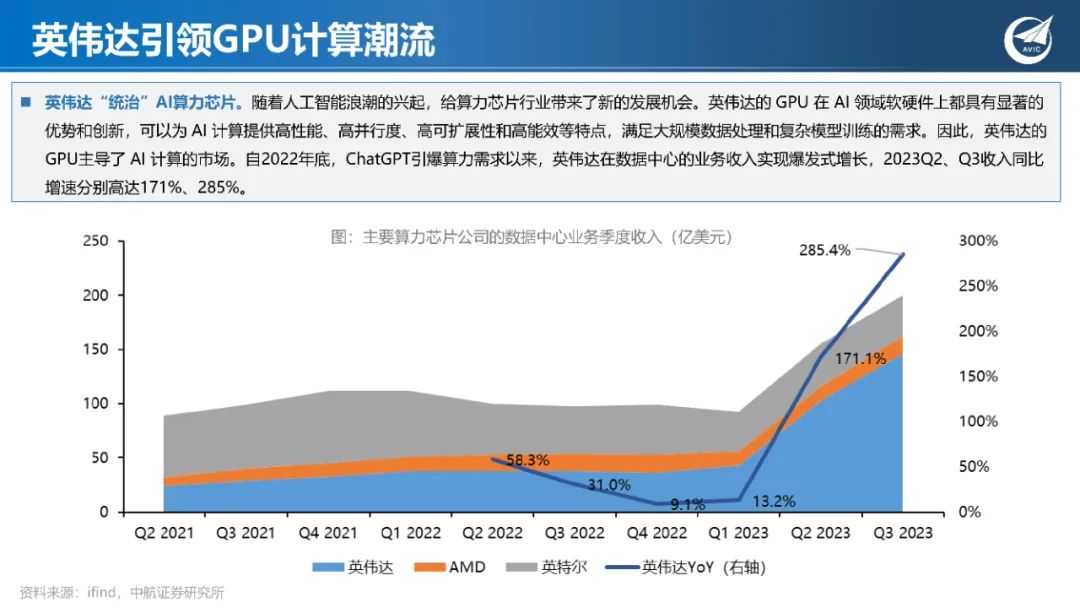

二、AI技术收敛,GPU主宰算力芯片

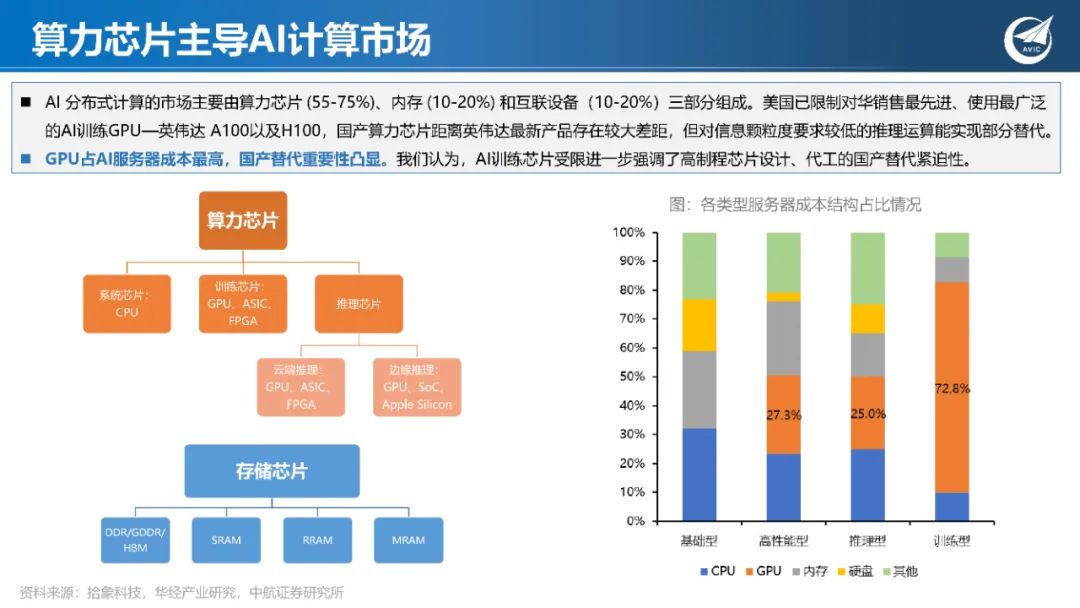

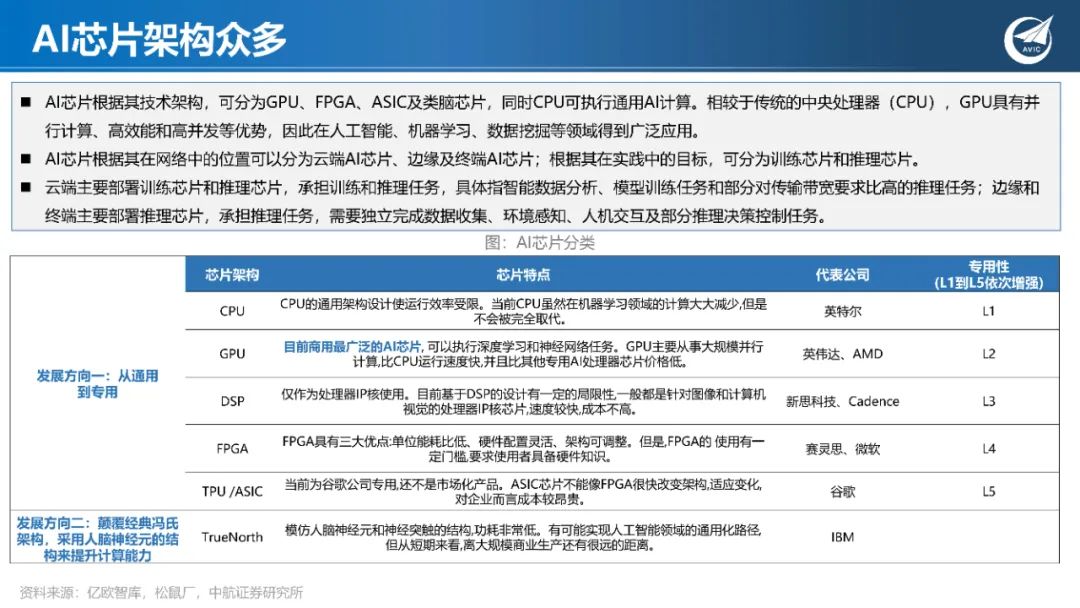

AI芯片架构众多

AI芯片根据其技术架构,可分为GPU、FPGA、ASIC及类脑芯片,同时CPU可执行通用AI计算。相较于传统的中央处理器(CPU),GPU具有并 行计算、高效能和高并发等优势,因此在人工智能、机器学习、数据挖掘等领域得到广泛应用。 AI芯片根据其在网络中的位置可以分为云端AI芯片、边缘及终端AI芯片;根据其在实践中的目标,可分为训练芯片和推理芯片。 云端主要部署训练芯片和推理芯片,承担训练和推理任务,具体指智能数据分析、模型训练任务和部分对传输带宽要求比高的推理任务;边缘和 终端主要部署推理芯片,承担推理任务,需要独立完成数据收集、环境感知、人机交互及部分推理决策控制任务。

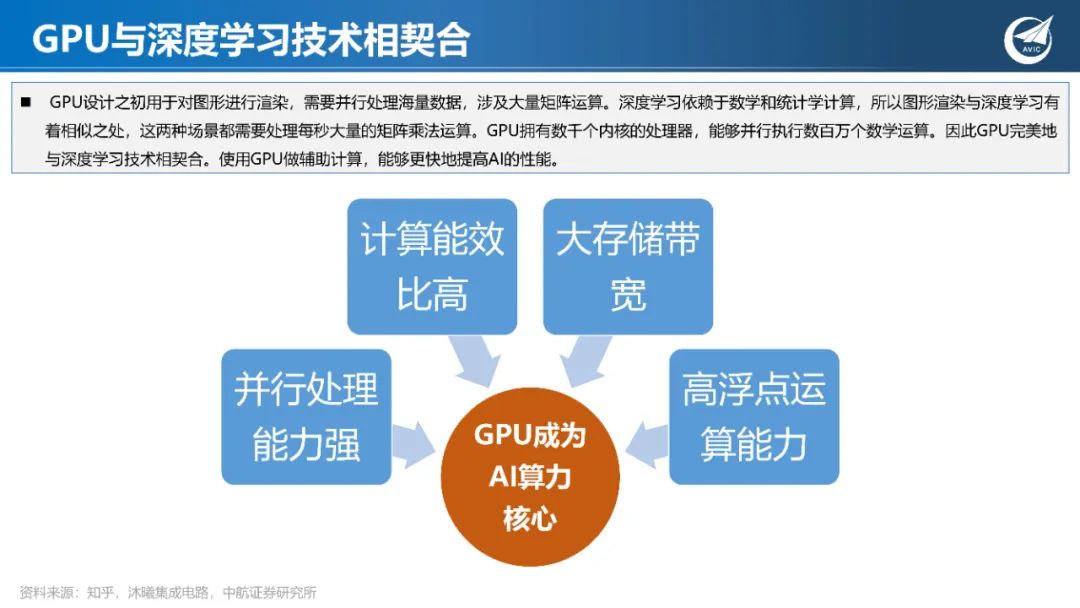

GPU与深度学习技术相契合

GPU设计之初用于对图形进行渲染,需要并行处理海量数据,涉及大量矩阵运算。深度学习依赖于数学和统计学计算,所以图形渲染与深度学习有 着相似之处,这两种场景都需要处理每秒大量的矩阵乘法运算。GPU拥有数千个内核的处理器,能够并行执行数百万个数学运算。因此GPU完美地 与深度学习技术相契合。使用GPU做辅助计算,能够更快地提高AI的性能。

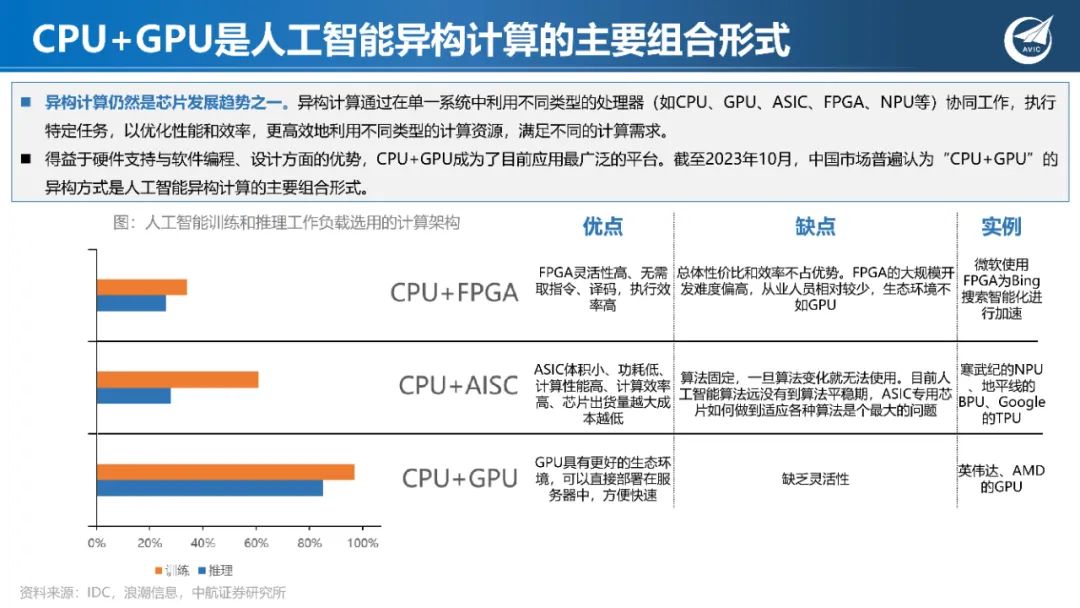

CPU+GPU是人工智能异构计算的主要组合形式

异构计算仍然是芯片发展趋势之一。异构计算通过在单一系统中利用不同类型的处理器(如CPU、GPU、ASIC、FPGA、NPU等)协同工作,执行 特定任务,以优化性能和效率,更高效地利用不同类型的计算资源,满足不同的计算需求。 得益于硬件支持与软件编程、设计方面的优势,CPU+GPU成为了目前应用最广泛的平台。截至2023年10月,中国市场普遍认为“CPU+GPU”的 异构方式是人工智能异构计算的主要组合形式。

三、“AI信创”驱动,培育国产算力生态

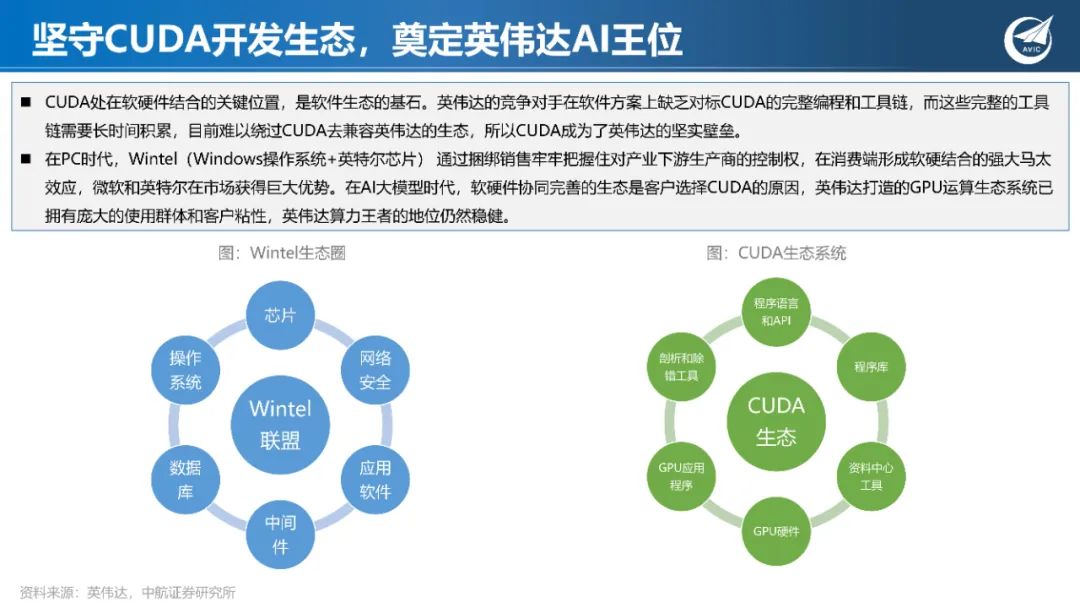

GPU行业需跨越CUDA横亘

英伟达CUDA已经实现了与算法工程师、芯片客户的强绑定,众多算法工程师已经习惯了一套工具库、一套编程语言,向外迁移存在不习惯等问题。 所以很多算力芯片硬件厂商选择了兼容CUDA的路线——使硬件能够直接用CUDA调动起来,以降低用户的硬件迁移痛点。 兼容CUDA需要巨大时间和成本投入。据集微网,兼容CUDA涉及50个驱动、50个编译器、50个数学库、300个应用层工程师,3-5年的时间。功 能的验证,用户的培养需要额外3-5年,每年还要至少开支1000万-3000万元资助外部开发者。 从头部AI厂商布局来看,英伟达竞争者AMD选择兼容CUDA+自研原生“两条腿”并行,英伟达客户谷歌、Meta、亚马逊等均已推出自己的AI芯 片。我们认为,国产GPU在起步阶段兼容CUDA生态更容易发展,易于生存。在美国技术封锁的大背景之下,“AI信创”为国产算力芯片提供了 市场窗口,远期国产GPU还是需要发展原生生态。

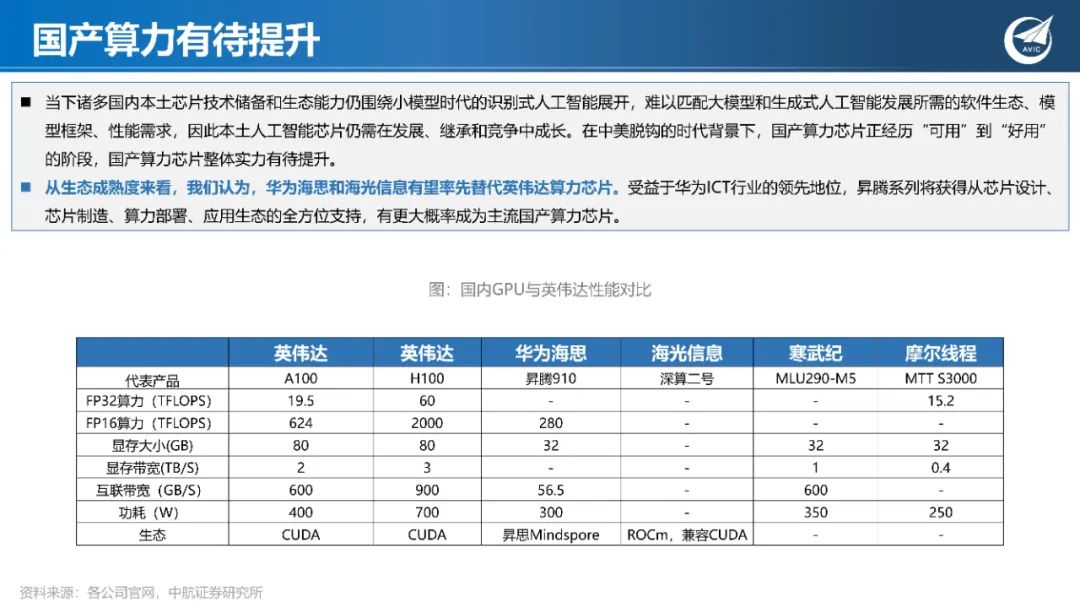

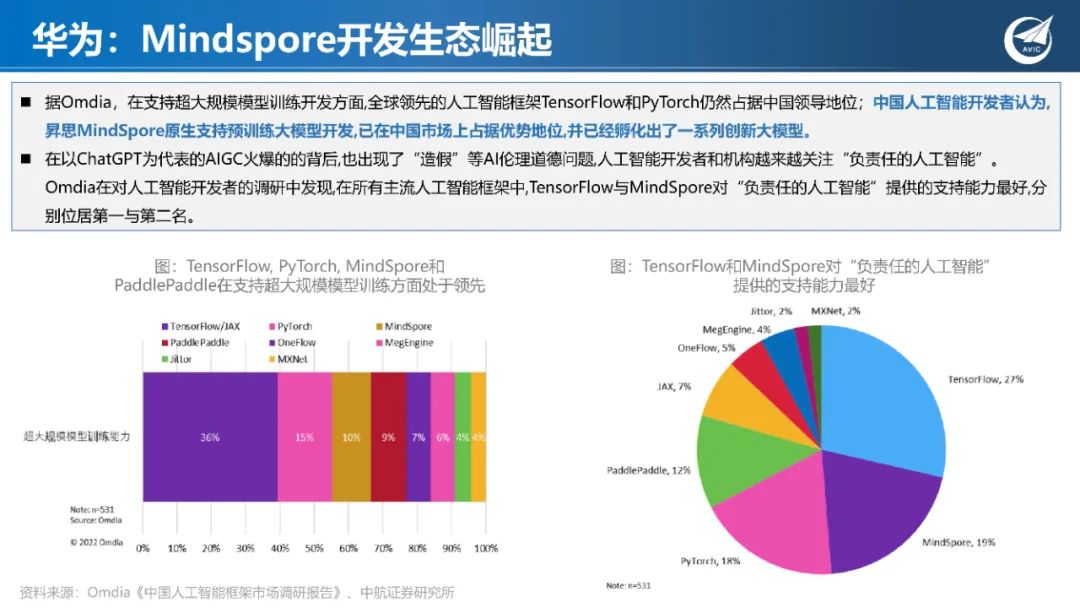

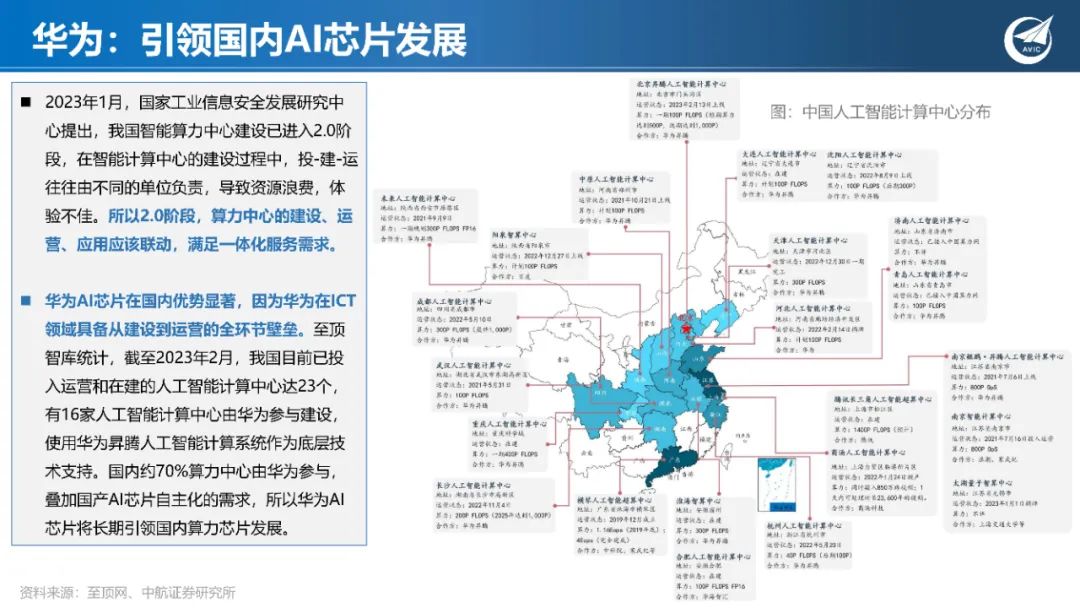

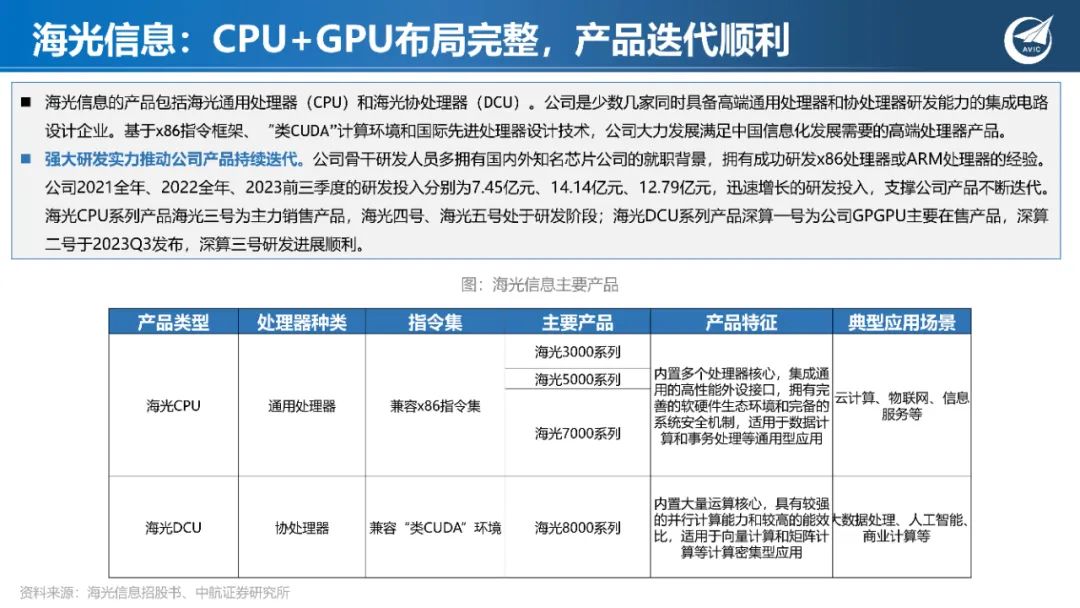

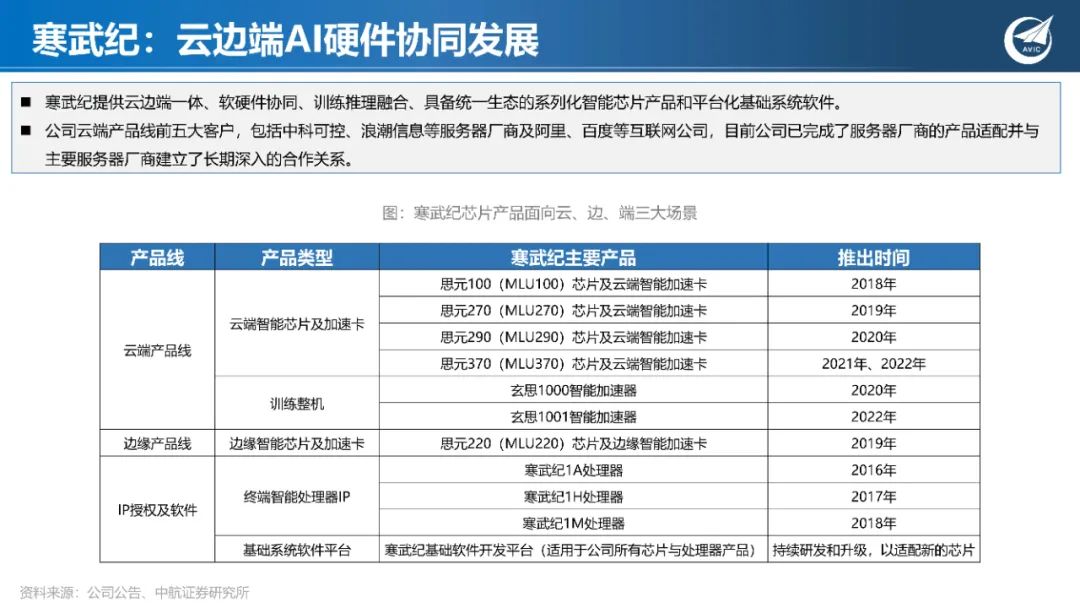

国产算力有待提升

当下诸多国内本土芯片技术储备和生态能力仍围绕小模型时代的识别式人工智能展开,难以匹配大模型和生成式人工智能发展所需的软件生态、模 型框架、性能需求,因此本土人工智能芯片仍需在发展、继承和竞争中成长。在中美脱钩的时代背景下,国产算力芯片正经历“可用”到“好用” 的阶段,国产算力芯片整体实力有待提升。 从生态成熟度来看,我们认为,华为海思和海光信息有望率先替代英伟达算力芯片。受益于华为ICT行业的领先地位,昇腾系列将获得从芯片设计、 芯片制造、算力部署、应用生态的全方位支持,有更大概率成为主流国产算力芯片。

四、HBM解决GPU内存危机,成为存储下一主战场

AI算力刺激更多存储器用量

AI服务器存储容量倍增,带动存储器需求成长。据TrendForce,AI服务器需要配置更多DRAM、SSD和HBM等大容量存储以应对日益复杂的大模型所 带来的海量数据。当前普通服务器DRAM普遍配置约为500至600GB,而AI服务器DRAM 配置可达1.2至1.7TB,是普通服务器的二到三倍。此外,相 较于一般服务器而言,AI服务器多增加GPGPU的使用,因此以NVIDIA A100 80GB配置4或8张计算,HBM用量约为320~640GB。未来在AI模型逐渐复 杂化的趋势下,将刺激更多的存储器用量,并同步带动 Server DRAM、SSD 以及 HBM 的需求成长。

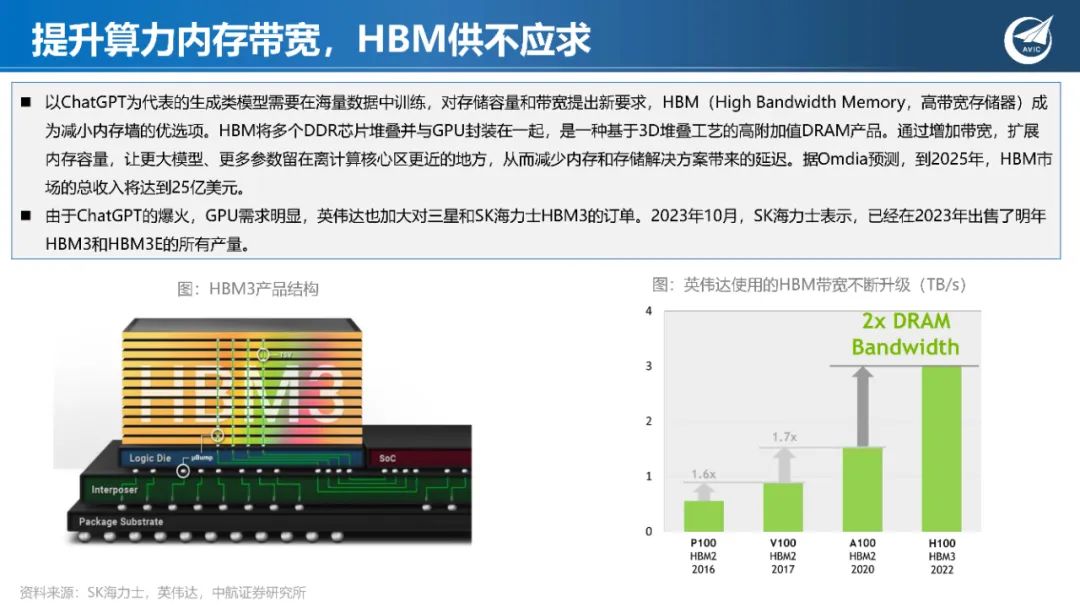

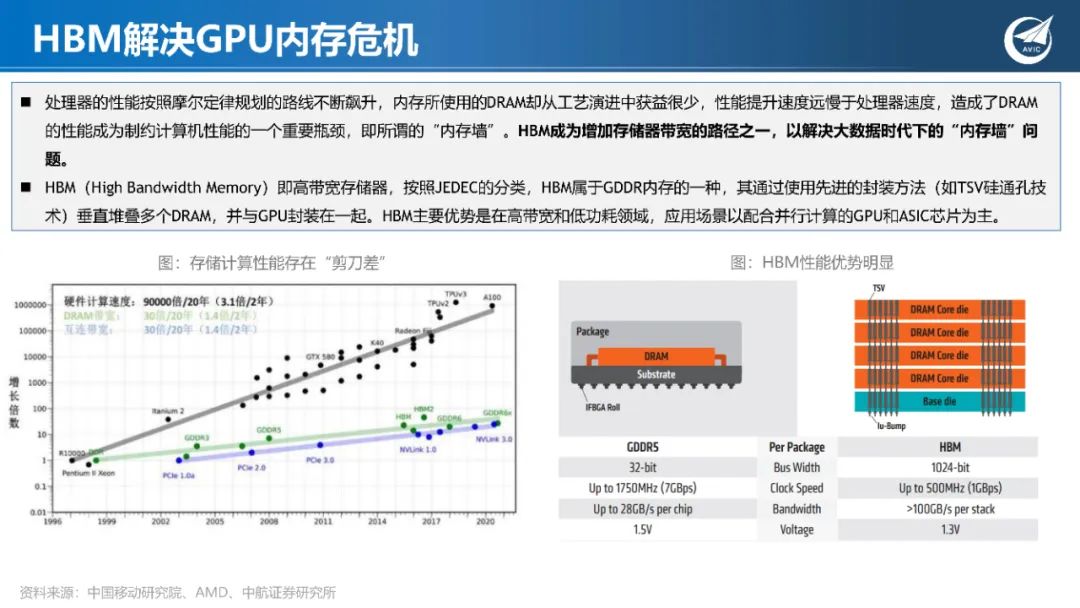

HBM解决GPU内存危机

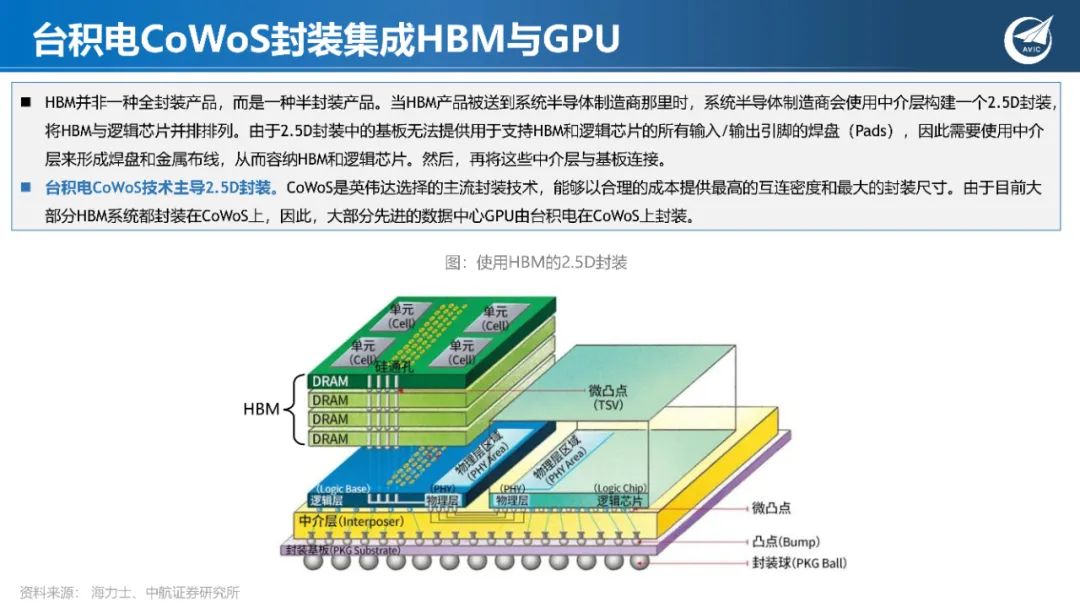

处理器的性能按照摩尔定律规划的路线不断飙升,内存所使用的DRAM却从工艺演进中获益很少,性能提升速度远慢于处理器速度,造成了DRAM 的性能成为制约计算机性能的一个重要瓶颈,即所谓的“内存墙”。HBM成为增加存储器带宽的路径之一,以解决大数据时代下的“内存墙”问 题。 HBM(High Bandwidth Memory)即高带宽存储器,按照JEDEC的分类,HBM属于GDDR内存的一种,其通过使用先进的封装方法(如TSV硅通孔技 术)垂直堆叠多个DRAM,并与GPU封装在一起。HBM主要优势是在高带宽和低功耗领域,应用场景以配合并行计算的GPU和ASIC芯片为主。

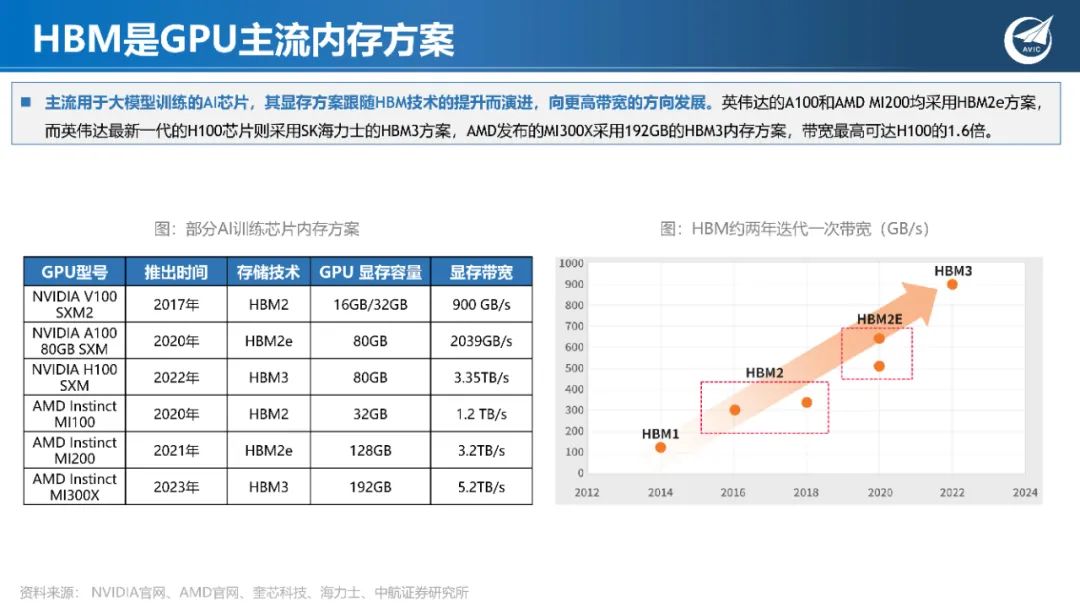

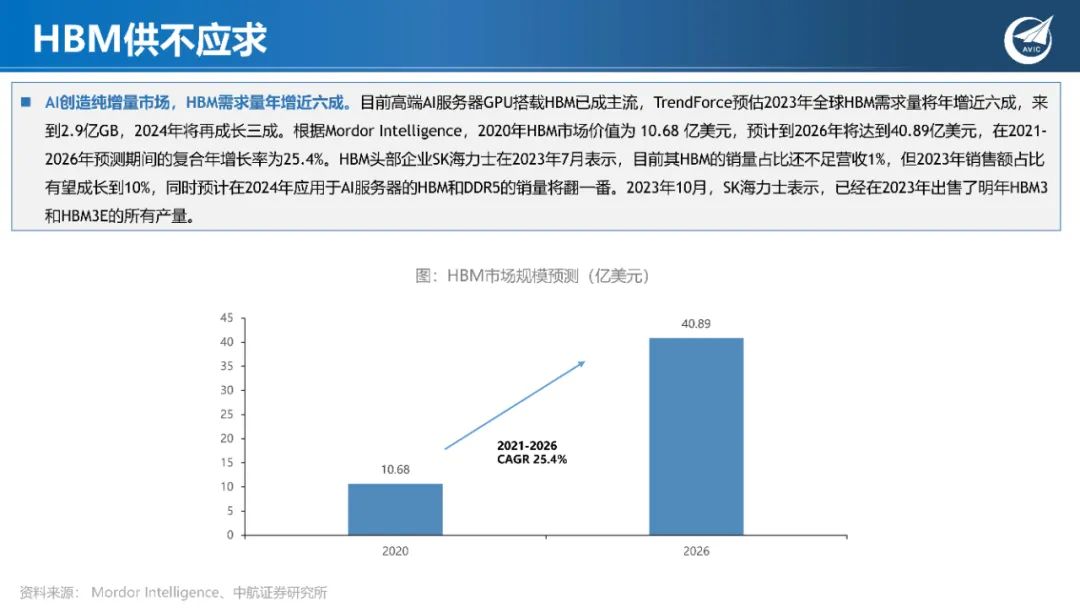

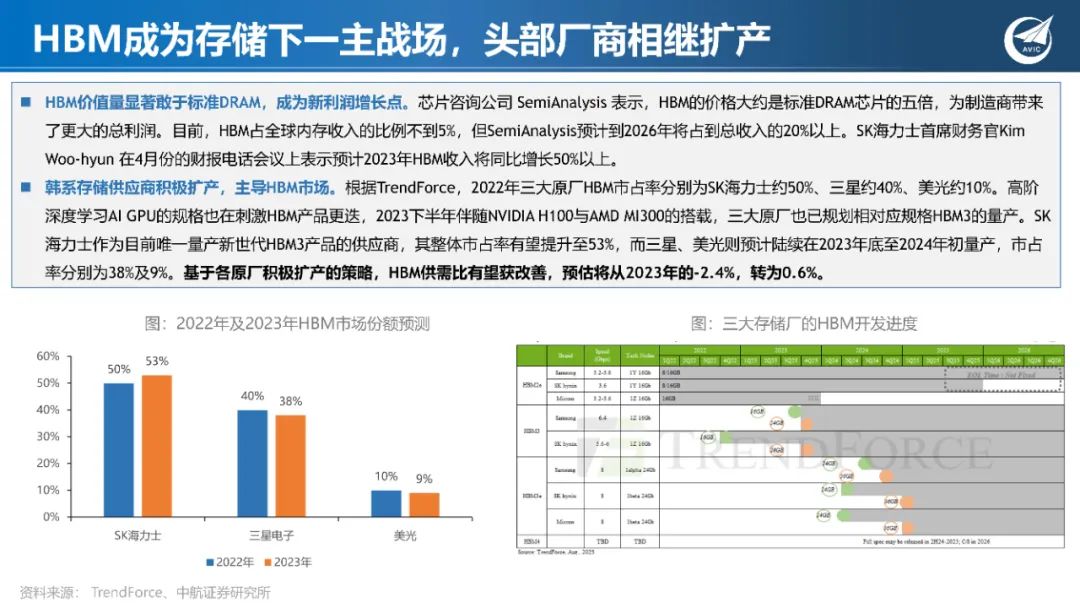

HBM供不应求

AI创造纯增量市场,HBM需求量年增近六成。目前高端AI服务器GPU搭载HBM已成主流,TrendForce预估2023年全球HBM需求量将年增近六成,来 到2.9亿GB,2024年将再成长三成。根据Mordor Intelligence,2020年HBM市场价值为 10.68 亿美元,预计到2026年将达到40.89亿美元,在2021- 2026年预测期间的复合年增长率为25.4%。HBM头部企业SK海力士在2023年7月表示,目前其HBM的销量占比还不足营收1%,但2023年销售额占比 有望成长到10%,同时预计在2024年应用于AI服务器的HBM和DDR5的销量将翻一番。2023年10月,SK海力士表示,已经在2023年出售了明年HBM3 和HBM3E的所有产量。

五、异构计算时代,先进封装战略地位凸显

异构计算时代,先进封装战略地位凸显

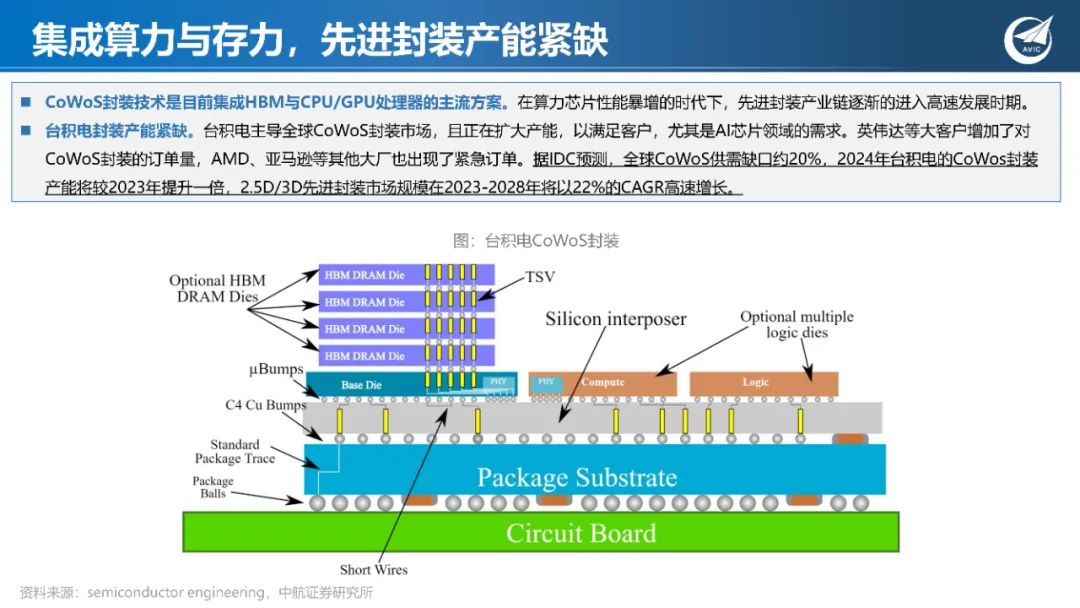

异构集成(Heterogeneous Integration),即横向和纵向连接多个半导体,可将更多的晶体管装在一个更小的半导体上,准确地说是在更小的半导 体封装内,从而提供比其各部分之和更大的功用。CPU+GPU是人工智能异构计算的主要组合形式,英伟达的Grace Hopper超级芯片通过异构集成 CPU、GPU以及存储器,实现芯片更高带宽的互连,能够承担更大的数据集、更复杂的模型和新的工作负载。

先进封装成为突破“摩尔定律”局限的技术。先进封装技术充当着半导体器件与系统之间的桥梁,是实现异构集成的关键技术,因此,这种连接 方法变得越来越重要。先进封装技术本身已成为一种系统解决方案,半导体头部设计、制造商均通过此方法,在摩尔定律放缓的时代,从系统层 面继续提升芯片性能。

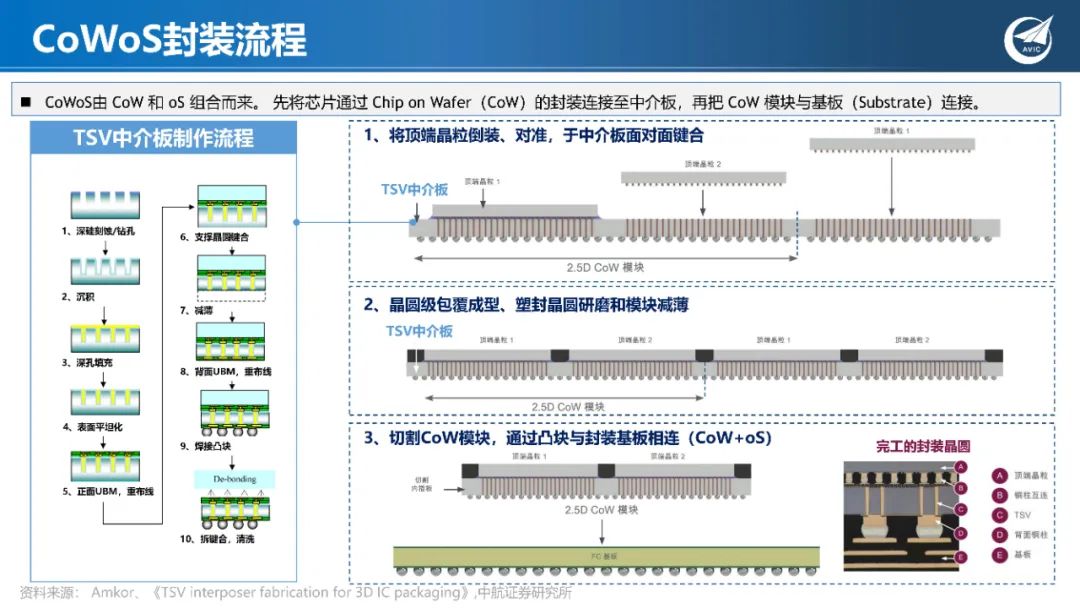

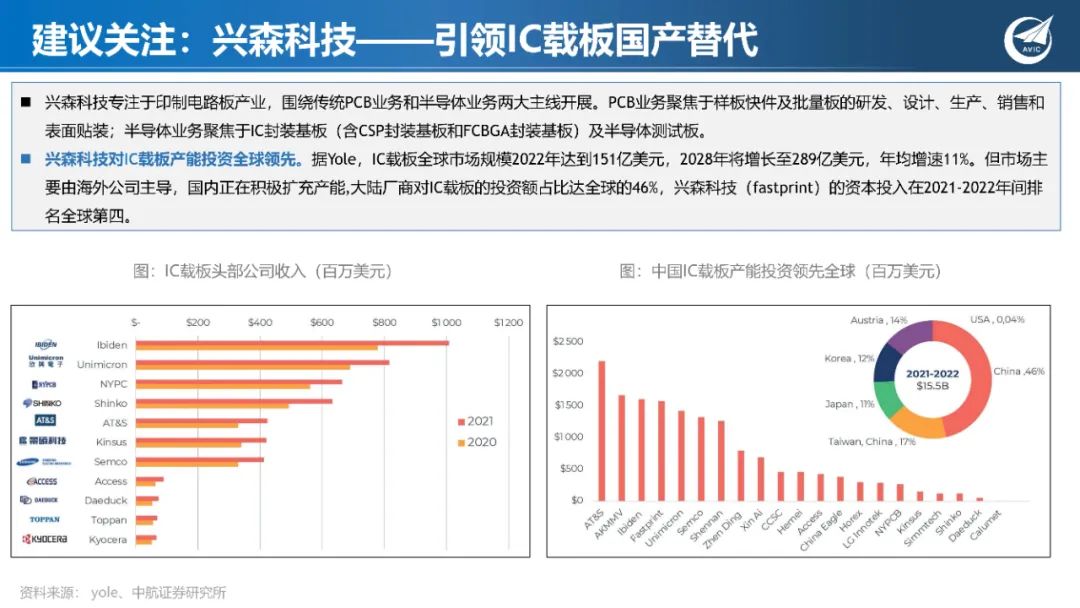

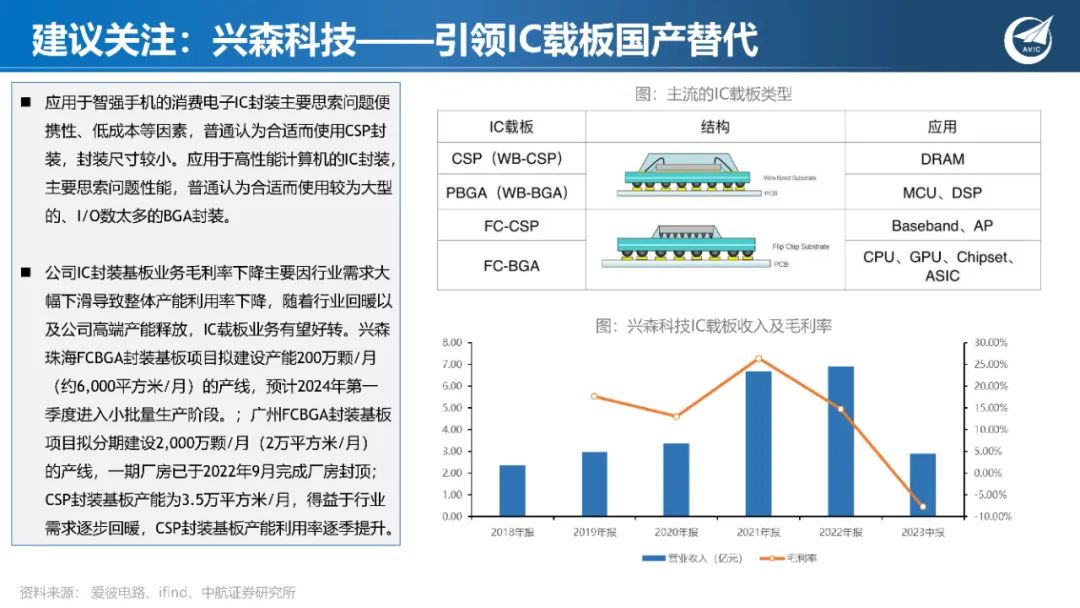

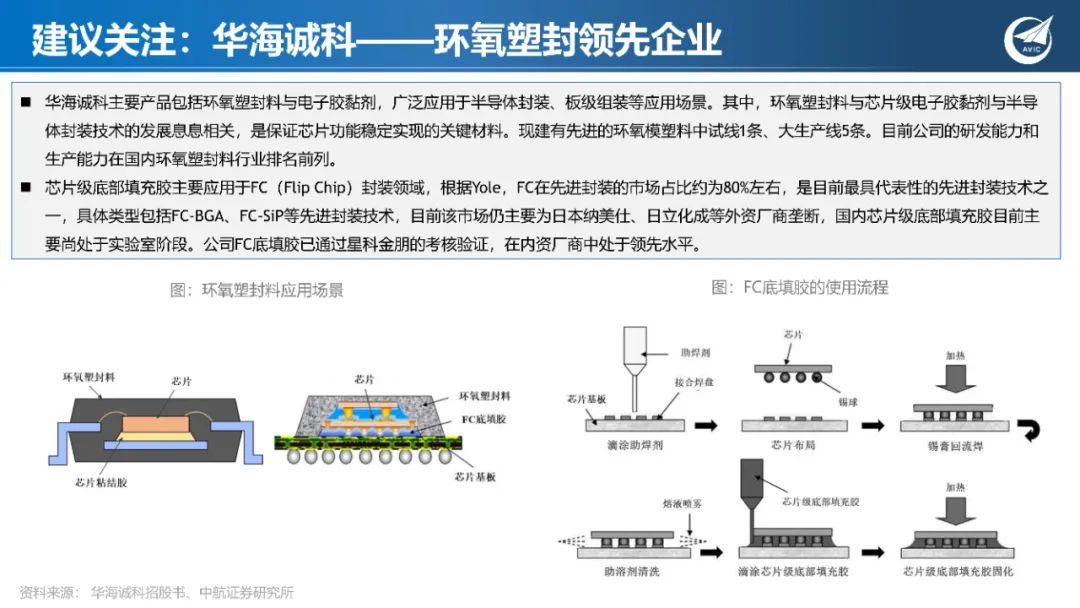

顺应AI算力芯片发展,封装技术持续创新

自2020年开始,先进封装进入技术融合期,成为关键的系统级解决方案。不仅需要借助多项技术将各类芯片集成到同一封装内,还需要在整合系 统时将多个部分连接至同一模块。AI计算芯片融合了多项先进封装技术,HBM应用TSV堆叠技术获得超高带宽,而为了将HBM和GPU集成,CoWoS 封装技术被深度开发。因此,封装技术将成为提供整体系统解决方案的重要手段 。海力士判断,未来各公司将依赖封装技术助力其成为半导体行 业的领军者。

顺应AI算力芯片发展,封装技术持续创新

随着封装技术的发展,近十年中,重新分配层(RDL)、倒片封装(Flip Chip)和硅穿孔(TSV)等封装技术得到了积极广泛的应用,在硅晶圆或 芯片堆叠结构晶圆中进行工艺处理,大幅提高了产品的性能和容量。SK海力士凭借业界领先的TSV堆叠技术引领了市场发展,这其中包括HBM封装 存储器解决方案,以及用于服务器的高密度存储器(HDM)三维堆叠技术。同时,海力士持续迭代封装技术,研发了批量回流模制底部填充、混 合键合、扇出型晶圆级封装等技术,以进一步提升了HBM的堆叠层数。

六、电源技术提升计算能效,背面供电蓄势待发

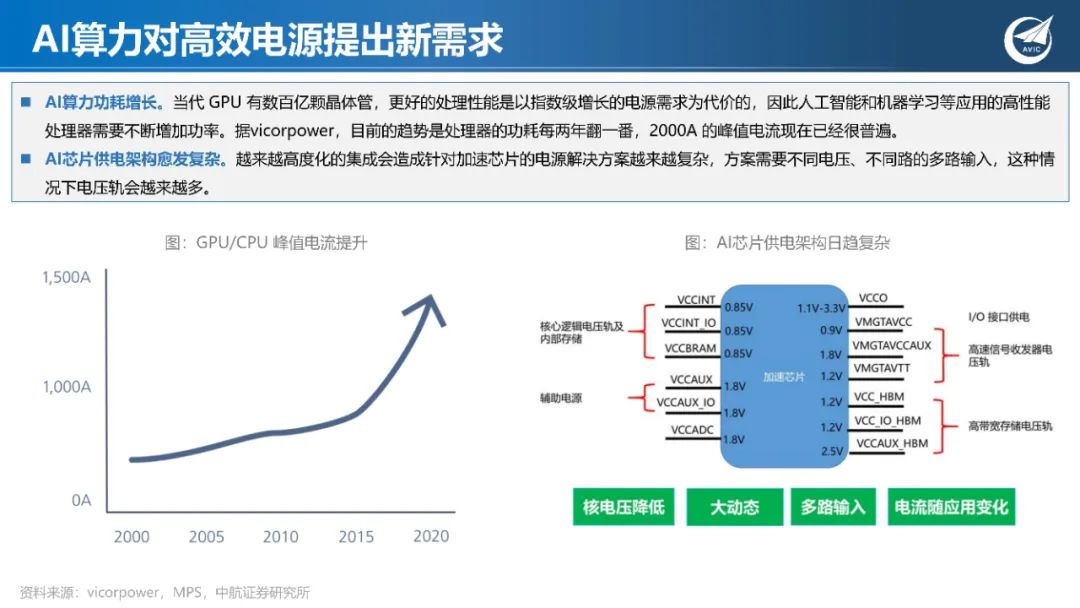

AI算力对高效电源提出新需求

据高性能电源解决方案供应商MPS测算,云计算领域的电源市场规模增长迅速,从2015年8亿美元,至2021年增长四倍,达到40亿美元。 云计算模拟电源市场由CPU服务器电路、GPU服务器电路、机架电路构成,市场规模分别为10亿美元、10亿美元、20亿美元。CPU服务器中, CPU供电、存储器供电、PoL(负载点)供电、eFuse(电子保险丝)市场规模分别为6亿、2.8亿美元、0.6亿美元、0.6亿美元。

服务器电源架构转向48V

48V直流供电能够降低服务器配电损耗。据松下测 试结果,计算配电路径的电阻为0.1mΩ时的配电损 耗,12V时为100W,48V时为6.25W,会出现16 倍的计算差异。在各家公司都在积极致力于节省电 力消耗中,谷歌公司于2016年率先引入了48V直流 供电的手法。

算力电路的供电设计拥有较高壁垒

典型48V电源架构包含一个 AC/DC 前端,负责生成 48V 直流电。该直流电会被输送至DC/DC 变换器,在这里电压被转换成 12V 中间母线结构。 然后将 12V 母线电压分配至板上多个负载点(PoL)变换器中,为内核CPU、GPU等提供电源。 大多数内核芯片或子电路所需的电压范围为 1V-3.3V,电流范围却为几十毫安至数百安培。通常,处理从几十毫安到数百安培应用程序的传统方式 会采用离散模拟解决方案。离散模拟解决方案的构建块由一个控制器 IC 和一对外部 MOSFET 或一个驱动 MOSFET(DrMOS)IC 组成。由于内核 芯片的电源轨对时序、电压精度、裕量和检测能力的设计要求非常严格,因此存在较大的设计壁垒。

七、报告节选