- 1IOS学习笔记07---C语言函数-scanf函数

- 2Rust编程入门教程

- 3企业级大数据安全架构(十)DBeaver连接Hive的Kerberos认证配置_dbeaver怎么配置keytab

- 4华为OD机考统一考试C卷 找朋友(C++ Java JavaScript Python)_华为机试题java c卷

- 5YOLOv8 | 有效涨点,添加GAM注意力机制,使用Wise-IoU有效提升目标检测效果(附报错解决技巧,全网独家)_yolov8添加gaw注意力机制

- 6博客阅读:图解Transformer(The Illustrated Transformer)

- 7从外包辞职10000小时后,我走进了字节跳动····_字节外包辞职

- 8求助,为什么navicat查询结果不能分页_navicat 没有分页

- 9SENet(Squeeze-and-Excitation Network)注意力机制_senet注意力

- 10Logseq电脑端+安卓端同步gitee或github_logseq安卓

2FSK调制解调器Verilog代码Quartus仿真_multisim中2fsk器件

赞

踩

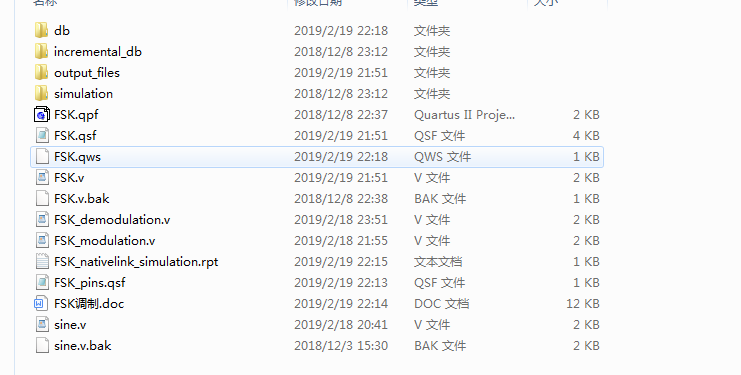

名称:2FSK调制解调器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

2FSK调制解调器

1、设计实现2FSK调制功能,2FSK调制波形通过DA芯片输出,在示波器观察波形

2、将DA芯片输出的模拟信号再接回板子上的AD芯片的输入端

3、AD芯片将模拟信号数字化后,再对2FSK波形进行解调,能正确解调出原信号

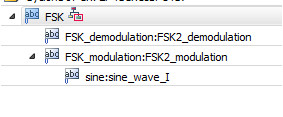

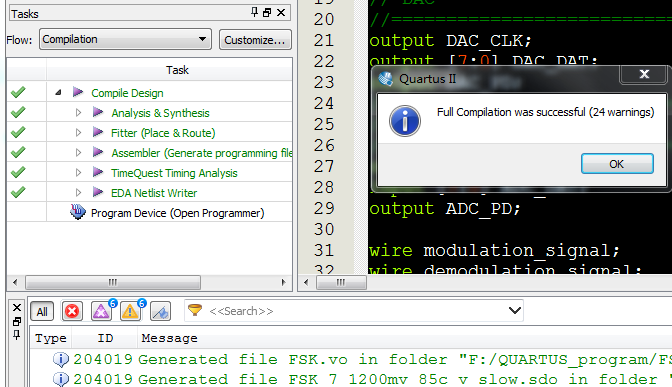

1.工程文件

2.程序代码

3.程序运行

4.程序仿真

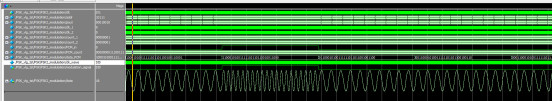

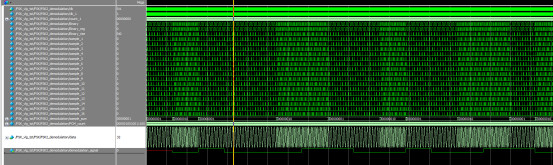

2FSK调制仿真

图中最后两行分别为调制信号和2FSK调制以后的波形

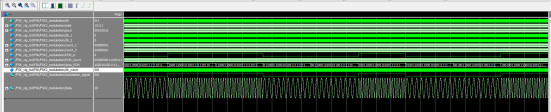

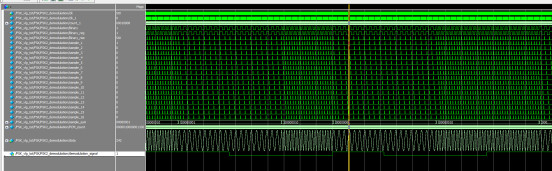

2FSK解调仿真

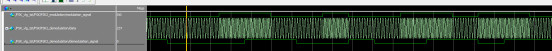

图中最后两行分别为输入的2FSK调制波形和解调以后的波形,可以看到解调信号相对2FSK调制波形有延迟

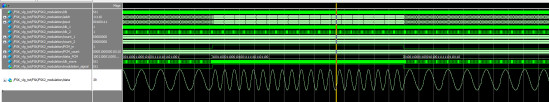

下图中从上到下依次为调制信号,2FSK调制波形,解调信号,可以看到解调信号相对原始调制信号有延迟

![]()

附:管脚约束

set_location_assignment PIN_11 -to clk50

set_location_assignment PIN_B8 -to rst_n

set_location_assignment PIN_W6 -to DAC_CLK

set_location_assignment PIN_V5 -to DAC_PD

set_location_assignment PIN_AA2 -to ADC_CLK

set_location_assignment PIN_AB2 -to ADC_PD

set_location_assignment PIN_W7 -to DAC_DAT[0]

set_location_assignment PIN_V7 -to DAC_DAT[1]

set_location_assignment PIN_W8 -to DAC_DAT[2]

set_location_assignment PIN_V8 -to DAC_DAT[3]

set_location_assignment PIN_W9 -to DAC_DAT[4]

set_location_assignment PIN_V9 -to DAC_DAT[5]

set_location_assignment PIN_W10 -to DAC_DAT[6]

set_location_assignment PIN_V10 -to DAC_DAT[7]

set_location_assignment PIN_Y3 -to ADC_DAT[0]

set_location_assignment PIN_AB3 -to ADC_DAT[1]

set_location_assignment PIN_Y4 -to ADC_DAT[2]

set_location_assignment PIN_AA5 -to ADC_DAT[3]

set_location_assignment PIN_Y5 -to ADC_DAT[4]

set_location_assignment PIN_AA6 -to ADC_DAT[5]

set_location_assignment PIN_Y6 -to ADC_DAT[6]

set_location_assignment PIN_AA7 -to ADC_DAT[7]

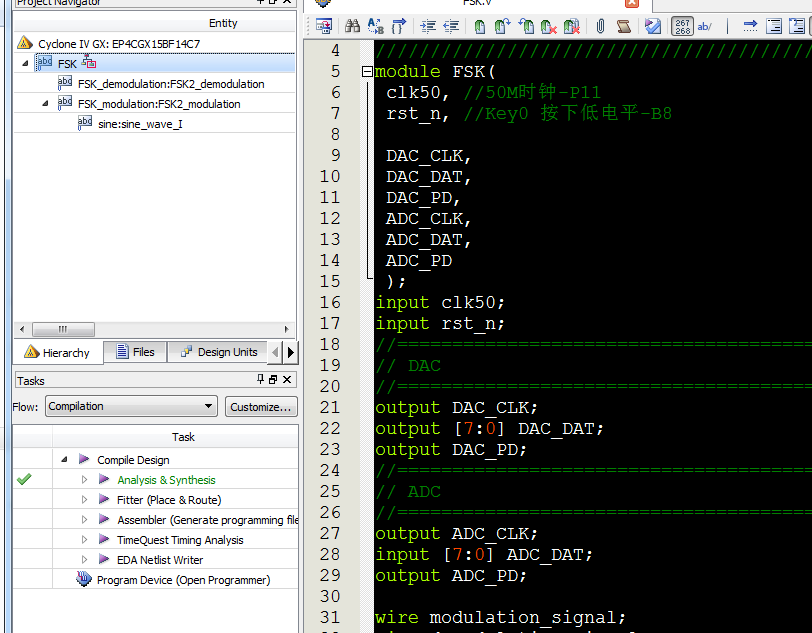

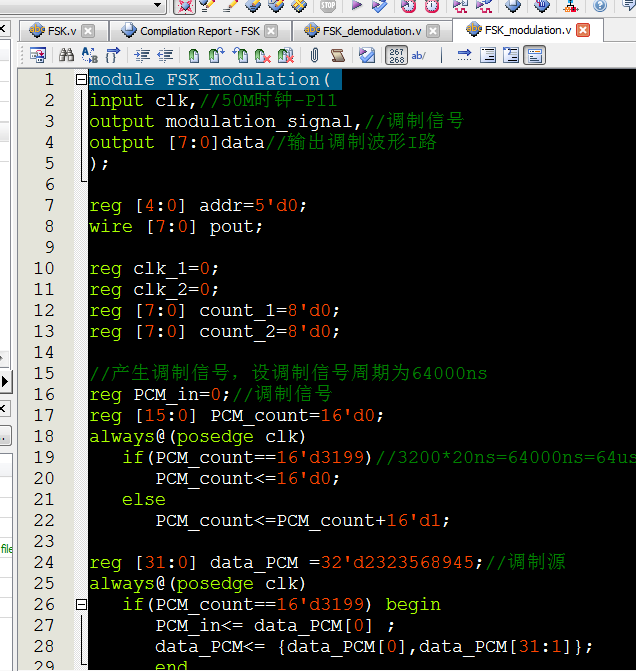

部分代码展示:

`timescale 1ns / 1ps // // Module Name: FSK // module FSK( clk50, //50M时钟-P11 rst_n, //Key0 按下低电平-B8 DAC_CLK, DAC_DAT, DAC_PD, ADC_CLK, ADC_DAT, ADC_PD ); input clk50; input rst_n; //======================================================= // DAC //======================================================= output DAC_CLK; output [7:0] DAC_DAT; output DAC_PD; //======================================================= // ADC //======================================================= output ADC_CLK; input [7:0] ADC_DAT; output ADC_PD; wire modulation_signal; wire demodulation_signal; reg [7:0] ADC_DAT_REG;//AD后数据 reg clk25; assign DAC_CLK = clk50; assign ADC_CLK = clk25; assign DAC_PD = 0; assign ADC_PD = 0; reg [8:0] Cont; //定义一个计数器,用于 SIN 的地址 Cont 持续计数 always@(posedge clk50 ) begin clk25 <= ~clk25; end always @(posedge clk50) begin ADC_DAT_REG <= ADC_DAT; end FSK_modulation FSK2_modulation( . clk(clk50),//50M时钟-P11 . modulation_signal(modulation_signal),//调制信号 . data(DAC_DAT)//输出调制波形路 ); FSK_demodulation FSK2_demodulation( . clk(clk50),//50M时钟-P11 . demodulation_signal(demodulation_signal),//解调信号 //. data(DAC_DAT)//仿真时用该句,屏蔽下面那句 . data(ADC_DAT_REG)//输入调制波形仿真时用DAC_DAT将数据还回到解调模块,下载板子验证时使用ADC_DAT_REG );

源代码

扫描文章末尾的公众号二维码