热门标签

热门文章

- 1Xcode隐私协议适配_xcprivacy

- 2大模型时代需要什么样的人才?

- 3fatal: refusing to merge unrelated histories_sourcetree fatal: refusing to merge unrelated hist

- 4PCIe 3.0 Xilinx V7搭配Aurora 40G:全源码、设计方案及电路图详解_xilinx pcie

- 5基于java的微信小程序的实现(一)项目介绍_java微信小程序开发

- 6C语言基础语法解析-输入与输出_语法分析程序的输入和输出

- 7stc89c52和stc89c52rc有什么区别

- 8libcurl-curl_easy_setopt-所有选项-名称-概要-描述_libcurl sha256

- 92023毕业生薪酬报告-本科生版

- 10这样设置Prompt,让ChatGPT输出更好的效果!_让gpt返回指定格式内容 三个单引号

当前位置: article > 正文

verilog 232串口通信程序

作者:从前慢现在也慢 | 2024-06-09 01:23:57

赞

踩

verilog 232串口通信程序

1,串口通信协议:

通常串口的一次发送或接收由四个部分组成:起始位S、数据位D0~D7(一般为 6 位~8 位之间可变,数据低位在前)、校验位(奇校验、偶检验或不需要校验位)、停止位(通常为1位、1.5位、2位)。停止位必须为逻辑 1。在一次串口通信过程中,数据接收与发送双方没有共享时钟,因此,双方必须协商好数据传输波特率。根据双方协议好的传输速率,接收端即可对发送端的数据进行采样。常见的波特率标准有300bps,600bps,800bps,9600bps,19200bps等。当然更块的速度意味着对采样的要求更高,有可能误码率会逐渐提高。通常对串口进行数据采样,采用更高频的时钟。这样做的目的是采用高频时钟来锁存低频时钟,减少数据误码率,增加接收模块自纠错能力。

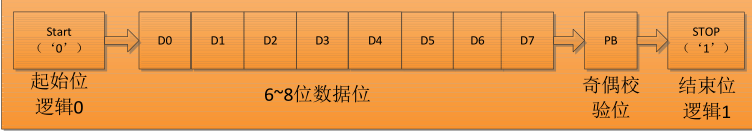

具体的工作流程为:发送端按照预先设定好的波特率,发送起始位(Start)+数据位(data)+奇偶校验位+结束位。起始位为逻辑 0,结束位为逻辑 1,发送端在空闲状态为 1。发送数据包格式:

2,verilog232串口代码

- module uart(

- clk,rst_n,

- rx_bit,

- rx_en, //仿真测试

- rx_stop, //仿真测试

- bit_data, //仿真测试

- bit_num, //仿真测试

-

推荐阅读

相关标签