- 1同一个 Github 账号之多台电脑间协同开发_两台电脑连接github

- 2零基础了解AI的技术点路线+超常用名词_ai人工智能要会哪些编程技术

- 3在Linux服务器上部署大语言模型_大语言模型云服务器pip install -r reuests.txt

- 42024年航空航天与力学国际学术会议(ICAM 2024)_2024大连 力学会议

- 5程序员·职场效能必修宝典⑤①:突破自己的职业天花板

- 6【ruoyi】docker 项目实战

- 7使用RPA通过GPT大模型AI Agent自动执行业务流程任务企业级应用开发实战:RPA在水利与环保行业的应用实例_rpa在水务

- 8关于面试找工作、工作中注意点的个人总结(一)_boss找工作注意点

- 9基于java EE——学生管理系统(超详细,0基础也可)_javaee学生管理系统

- 10PostgreSQL 事件触发器_postgres 触发器

FPGA - 7系列 FPGA内部结构之SelectIO -01- 简介与DCI技术简介

赞

踩

SelectIO简介

FPGA的SelectIO就是I/O接口以及I/O逻辑的总称。Xilinx SelectIO支持电平标准多,除MIPI C-PHY电平(三电平标准)外,IO能直接对接3.3V以及3.3V以下基本所有电平标准,初步统计支持72种不同电平标准。同时在使用是经常需要根据具体的应用设计进行配置电平标准以及IO配置,本文节选翻译整理自UG471的第一章,对7系列的FPGA的SelectIO资源进行简要介绍以及数控阻抗 (DCI) 技术的介绍。

7系列FPGA I/O Bank支持的功能

所有7系列FPGA都有可配置的SelectIO驱动器和接收器,支持多种标准接口。强大的功能集包括可编程控制输出强度和压摆率的可编程控制,使用数字控制阻抗的(DCI)的片上终端,以及内部产生参考电压(INTERNAL_VREF)的能力。

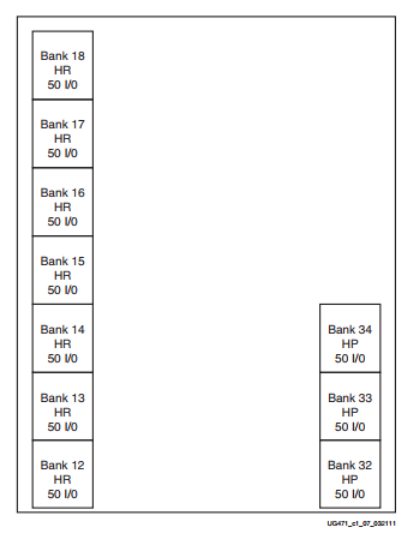

HR Bank没有DCI。DCI并不适用于HR Bank。除了一些例外情况,每个I/O库包含50个SelectIO引脚。在每个库的最末端的两个引脚只能用于单端I/O标准。剩下的48个的引脚可以使用单端或差分标准,使用两个SelectIO引脚组成的正/负(P/N)对,可用于单端或差分标准。每个SelectIO资源都包含输入、输出和三态驱动器。

7系列FPGA的HR和HP I/O Bank支持的功能如下:

| Feature | HP I/O Banks | HR I/O Banks |

|---|---|---|

| 3.3V I/O standard | N/A | Supported |

| 2.5V I/O standards | N/A | Supported |

| 1.8V I/O standards | Supported | Supported |

| 1.5V I/O standards | Supported | Supported |

| 1.35V I/O standards | Supported | Supported |

| 1.2V I/O standards | Supported | Supported |

| LVDS signaling | Supported | Supported |

| 24 mA drive option for LVCMOS18 and LVTTL outputs | N/A | Supported |

| V CCAUX_IO supply rail | Supported | N/A |

| Digitally-controlled impedance (DCI) and DCI cascading | Supported | N/A |

| Internal VREF | Supported | Supported |

| Internal differential termination (DIFF_TERM) | Supported | Supported |

| IDELAY | Supported | Supported |

| ODELAY | Supported | N/A |

| IDELAYCTRL | Supported | Supported |

| ISERDES | Supported | Supported |

| OSERDES | Supported | Supported |

| ZHOLD_DELAY | N/A | Supported |

单端与差分逻辑架构

SelectIO引脚可以被配置成各种I/O标准,包括单端和差分。

- 单端I/O标准(如LVCMOS、LVTTL、HSTL、PCI和SSTL)。

- 差分I/O标准(例如,LVDS、Mini_LVDS、RSDS、PPDS、BLVDS和差分HSTL和SSTL)。

被配置成不同I/O标准的引脚,端口的输入输出的连接方式也不相同。

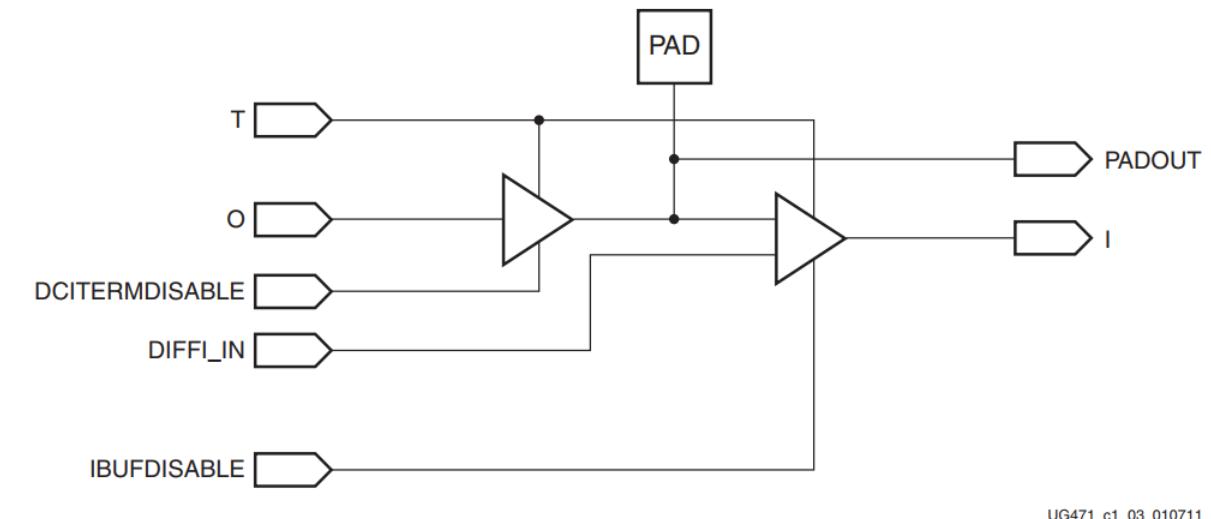

下图显示了单端(仅)HP I/O Bank(IOB)及其与内部逻辑和器件焊盘的连接。

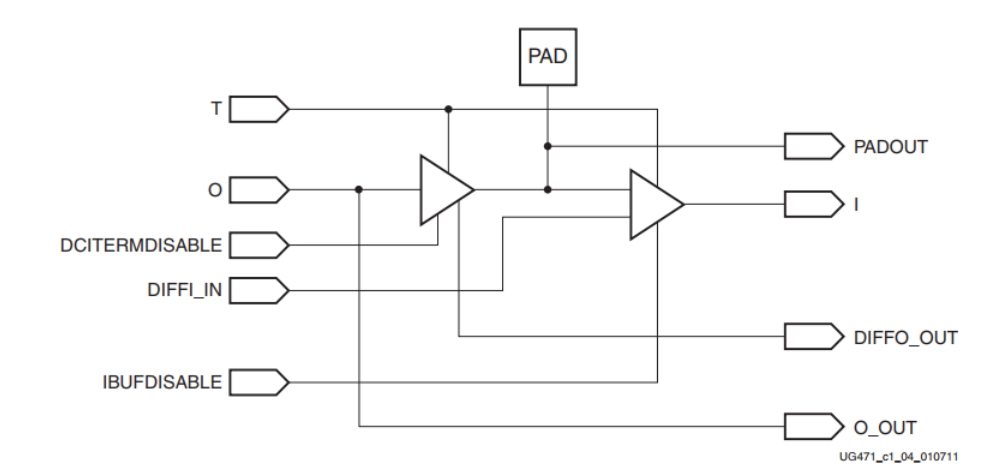

下图显示了常规HP IO Bank及其与内部逻辑和器件焊盘的连接。

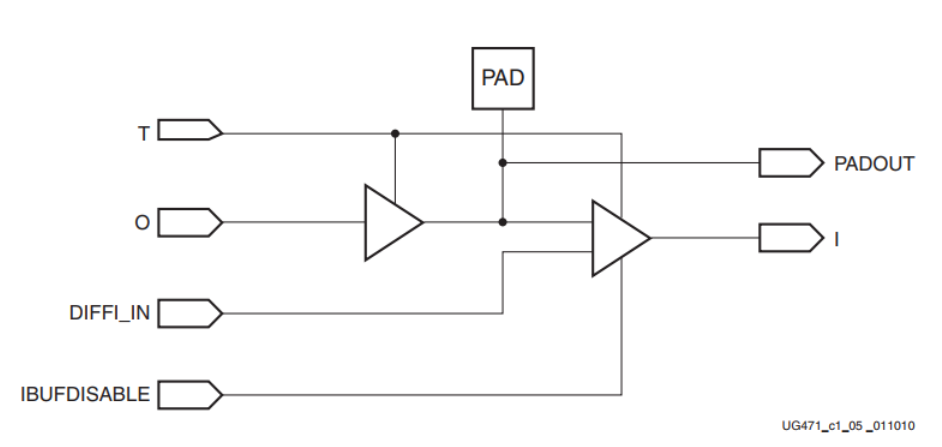

下图显示了单端(仅)的HR IO Bank及其与内部逻辑和器件焊盘的连接。

下图显示了单端(仅)的HR IO Bank及其与内部逻辑和器件焊盘的连接。

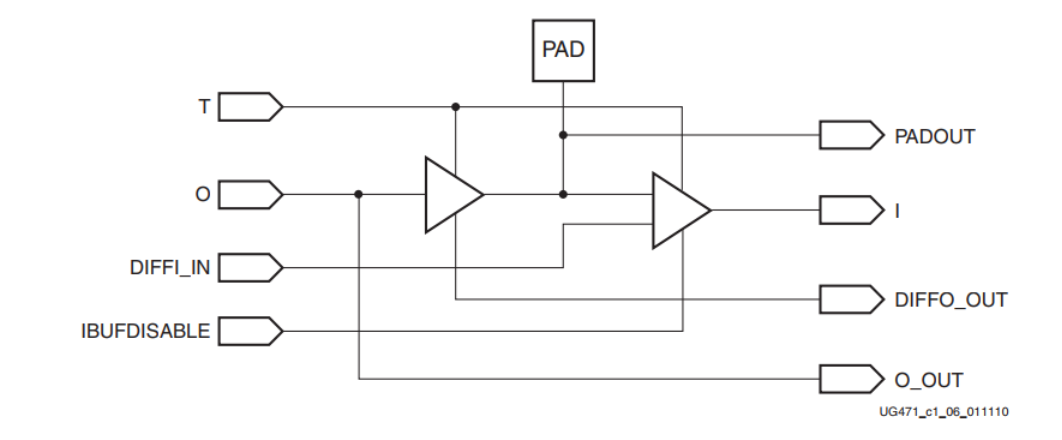

下图显示了常规的HR IO Bank及其与内部逻辑和器件焊盘的连接。

经过对比分析可知,在 HP 和 HR I/O Bank中,单端和常规IO Bank 基本上是等同的,除了单端IOB没有连接来产生差分输出的信号。HR和HP相比,除了缺少DCI片上终端使能控制,其余结构也基本相似。

在大多数设备中,单端 IOB是位于每个I/O组两端的两个引脚。组成每组其他48个引脚的常规IOB可以实现单端和差分I/O标准。每个IOB都有一个直接连接到ILOGIC/OLOGIC对,包含数据和三态的输入和输出逻辑资源。每个IOB都有一个与ILOGIC/OLOGIC对的直接连接,包含了IOB的数据和三态控制的输入和输出逻辑资源,用于数据和IOB的三态控制。ILOGIC和OLOGIC都可以被配置为ISERDES和OSERDES。

设计时一般准则

本节总结了使用7系列FPGA的SelectIO资源进行设计时需要考虑的一般准则。在7系列器件中,一个I/O库由50个IOB组成。Bank的数量取决于器件尺寸和封装引脚。在7系列FPGA概述中,可用的I/O库的总数按器件类型列出。可用的I/O库总数是按器件类型列出的。例如,XC7K325T有10个可用的I/O库。

选择IO引脚的电源电压

VCCO

VCCO电源是7系列I/O电路的主要电源。一个给定的I/O组的所有VCCO引脚必须连接到电路板上相同的外部电源,因此,一个给定的I/O组内的所有I/O必须共享相同的VCCO电平。VCCO电压必须符合分配给I/O组的I/O标准的要求。不正确的VCCO电压会导致功能丧失或设备损坏。在HP I/O Bank中,如果I/O标准电压要求<1.8V,但应用VCCO>2.5V,器件会自动进入过压保护模式。用正确的VCCO电平重新配置器件,就可以恢复正常工作。

VREF

具有差分输入缓冲器的单端I/O标准需要一个输入参考电压(VREF)。当一个I/O组内需要VREF时,该组的两个多功能VREF引脚必须被用作VREF电源输入。7系列FPGA可以通过启用INTERNAL_VREF约束来选择使用内部产生的参考电压。

VCCAUX

全局辅助(VCCAUX)电源主要用于为7系列FPGA内部各种块特征的互连逻辑提供电源。在I/O库中,VCCAUX也被用来为一些I/O标准的输入缓冲电路供电。这些包括所有1.8V或以下的单端I/O标准,以及一些2.5V标准(仅HR I/O Bank)。此外,VCCAUX为用于差分和VREF I/O标准的组的差分输入缓冲电路提供电源。

VCCAUX_IO

辅助I/O(VCCAUX_IO)电源只存在于HP I/O库中,为I/O电路提供电源。Kintex-7和Virtex-7 FPGAs数据表中包含一个 "存储器接口的最大物理接口(PHY)速率 "的表格,其中提到了VCCAUX_IO。该表指出了VCCAUX_IO引脚如何在1.8V(默认)或可选的2.0V下供电,以实现某些类型存储器接口的更高频率性能。尽管该表是为存储器接口设计的,但它也可以根据目标比特率为其他高速单端接口的VCCAUX_IO供电提供指导。

**该表不适用于LVDS,因为LVDS使用的驱动电路与单端驱动不同,受VCCAUX_IO电平影响较大。**因此,对于LVDS接口,VCCAUX_IO轨哪个电压水平上供电并不重要。1.8V的默认值提供了较低的功耗,并在I/O中提供了非常接近于相同的性能。当单端驱动器所支持的最快比特率需要略微增加的性能时,可以选择2.0V。I/O 网络和原语有一个称为 VCCAUX_IO 的设计约束,如果要将任何 bank 的 VCCAUX_IO 引脚设置为 2.0V,则应在设计中指定该约束。

配置期间和配置之后的I/O状态

7 系列 FPGA 具有专用于 I/O bank 0 中包含的配置功能的引脚。Bank 14 和 15 还包含称为多功能或多用途管脚的 I/O 管脚,也可用于配置,但配置后转换为普通 I/O 引脚。 此外,在 SSI 器件中,bank 11、12、17、18、20 和 21 中的引脚具有配置过程中的限制类似于多功能引脚。 然而,在这些引脚bank没有任何配置功能。

在 bank 14 和/或 bank 15 是 HR bank 且配置为 VCCO 要求 < 1.8V 的器件中,如果输入连接到 0 或悬空且配置电压 > 2.5V,则在配置期间输入可能会从 0-1-0 转换到互连逻辑。

仅HP bank 中可用的DCI

数控阻抗 (DCI) 技术介绍

随着 FPGA 变得越来越大,系统时钟速度越来越快,PCB 板的设计和制造变得更加困难。 随着边缘速率越来越快,保持信号完整性成为一个关键问题。 PCB 板走线必须正确端接以避免反射或振铃。 为了终止迹线,传统上添加电阻以使输出和/或输入与接收器或驱动器的阻抗匹配到迹线的阻抗。 然而,由于器件 I/O 的增加,在器件引脚附近添加电阻器会增加电路板面积和元件数量,并且在某些情况下可能在物理上是不可能的。 为了解决这些问题并实现更好的信号完整性,Xilinx 开发了数控阻抗 (DCI) 技术。

根据 I/O 标准,DCI 可以控制驱动器的输出阻抗,也可以在驱动器和/或接收器上添加一个并行终端,以精确匹配传输线的特性阻抗。 DCI 主动调整 I/O 内部的这些阻抗,以校准放置在 VRN 和 VRP 引脚上的外部精密参考电阻。 这可以补偿由于工艺变化引起的 I/O 阻抗变化。 它还连续调整阻抗以补偿温度和电源电压波动的变化。

对于具有受控阻抗驱动器的 I/O 标准,DCI 控制驱动器阻抗以匹配两个参考电阻器,或者对于某些标准,匹配这些参考电阻器值的一半。

对于具有受控并行终端的 I/O 标准,DCI 为发送器和接收器提供并行终端。 这消除了板上端接电阻的需要,减少了电路板布线困难和组件数量,并通过消除短截线反射提高了信号完整性。 当终端电阻距离传输线末端太远时,会发生短截线反射。 使用 DCI,端接电阻器尽可能靠近输出驱动器或输入缓冲器,从而消除短截线反射。 DCI 仅在 7 系列 FPGA HP I/O bank 中可用,在 HR I/O bank 中不可用。

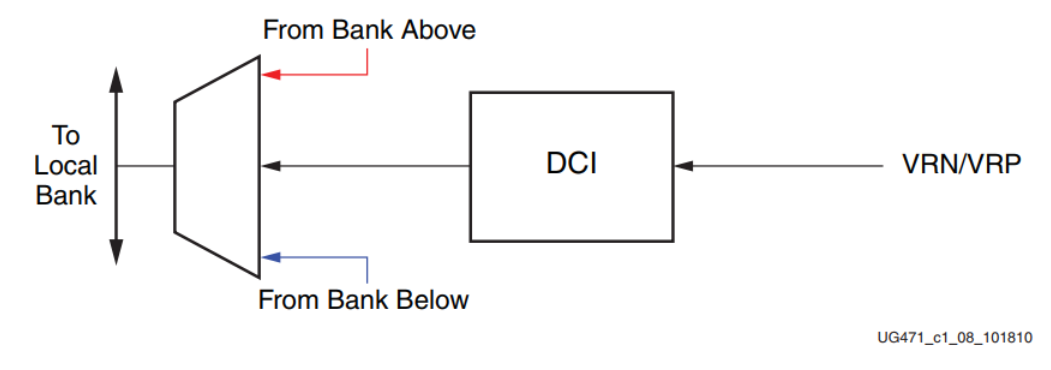

Xilinx DCI

DCI 在每个 I/O bank 中使用两个多用途参考管脚来控制驱动器的阻抗或该 bank 中所有 I/O 的并行终端值。 N 参考引脚 (VRN) 必须通过参考电阻上拉至 VCCO,而 P 参考引脚 (VRP) 必须通过另一个参考电阻下拉至地。 每个参考电阻的值应等于 PCB 板走线的特性阻抗或该值的两倍。

要在设计中使用DCI:

- 在 HP I/O bank 中分配 DCI I/O 标准之一。

- 将 VRN 多功能引脚连接到一个精密电阻,该电阻连接到同一组的 VCCO 。

- 将 VRP 多功能引脚连接到接地的精密电阻。

以下部分讨论如何确定不同 I/O 标准的 VRN 和 VRP 的精密电阻值。 每个 bank 仅使用一组 VRN 和 VRP 电阻,因此每个 bank 内的所有 DCI 标准必须能够共享相同的外部电阻值。 如果同一 I/O bank 列中的多个 I/O bank 使用 DCI,并且所有这些 I/O bank 使用相同的 VRN/VRP 电阻值,则内部 VRN 和 VRP 节点可以级联,这样只有一对 整个 I/O 列中所有 I/O bank 的管脚都需要连接到精密电阻。 此选项称为 DCI 级联。如果组中未使用 DCI I/O 标准,则这些管脚可用作常规 I/O 管脚。

DCI 通过有选择地打开或关闭 I/O 中的晶体管来调整 I/O 的阻抗。 调整阻抗以匹配外部参考电阻。 调整在设备启动序列期间开始。 默认情况下,在阻抗调整过程的第一部分完成之前,DONE 引脚不会变为高电平。

DCI 校准可以通过例化 DCIRESET 原语来复位。 在设备运行时将 RST 输入切换到 DCIRESET 原语,重置 DCI 状态机并重新启动校准过程。 在 DCIRESET 模块的 LOCKED 输出被断言之前,所有使用 DCI 的 I/O 都将不可用。 此功能在温度和/或电源电压从器件上电到标称工作条件显着变化的应用中非常有用。

对于受控阻抗输出驱动器,可以调整阻抗以匹配参考电阻器或参考电阻器的一半电阻。 对于片上端接,端接总是被调整以匹配参考电阻。

对于支持 DCI 控制阻抗驱动器的 I/O 标准,DCI 可以将输出驱动器配置为以下类型:

- 受控阻抗驱动器(源极端接), Controlled Impedance Driver (Source Termination)

- 具有半阻抗(源极端接)的受控阻抗驱动器 ,Controlled Impedance Driver with Half Impedance (Source Termination)

对于支持并行端接的 I/O 标准,DCI 创建一个与 VCCO/2 电压电平等效的戴维南电阻或分离端接电阻。 I/O 标准的命名约定增加了:

- 如果 I/O 中始终存在分离终端电阻,则在 I/O 标准名称中添加 DCI,无论该标准是用于输入、输出还是双向端口。

- I/O 标准名称中的T_DCI,如果仅当输出缓冲器为三态时才存在分离终端电阻。

Match_cycle 配置选项

Match_cycle 是一个配置选项,可在 FPGA 配置序列结束时选择性地暂停启动序列,直到 DCI 逻辑对外部参考电阻器执行第一次匹配(校准)。 此选项有时也称为 DCI 匹配。

DCIUpdateMode 配置选项

DCIUpdateMode 是一个配置选项,可以覆盖对 DCI 电路更新与 VRN 和 VRP 参考电阻匹配的阻抗的频率的控制。 此选项默认为 AsRequired,但在 Xilinx 实现软件中还有一个可选值 Quiet。**强烈建议将 DCIUpdateMode 选项保持为默认值 AsRequired,以便允许 DCI 电路正常运行。**DCIUpdateMode 配置选项的设置如下:

- AsRequired:在设备初始化时进行初始阻抗校准,并在整个设备操作期间根据需要进行动态阻抗调整(默认)。

- Continuous:对于 7 系列 FPGA,此值无效(默认为 AsRequired)。

- Quiet:阻抗校准仅在器件初始化时进行一次,或者对于包含该原语的设计,每次在 DCIRESET 原语上断言 RST 引脚时进行一次。

DCIRESET原语

DCIRESET 是 Xilinx 设计原语,它提供了在设计正常运行期间执行 DCI 控制器状态机复位的能力。 除非 DCIUpdateMode 设置为 Quiet或对于下面概述的与使用设置为使用 DCI 的多功能引脚相关的情况,在大多数情况下,设计中不需要此原语。

某些 Bank 的特殊 DCI 要求

如果 I/O bank 14 或 15(任何设备)或 bank 11、12、17、18、20 和 21(仅限 SSI 设备)中的任何多功能管脚被分配 DCI I /O 标准在用户设计中,DCIRESET 原语也应包含在设计中并使用。 在这种情况下,设计应该脉冲 DCIRESET 的 RST 输入,然后等待 LOCKED 信号被断言,然后再使用符合 DCI 标准的这些引脚上的任何用户输入或输出。 这是必需的,因为这些 I/O 管脚会忽略在正常设备初始化期间发生的初始 DCI 校准。

因此,如果未使用 DCIRESET 原语且 DCIUpdateMode 设置为 AsRequired,则在这些引脚变为正常 I/O 引脚之后,在配置结束与 DCI 校准算法更新这些引脚 DCI 设置之间会有一个不确定的延迟。如果不使用 DCIRESET 并且 DCIUpdateMode 设置为 Quiet,则这些引脚将永远不会设置其 DCI 值。 在这种情况下,受控阻抗 DCI I/O 标准(例如 LVDCI_18)会一直表现得好像处于高阻态,而拆分终端 DCI I/O 标准(例如 SSTL15_DCI)会表现得好像没有内部终端电阻。 在设计中包含和使用 DCIRESET 原语允许这些引脚具有 DCI I/O 标准并且可以毫无问题地执行。

DCI 级联

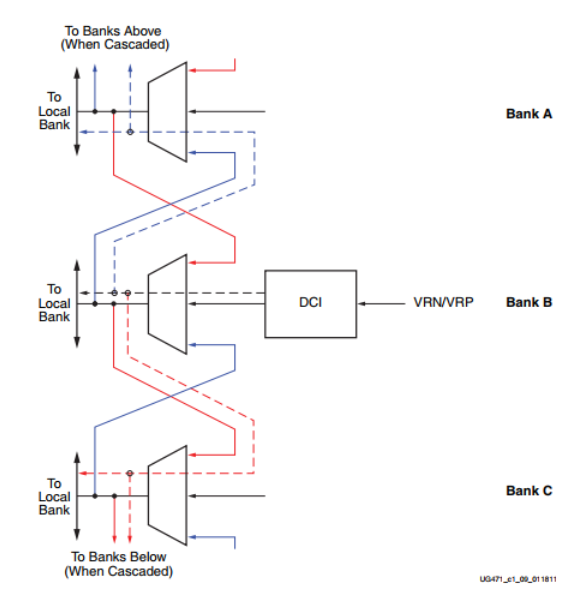

使用 DCI I/O 标准的 7 系列 FPGA HP I/O bank 可以选择从另一个 HP I/O bank 导出 DCI 阻抗值。 如下图所示,数字控制总线内部分布在整个 bank 中,以控制每个 I/O 的阻抗。

对于 DCI 级联,一个 I/O bank(主 bank)必须将其 VRN/VRP 管脚连接到外部参考电阻。 同一 HP I/O bank 列(从库)中的其他 I/O bank 可以使用具有与主库相同阻抗的 DCI 标准,而无需将这些从库上的 VRN/VRP 管脚连接到外部电阻器。 级联组中的 DCI 阻抗控制从 I/O 主组接收。

下图显示了对多个 I/O bank 的 DCI 级联支持。 Bank B 是主 I/O bank,而 Bank A 和 C 被认为是从 I/O bank。

使用 DCI 级联时的指导原则如下:

- DCI 级联只能通过 HP I/O bank 列使用。

- 主和从 SelectIO bank 必须都驻留在设备上的同一 HP I/O 列上,并且可以跨越整个列,除非有插入器边界。

- DCI 级联不能通过采用堆叠硅互连 (SSI) 技术的较大 Virtex-7 器件的中介层边界。 这包括 XC7V2000T 和 XC7VX1140T 器件。

- 主和从I/O bank 必须具有相同的VCCO 和VREF(如果适用)电压。

- 同一 HP I/O 列中不使用 DCI(直通 bank)的 I/O bank 不必遵守 VCCO 和 VREF 电压规则来组合 DCI 设置。

- 所有主bank 和从 bank 都必须满足 DCI I/O bank 兼容性规则(例如,所有主库和从库只允许使用一种使用单一终端类型的 DCI I/O 标准)。

- 要定位位于同一 I/O 列中的 I/O bank,参阅 UG475。

- 有关在设计中实施直流级联的具体信息,参阅UG471的46页的 DCI_CASCADE 约束。

- Xilinx 建议给未使用的 bank也上电,因为将未使用的 I/O bank 的 VCCO 管脚悬空会降低这些管脚和 bank 中的 I/O 管脚的 ESD 保护水平。 如果 bank 未上电,DCI 仍可通过未上电的 bank 级联。

受控阻抗驱动器(源端接)

为了优化高速或高性能应用的信号完整性,需要采取额外措施来使驱动器的输出阻抗与传输线和接收器的阻抗相匹配。 理想情况下,驱动器的输出阻抗必须与驱动线的特性阻抗相匹配,否则会由于不连续性而发生反射。 为了解决这个问题,设计人员有时会使用靠近高强度、低阻抗驱动器引脚的外部源串联终端电阻。 选择电阻值,使驱动器的输出阻抗加上源串联终端电阻的电阻之和大致等于传输线的阻抗。

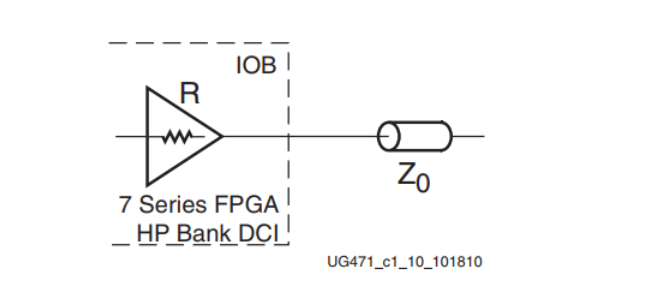

DCI 可以提供受控阻抗输出驱动器来消除反射,而无需使用外部源极终端电阻。 阻抗由外部参考电阻器设置,其电阻等于走线阻抗。

支持受控阻抗驱动器的 DCI I/O 标准有:LVDCI_15、LVDCI_18、HSLVDCI_15、HSLVDCI_18、HSUL_12_DCI 和 DIFF_HSUL_12_DCI。

下图说明了 7 系列器件中的受控阻抗驱动器。

具有半阻抗(源极端接)的可控阻抗驱动器

DCI 还为驱动器提供了一半的参考电阻器阻抗。 参考电阻值翻倍可将这些电阻的静态功耗降低一半。 支持具有半阻抗的受控阻抗驱动器的 DCI I/O 标准是 LVDCI_DV2_15 和 LVDCI_DV2_18。

下图说明了一个 7 系列器件内部具有半阻抗的受控驱动器。 参考电阻 R 必须为 2 × Z0 以匹配 Z0 的阻抗。

Split-Termination DCI(戴维宁等效终端到 VCCO/2)

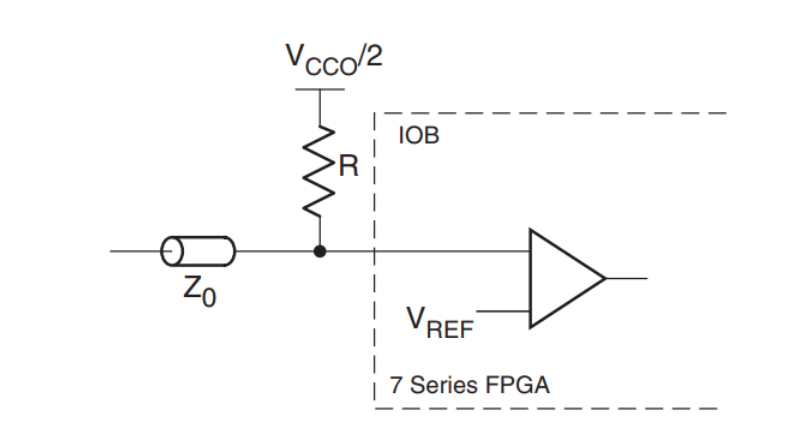

一些 I/O 标准(例如 HSTL 和 SSTL)要求输入终端电阻 ® 连接到 VCCO/2 的 VTT 电压,见下图。

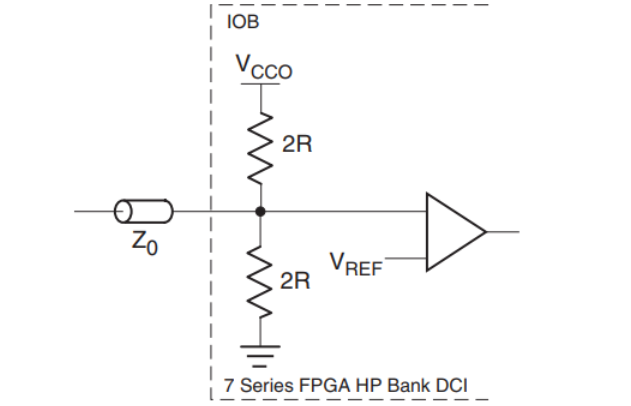

分体式终端 DCI 使用两个电阻值 (2R) 两倍的电阻器创建戴维南等效电路。 一个连接到 VCCO,另一个连接到地。 使用这种方法,分离端接 DCI 提供与 VCCO/2 等效的端接。2R 终端电阻由外部参考电阻器设置。 例如,要实现 50Ω 至 VCCO/2 的戴维南等效并联端接电路,需要在 VRN 和 VRP 引脚上使用 100Ω 外部精密电阻。 支持分离端接的 DCI 输入标准如下表所示。

| HSTL_I_DCI | DIFF_HSTL_I_DCI | SSTL18_I_DCI | DIFF_SSTL18_I_DCI |

|---|---|---|---|

| HSTL_I_DCI_18 | DIFF_HSTL_I_DCI_18 | SSTL18_II_DCI | DIFF_SSTL18_II_DCI |

| HSTL_II_DCI | DIFF_HSTL_II_DCI | SSTL18_II_T_DCI | DIFF_SSTL18_II_T_DCI |

| HSTL_II_DCI_18 | DIFF_HSTL_II_DCI_18 | SSTL15_DCI | DIFF_SSTL15_DCI |

| HSTL_II_T_DCI | DIFF_HSTL_II_T_DCI | SSTL15_T_DCI | DIFF_SSTL15_T_DCI |

| HSTL_II_T_DCI_18 | DIFF_HSTL_II_T_DCI_18 | SSTL135_DCI | DIFF_SSTL135_DCI |

| SSTL135_T_DCI | DIFF_SSTL135_T_DCI | ||

| SSTL12_DCI | DIFF_SSTL12_DCI | ||

| SSTL12_T_DCI | DIFF_SSTL12_T_DCI |

下图说明了 7 系列设备中的分离式终端 DCI。

VRN/VRP 外部电阻设计移植指南

以前具有 DCI 的 Xilinx FPGA 系列使用稍微不同的电路来校准来自放置在 VRN 和 VRP 引脚上的外部参考电阻的分离终端阻抗。 Virtex-6 FPGA DCI 将分离端接电路的每个支路校准为外部电阻值的两倍。 例如,在具有 50Ω 到 VCCO/2 的目标并联终端的 Virtex-6 器件中,VRN 和 VRP 引脚上需要 50Ω 外部电阻器。

7 系列 FPGA DCI 校准分离端接电路的每个支路,使其直接等于外部电阻值。 例如,在具有 50Ω 到 VCCO/2 的目标并联终端的 7 系列器件中,VRN 和 VRP 引脚上需要 100Ω 外部电阻器。

在为受控阻抗 DCI 和分离端接 DCI 标准选择要在同一 I/O 组(或多个级联 DCI 组)中使用的 VRN 和 VRP 值时,考虑这一点尤为重要。

在具有用于 LVDCI_18 输出的 50Ω 目标受控阻抗驱动器和用于 HSTL_I_DCI_18 输入的 50Ω 目标分离终端接收器的 Virtex-6 FPGA 设计中,可以使用 VRN 和 VRP 引脚上的 50Ω 外部电阻器来实现。 将同样的设计移植到 7 系列 FPGA 不会改变 HSTL_I_DCI_18 I/O 标准; 但是,外部电阻器必须更改为 100Ω,并且受控阻抗驱动器更改为 LVDCI_DIV2_18 输出。 这个示例结果是等价的; 但是,电阻值和 I/O 标准都需要更改。 VRN 和 VRP 外部电阻器可以安全地使用 0.05W 或更高的额定功率。

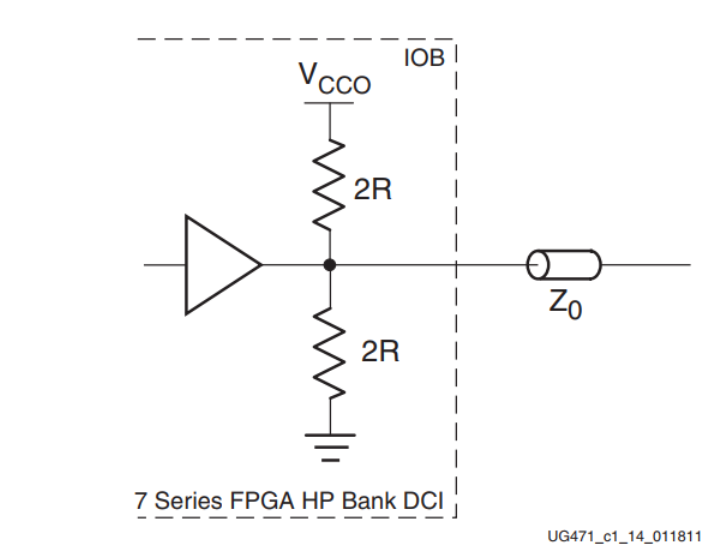

DCI and 3-state DCI (T_DCI)

SSTL 和 HSTL I/O 标准的 I 类驱动程序版本仅支持单向信令; 它们只能分配给设计中的仅输入或仅输出引脚,而不是双向引脚。 I 类 SSTL 和 HSTL I/O 标准的 DCI 版本仅在输入(而非输出)上具有内部分离终端电阻。 支持双向和单向信令的 SSTL 和 HSTL I/O 标准的 II 类驱动程序版本; 它们可以分配给设计中的输入、输出或双向引脚。 II 类 SSTL 和 HSTL I/O 标准的 DCI 版本始终在输入、输出或双向引脚上存在内部分离终端电阻。下图说明了 7 系列器件内部具有分离终端的驱动程序。

当驱动时存在分离终端时,DCI 仅控制终端的阻抗,而不控制驱动器。 然而,许多应用都可以受益于在引脚驱动时关闭分离端接电阻器。 三态 DCI (T_DCI) 标准旨在通过在输出缓冲器驱动时关闭分离终端电阻器来满足这一要求,并在输出处于三态时打开分离终端电阻器(例如当 接收或处于空闲状态)。 T_DCI 标准只能分配给双向引脚。 对于单向输入引脚,可以分配标准的 DCI 版本。 对于单向输出引脚,可以分配非 DCI 或 DCI 版本。

具有始终存在的分离端接 DCI 电阻器的 I/O 标准下表所示。

| HSTL_I_DCI | DIFF_HSTL_I_DCI | SSTL18_I_DCI | DIFF_SSTL18_I_DCI |

|---|---|---|---|

| HSTL_I_DCI_18 | DIFF_HSTL_I_DCI_18 | SSTL18_II_DCI | DIFF_SSTL18_II_DCI |

| HSTL_II_DCI | DIFF_HSTL_II_DCI | SSTL15_DCI | DIFF_SSTL15_DCI |

| HSTL_II_DCI_18 | DIFF_HSTL_II_DCI_18 | SSTL135_DCI | DIFF_SSTL135_DCI |

| SSTL12_DCI | DIFF_SSTL12_DCI |

仅在三态时具有分离端接 DCI 的 I/O 标准:

| HSTL_II_T_DCI | SSTL18_II_T_DCI | DIFF_SSTL18_II_T_DCI |

|---|---|---|

| HSTL_II_T_DCI_18 | SSTL15_T_DCI | DIFF_SSTL15_T_DCI |

| DIFF_HSTL_II__T_DCI | SSTL135_T_DCI | DIFF_SSTL135_T_DCI |

| DIFF_HSTL_II_T_DCI_18 | SSTL12_T_DCI | DIFF_SSTL12_T_DCI |

所有 7 系列设备 DCI I/O 标准:

| LVDCI_18 | HSTL_I_DCI | DIFF_HSTL_I_DCI | SSTL18_I_DCI | DIFF_SSTL18_I_DCI |

|---|---|---|---|---|

| LVDCI_15 | HSTL_I_DCI_18 | DIFF_HSTL_I_DCI_18 | SSTL18_II_DCI | DIFF_SSTL18_II_DCI |

| LVDCI_DV2_18 | HSTL_II_DCI | DIFF_HSTL_II_DCI | SSTL18_II_T_DCI | DIFF_SSTL18_II_T_DCI |

| LVDCI_DV2_15 | HSTL_II_DCI_18 | DIFF_HSTL_II_DCI_18 | SSTL15_DCI | DIFF_SSTL15_DCI |

| HSLVDCI_18 | HSTL_II_T_DCI | DIFF_HSTL_II_T_DCI | SSTL15_T_DCI | DIFF_SSTL15_T_DCI |

| HSLVDCI_15 | HSTL_II_T_DCI_18 | DIFF_HSTL_II_T_DCI_18 | SSTL135_DCI | DIFF_SSTL135_DCI |

| SSTL135_T_DCI | DIFF_SSTL135_T_DCI | |||

| SSTL12_DCI | DIFF_SSTL12_DCI | |||

| SSTL12_T_DCI | DIFF_SSTL12_T_DCI | |||

| HSUL_12_DCI | DIFF_HSUL_12_DCI |

要在 7 系列器件中正确使用 DCI:

-

VCCO 管脚必须根据该 I/O bank 中的 IOSTANDARD 连接到适当的 VCCO 电压。

-

必须在软件中使用正确的 DCI I/O 缓冲器,方法是使用 IOSTANDARD 属性或 HDL 代码中的实例化。

-

DCI 标准要求将外部参考电阻器连接到多用途引脚(VRN 和 VRP)。 需要时,这两个多用途管脚不能用作使用 DCI 的 I/O bank 中的通用 I/O,或级联 DCI 时的主 I/O bank 中的通用 I/O。引脚 VRN 必须通过其参考电阻上拉至 VCCO。 引脚 VRP 必须通过其参考电阻下拉至地。 在从 I/O bank 中级联 DCI 时,此要求有一个例外,因为 VRN 和 VRP 引脚可用作通用 I/O。

具有受控阻抗驱动器的 DCI 标准可用于仅输入信号。 对于这种情况,如果这些引脚是给定 I/O bank 中唯一使用 DCI 标准的引脚,则该 bank 不需要将外部参考电阻器连接到 VRP/VRN 引脚。 当这些基于 DCI 的 I/O 标准是 bank 中唯一的标准时,该 bank 中的 VRP 和 VRN 管脚可用作通用 I/O。

- VRP/VRN 上不需要参考电阻的 DCI 输入如下表所示。

| LVDCI_18 | LVDCI_DV2_18 | HSLVDCI_18 | HSUL_12_DCI |

|---|---|---|---|

| LVDCI_15 | LVDCI_DV2_15 | HSLVDCI_15 | DIFF_HSUL_12_DCI |

- 应选择外部参考电阻器的值,以提供所需的输出驱动器阻抗或分路终端阻抗。 例如,当使用 LVDCI_15 时,要实现 50Ω 的输出驱动器阻抗,VRN 和 VRP 引脚上使用的外部参考电阻应各为 50Ω。 使用 SSTL15_T_DCI 时,要实现 50Ω Thevenin 等效端接 ® 到 VCCO/2,外部参考电阻应为 100Ω,即 (2R)。 Xilinx 要求在 VRP 和 VRN 引脚上使用完全相同的电阻值,以实现预期的 DCI 行为。

- 遵循 DCI I/O Bank规则:

- 使用 DCI 级联时,VREF 必须与同一 I/O bank 或一组 I/O bank 中的所有输入兼容。

- VCCO 必须与同一 I/O bank 中的所有输入和输出兼容。

- 分离端接、受控阻抗驱动器和具有半阻抗的受控阻抗驱动器可以共存于同一组中。

DCI Usage Examples

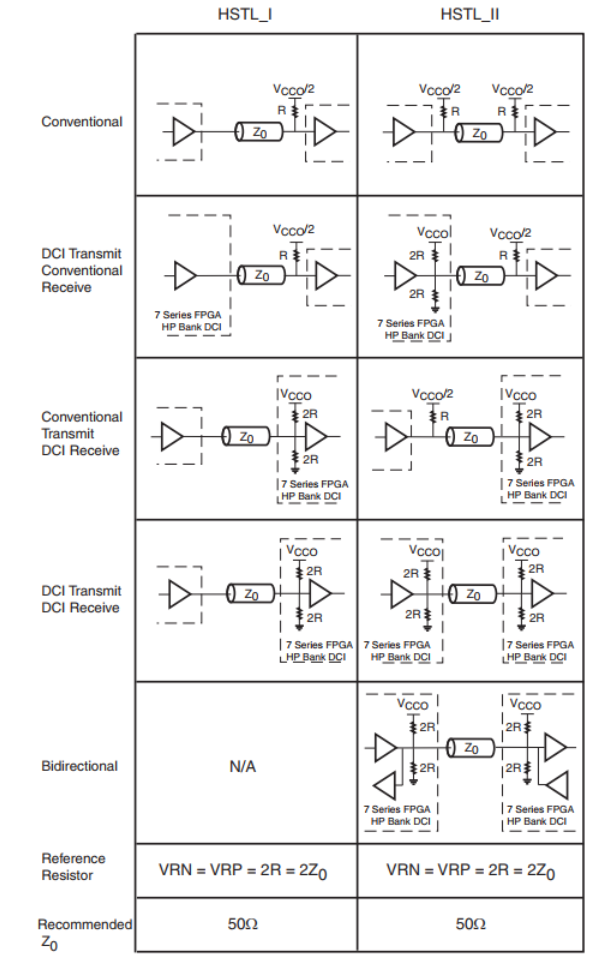

下图提供了说明使用 HSTL_I_DCI 和 HSTL_II_DCI I/O 标准的示例。

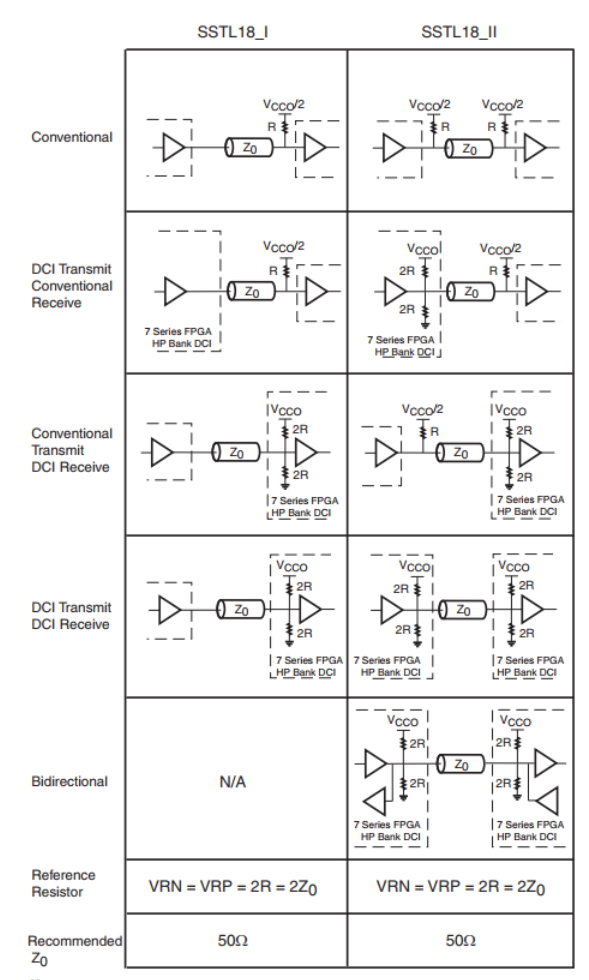

下图提供了说明使用 SSTL18_I_DCI 和 SSTL18_II_DCI I/O 标准的示例。

HR I/O Bank 中未校准的拆分终端 (IN_TERM)

HR I/O bank 有一个可选的片上分离终端特性,与 HP I/O bank 中的三态分离终端 DCI 特性非常相似。 与 HP 组中的三态分离端接 DCI 类似,HR 组中的选项使用两个目标电阻值两倍的内部电阻器创建戴维南等效电路。 一个电阻端接至 VCCO,另一个端接至地,为中点 VCCO/2 提供戴维南等效端接电路。 当输出缓冲器为三态时,输入端和双向引脚上始终存在端接。 然而,这种未经校准的分离式终端选项和三态分离式终端 DCI 之间的一个重要区别是,在使用 DCI 时,该功能不是校准到 VRN 和 VRP 引脚上的外部参考电阻,而是调用没有校准例程的内部电阻来校准补偿温度、过程或电压变化。 此选项的目标戴维南等效电阻值为 40Ω、50Ω 和 60Ω。

与 DCI 终端的另一个区别是如何在设计中调用这种未经校准的终端。 虽然通过将 T_DCI I/O 标准分配给 HP I/O bank 中的 I/O 管脚来调用三态分离终端 DCI 选项,但通过将 IN_TERM 约束分配给 I/O 管脚来调用未校准的分离终端选项 HR I/O bank 中的网络。这可以通过多种方式完成,包括在源 HDL 设计中、在 UCF、NCF 或 XCF 文件中,或在 PlanAhead软件中。

reference

- UG471