热门标签

热门文章

- 1执行'brew update'提示'Permission denied'解决方案_brew upgrade permission denied mac

- 2最新个人简历(通用20篇)_个人简历免费

- 3Java 给视频添加背景音乐 | Java工具_java video audio encoder

- 4关于github双因素验证问题解决方案_two-factor code verification failed. please try ag

- 5ONLYOFFICE 桌面编辑器 8.1 强势来袭:解锁全新PDF编辑、幻灯片优化与本地化体验,立即下载!AI_onlyoffice8.1版本

- 6Baidu Comate 编程的智能化新时代

- 72024年最全微信公众号 接口测试平台 获取自定义菜单教程,2024年最新推荐给大家_微信公众平台接口调试工具自定义菜单

- 8PHP 免费开源 cms 内容管理系统 (07flyCMS)

- 9dell电脑安装Ubuntu系统BIOS设置_dell服务器默认ubuntu操作系统吗

- 10python列表的扩展操作

当前位置: article > 正文

基于FPGA的简单数字钟设计VHDL代码Quartus仿真_24进制计数器vhdl代码

作者:从前慢现在也慢 | 2024-06-17 08:39:02

赞

踩

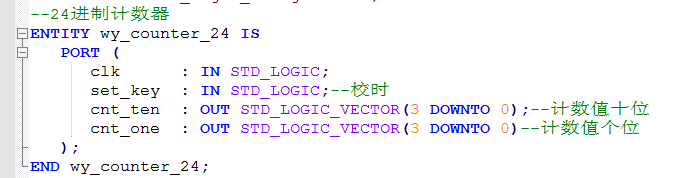

24进制计数器vhdl代码

名称:基于FPGA的简单数字钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

简单数字钟设计

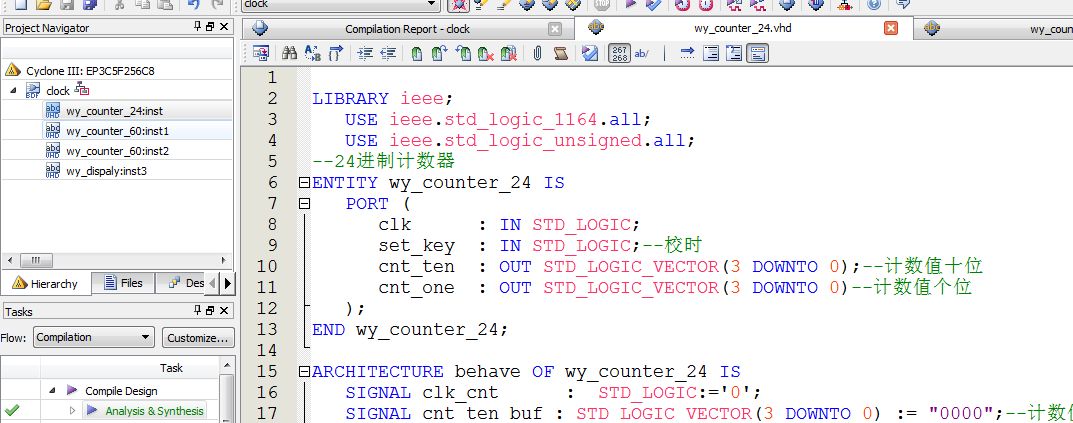

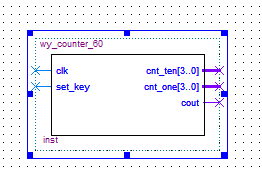

1、设计24进制计数器,可以通过按键调整计数值

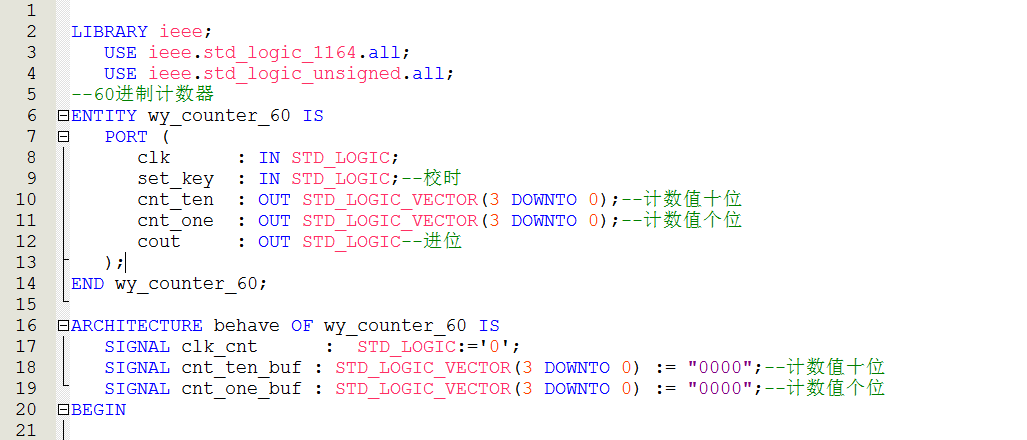

2、设计60进制计数器,可以通过按键调整计数值

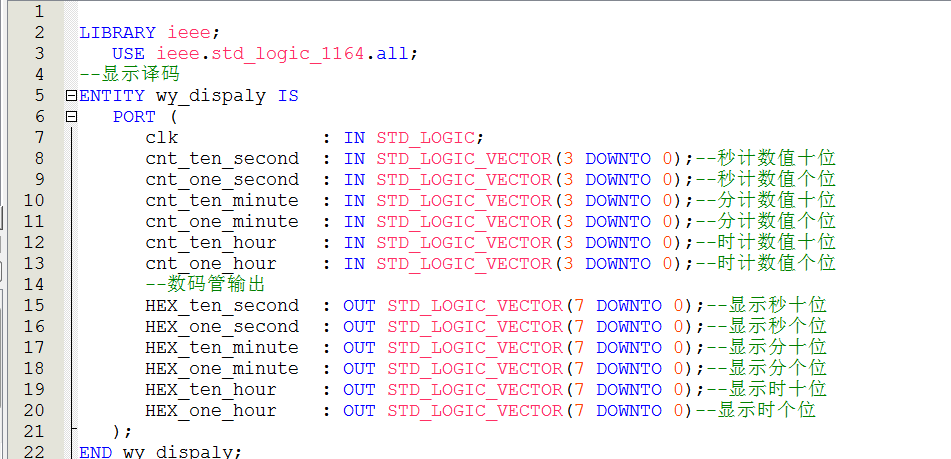

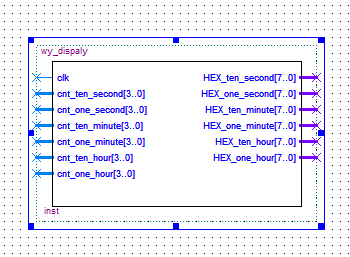

3、设计显示模块

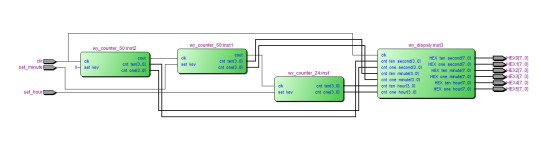

4、将上述模块组成时、分、秒数字钟,可以调时,并显示在数码管

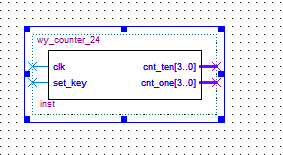

1. 工程文件

2. 程序文件

框图

3. 程序编译

4. RTL图

5. 仿真图

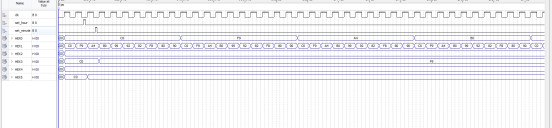

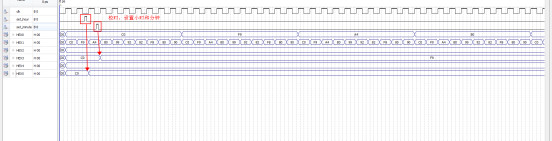

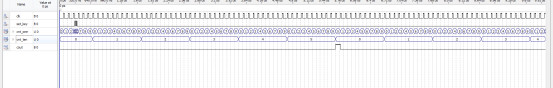

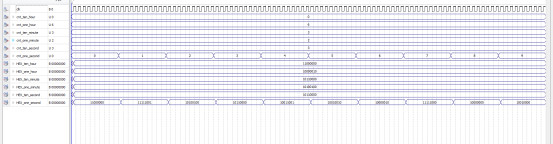

整体仿真图

60进制模块仿真图

24进制模块仿真图

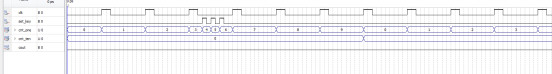

显示模块仿真

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --小时模块--24进制 ENTITY wy_counter_24 IS PORT ( clk : IN STD_LOGIC; set_key : IN STD_LOGIC;--校时 cnt_ten : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--计数值十位 cnt_one : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--计数值个位 ); END wy_counter_24; ARCHITECTURE behave OF wy_counter_24 IS SIGNAL clk_cnt : STD_LOGIC:='0'; SIGNAL cnt_ten_buf : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";--计数值十位 SIGNAL cnt_one_buf : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";--计数值个位 BEGIN --输出 cnt_ten <= cnt_ten_buf; cnt_one <= cnt_one_buf; clk_cnt<=clk OR set_key;--校时和时钟或运算,即校时也可以控制时间 PROCESS (clk_cnt) begin IF (clk_cnt'EVENT AND clk_cnt = '1') THEN--正常计时 IF (cnt_ten_buf = "0010" AND cnt_one_buf = "0011") THEN--23时后变为00 cnt_ten_buf <= "0000"; cnt_one_buf <= "0000"; ELSIF (cnt_ten_buf = "0000" AND cnt_one_buf = "1001") THEN--09变为10 cnt_ten_buf <= "0001"; cnt_one_buf <= "0000"; ELSIF (cnt_ten_buf = "0001" AND cnt_one_buf = "1001") THEN--19变为20 cnt_ten_buf <= "0010"; cnt_one_buf <= "0000"; ELSE--个位累加 cnt_ten_buf <= cnt_ten_buf; cnt_one_buf <= cnt_one_buf + "0001"; END IF; END IF; END PROCESS; END behave;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/730446

推荐阅读

相关标签