- 1fiddler抓取的接口参数,postman接口测试报无响应?

- 2【AI视野·今日CV 计算机视觉论文速览 第244期】Fri, 15 Apr 2022_interpretable vertebral fracture quantification vi

- 3从零手写实现 nginx-20-placeholder 占位符 $

- 4使用react开发dapp应用实战-宠物认领_react 电子宠物

- 5docker-compose部署Flink及Dinky

- 6【Python】Django删除数据迁移记录_python manage.py migrate 清除缓存

- 7ollama部署本地大模型

- 8不要迷恋我,虽然我利用Python来耍植物大战僵尸_zwdzjs怎么修改源代码

- 9素数筛(算法篇)

- 10浅谈四种用Python实现数据可视化的快速简便方法_数据可视化python

笔记:FPGA上实现最小soc系统_quartus 实现fpga soc

赞

踩

笔记:FPGA上实现最小soc系统

软件:quartus2+keil,硬件:JTAG/SW,usb转ttl,fpga下载线,10M50DAF484C7G — fpga max10系列

1.fpga硬件设计

1.1 debug可能出现的问题

1.2 pin脚连接

1.3 tcl文件

1.4 soc电路设计下载到fpga

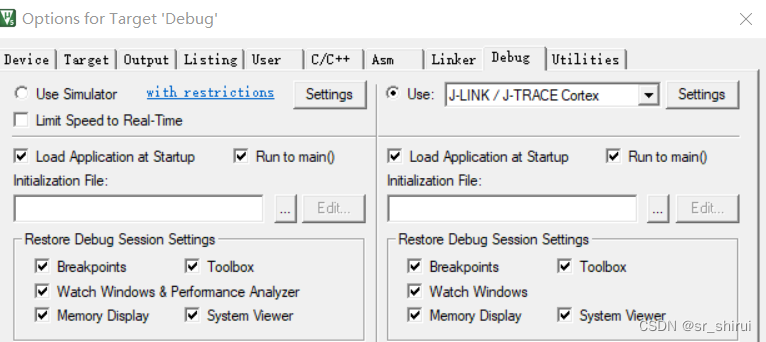

2.软件调试

基于上篇文章min_soc系统软硬件协同仿真,这次我们来把bit流下载到fpga上,让fpga的uart串口打印出hello

1.fpga硬件设计

1.1 debug可能出现的问题

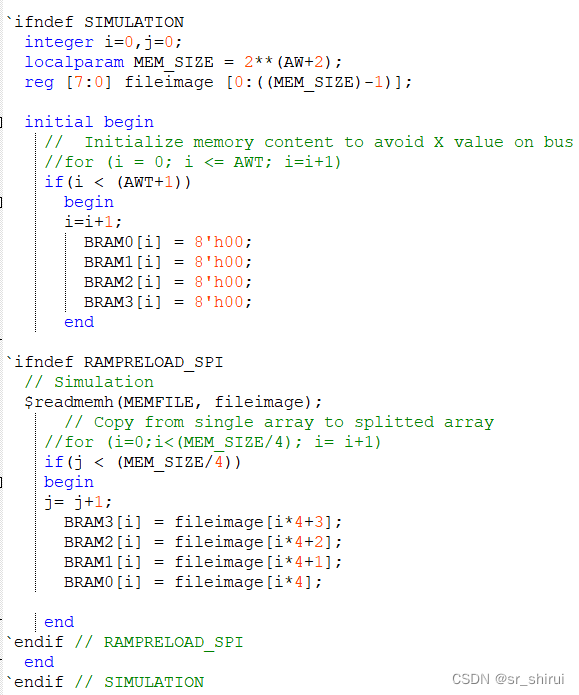

loop must terminate within 5000 iter,在仿真时,有时会出现这样的问题,这是由于for赋值引发的问题,语句改为用if做判断即可,在cmsdk_fpga_sram中,应改为如下定义simulation。

1.2 pin脚连接

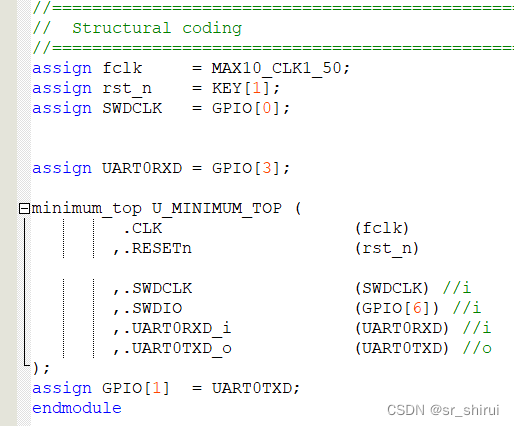

基于上次的最小系统,我们在top文件中定义了fpga 的pin脚连接,(在这里可以看到管脚之间的连接,配合fpga的用户手册即可对各管脚的连接一通百通)

如图,这是top文件对管脚连接的定义,让我们看看,即可以举例几个关进啊管脚,sw调试仿真需至少配置SWDIO/SWDCLK/GND连接在JTAG/SW调试口与fpga间,如下图,SWDCLK是与GPIO[0]相连接,只需查用户手册,这个GPIO[0]连接的是哪一个pin口即可。

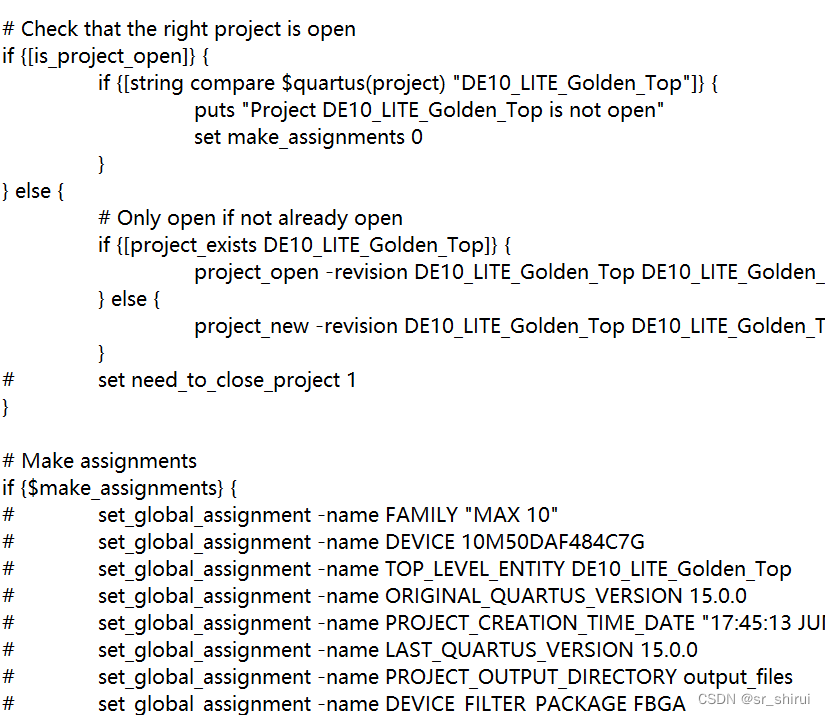

1.3 tcl文件

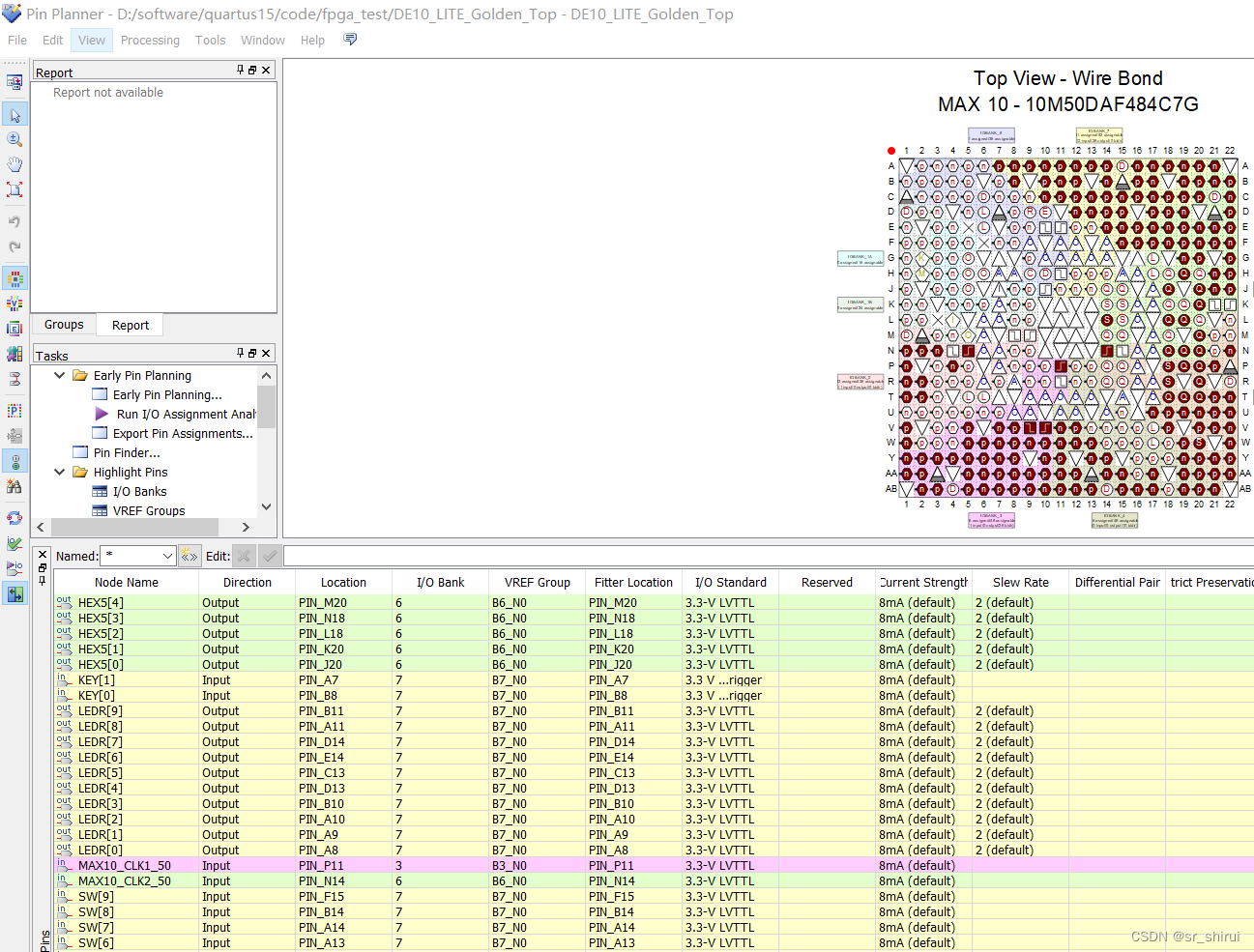

为管脚配置方便起见,我们可以根据fpga用户手册先配置好管脚的连接通过progect -> generate tcl file for project 即可生成自己定义的工程文件的tcl脚本,以后使用时只需在quartus中打开view -> utility windows -> tcl console ,在tcl脚本处,source project_name.tcl 即可配置好管脚

还是tcl脚本方便呐,如上图所示,打开pin planer里,管脚就都已经配置好了。其实可以把建立到仿真的整个过程都写成tcl脚本的,但是这样的话如果程序跑飞,在终端界面看着不明显,也很难定位程序错误位置,调试麻烦。

1.4 soc电路设计下载到fpga

都配置好后直接compile design,生成的文件中会有如下两中可下载文件,其中,sof文件下载速度快,但是掉电易失,pof文件下载速度慢,但掉电不易失

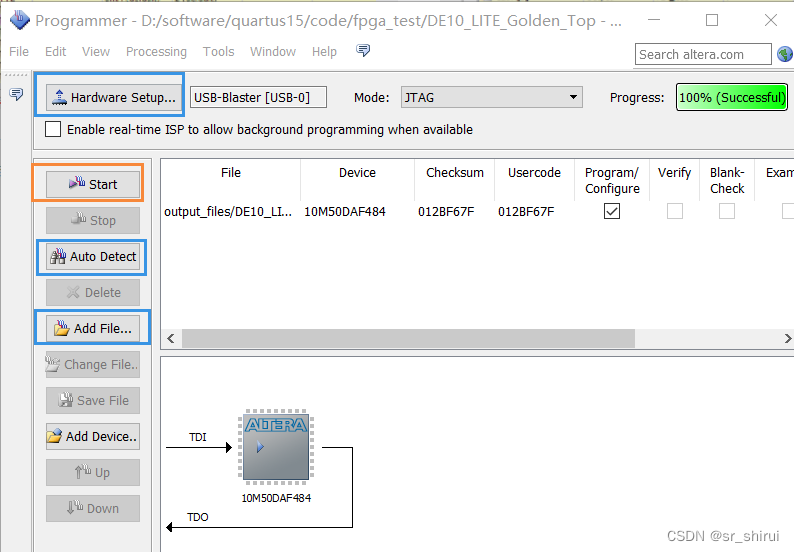

在programmer中只要配置好hardware和file就好,好现在我们已经完成了硬件的程序设计、pin脚连接、程序下载,下面我们要开始在软件上看我们的soc上调试程序能否正确执行。

2.软件调试

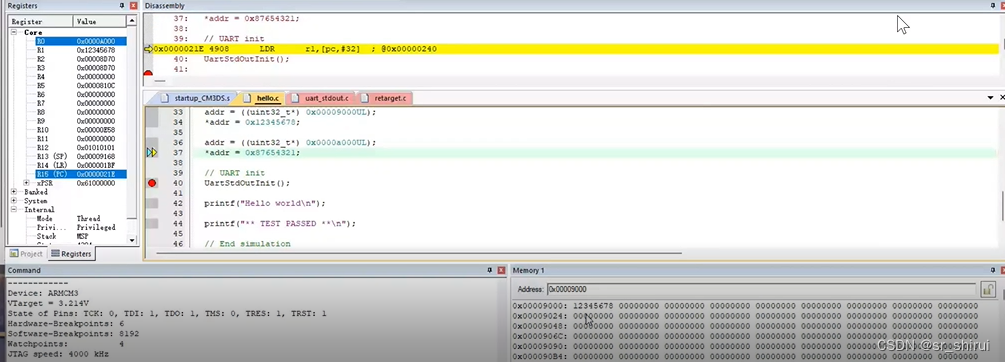

打开keil,依旧是我们上次的 数据插桩 和 uart串口调试打印hello部分

#include "CM3DS_MPS2.h" #include <stdio.h> #include "uart_stdout.h" int main (void) { uint32_t* addr; addr = ((uint32_t*) 0x00009000UL); *addr = 0x12345678; addr = ((uint32_t*) 0x0000a000UL); *addr = 0x87654321; // UART init UartStdOutInit(); printf("Hello world\n"); printf("** TEST PASSED **\n"); // End simulation UartEndSimulation(); return 0; }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

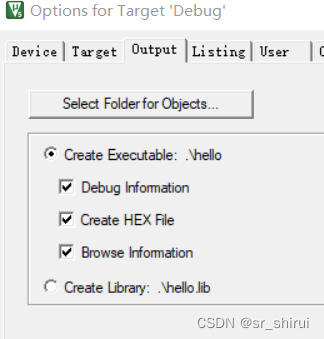

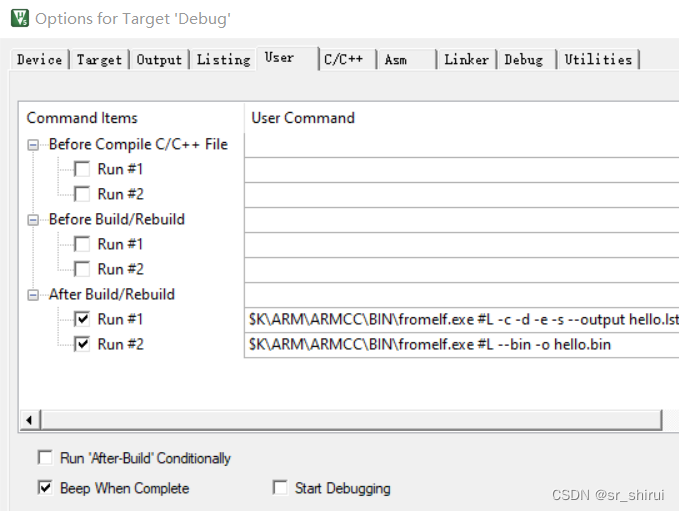

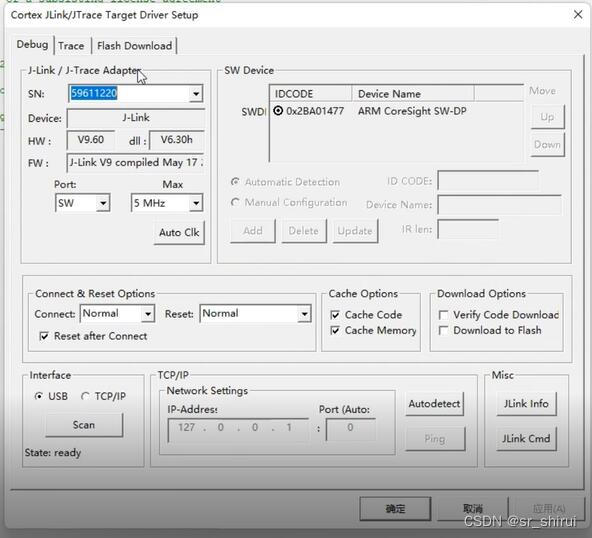

主要还是要先配置好环境啊,

$K\ARM\ARMCC\BIN\fromelf.exe #L -c -d -e -s --output hello.lst

$K\ARM\ARMCC\BIN\fromelf.exe #L --bin -o hello.bin

要看到上面这张图正常时,才说明你连接的是正确的,否则可能会检测不到芯片或者JTAG。

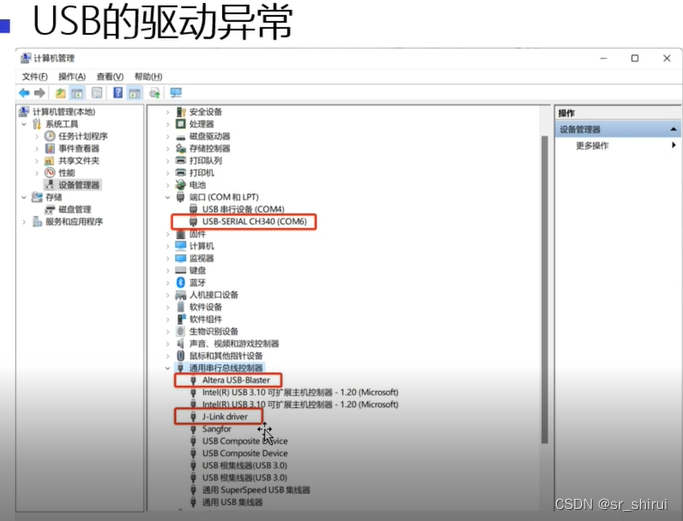

当然这也可能是你没有装好驱动的问题,如图三个端口分别接的是,uart, fpga,jtag调试器。

然后进入keil的调试界面

调出它的寄存器窗口可以看到插桩的数据已经写入。

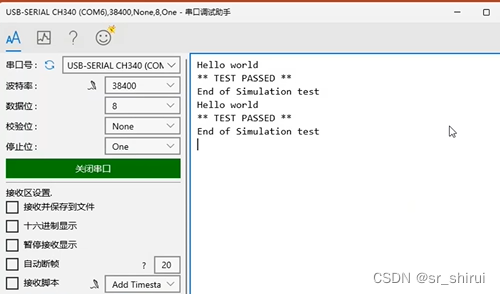

配置好串口调试助手,已经能看到我们的uart打印的语句,到此就完成了我们的最小soc在fpga上实现啦

//---------------------------------------------------------------

可以到我的主页下载最小soc运行的代码,只做学习交流使用